| LABORATORIO ELETTRONICA DIGITALE: |           | 04_08 | Data:  |

|-----------------------------------|-----------|-------|--------|

| Nome                              | SOLUZIONE |       | Esito: |

| Tempo a disposizione:             | 1 ora     |       |        |

## **QUESITO 1**

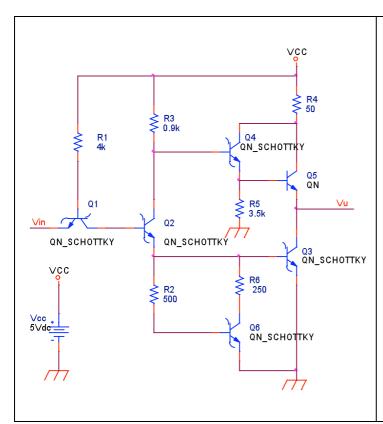

Simulare staticamente e dinamicamente l'inverter TTL-S realizzato in tecnologia "ED", il cui schema circuitale è riportato in figura. Si completi la tabella con i risultati delle opportune simulazione effettuate tenendo conto delle condizioni specificate sotto la tabella stessa.

| $V_{IL}$          | 938 mV   |

|-------------------|----------|

| $V_{IH}$          | 1,352 V  |

| $V_{OL}$          | 338 mV   |

| $V_{OH}$          | 3,569 V  |

| I <sub>IL</sub> * | -966 μA  |

| $I_{IH}^{\#}$     | 1,5 nA   |

| $t_{pHL}^{\%}$    | 1,366 ns |

| $t_{pLH}^{\%}$    | 1,888 ns |

<sup>\*</sup> Valutato con ingresso pari a 0,1 V.

<sup>&</sup>lt;sup>#</sup> Valutato con ingresso pari a 3,6 V.

Walutati facendo variare il segnale d'ingresso tra 0,1 V e 3,6 V con tempi di salita e discesa pari a 500 ps e collegando in uscita alla porta una capacità di valore 1 pF e una resistenza di valore 10 kΩ.

## **QUESITO 2**

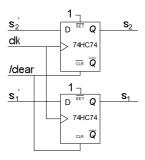

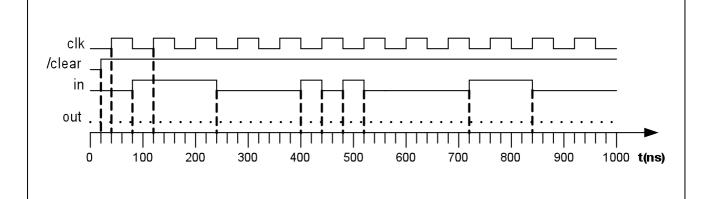

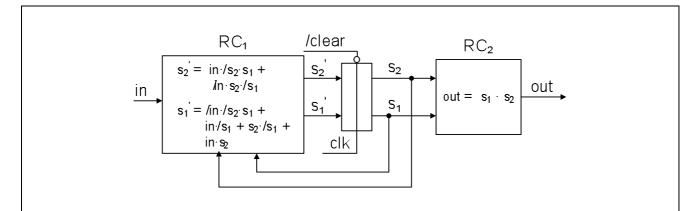

Realizzare usando porte della famiglia logica HC la rete sequenziale sincrona di Moore rappresentata in figura. Si riporti lo schema elettrico del circuito realizzato. Simulare poi il circuito realizzato utilizzando per gli ingressi le forme d'onda specificate di seguito e il modello *typical* per i ritardi delle porte logiche. Si richiede di disegnare la forma d'onda relativa all'uscita quotando gli istanti in cui si presenta un cambiamento di stato.

Schema elettrico del circuito realizzato.