| LABORATORIO ELETTRONICA | Digitale: | 03_09 | Data:  | 30/06/2009 |

|-------------------------|-----------|-------|--------|------------|

| Nome                    | SOLUZIONE |       | Esito: |            |

| Tempo a disposizione:   | 1 ora     |       |        |            |

## **TEMA**

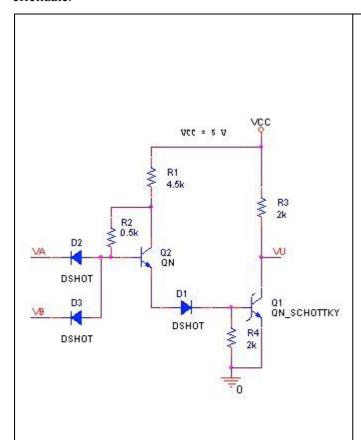

Si consideri la porta NAND realizzata in tecnologia bipolare "ED", il cui schema elettrico è riportato nella figura più in basso. Si richiede di completare la scheda con i risultati ottenuti dalle opportune simulazioni effettuate.

a. Analisi statica a vuoto: si faccia variare l'ingresso A, mantenendo l'ingresso B sul livello neutro della porta. Si valuti la potenza dissipata staticamente *PDS* e le correnti *I<sub>IL</sub>*, *I<sub>IH</sub>* considerando 0.4 V e 5 V come livelli rispettivamente basso e alto in ingresso.

| $V_{I\!L}$                         | 1.319 V  |

|------------------------------------|----------|

| $V_{I\!H}$                         | 1.511 V  |

| $V_{OL}$                           | 410 mV   |

| $V_{OH}$                           | 4.999 V  |

| PDS                                | 9.576 mW |

| $I_{IL}$ @ $(V_A = 0.4 \text{ V})$ | -841 μA  |

| $I_{IH}$ @ $(V_A = 5 \text{ V})$   | 303 pA   |

|                                    |          |

b. Analisi statica a carico: si valuti il FAN—OUT della porta, garantendo un margine di rumore residuo pari a 0.5 V. Si considerino in ingresso alla porta pilota i livelli elettrici 0.4 V e 5 V e si modelli l'ingresso delle porte pilotate con un generatore di corrente di valore  $I_{IL}$  e  $I_{IH}$  sul livello basso e su quello alto, rispettivamente.

| FAN-OUT | 12 |

|---------|----|

|         |    |

c. Analisi dinamica: valutare i tempi di transizione dell'uscita dal livello alto a quello basso e viceversa,  $t_{HL}$  e  $t_{LH}$ . Si colleghi una capacità  $C_L = 0.5$  pF in uscita e si faccia variare il segnale d'ingresso A tra 0.4 V e 5 V con tempi di salita e discesa uguali e pari a 1 ns, mantenendo l'altro ingresso sul livello neutro della porta.

| $t_{HL} (C_L = 0.5 \text{ pF})$ | 1.217 ns |

|---------------------------------|----------|

| $t_{LH} (C_L = 0.5 \text{ pF})$ | 2.892 ns |

d. Dimensionare le resistenze  $R_1$  e  $R_2$ , mantenendo la loro somma costante e pari a 5 k $\Omega$ , in modo tale che il FAN-OUT, valutato come al punto b, risulti uguale a 20.

| 3.675 kΩ |

|----------|

|          |