# SISTEMI EMBEDDED AA 2012/2013

SOPC DE2 Basic Computer

Parallel port

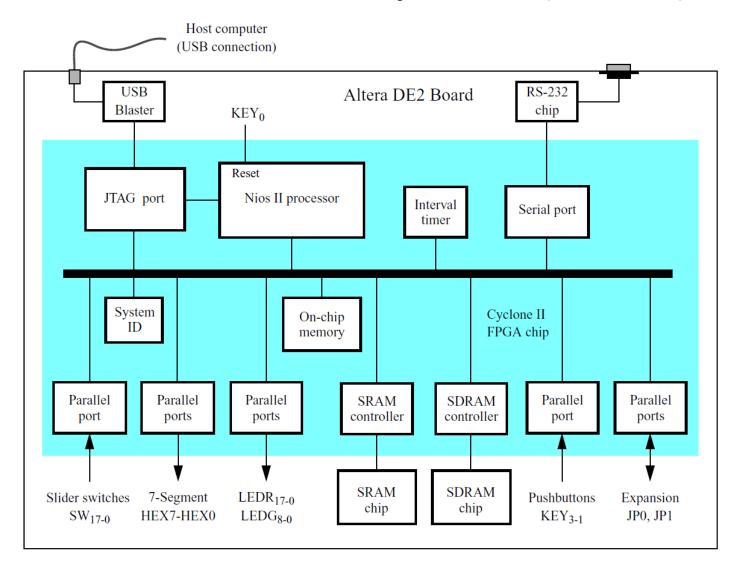

#### **DE2 Basic Computer**

- Nios II configuration provided by Altera University Program

- Core: Nios II/e

- Memory: SDRAM, RAM, On-chip memory

- Parallel ports: Red\_LEDs, Green\_LEDs,

HEX3\_HEX0, HEX7\_HEX4, Slider\_switches,

Pushbuttons, etc.

- Other peripherals: JTAG UART, Serial\_port,

Interval\_timer, sysid

### DE2 Basic Computer (cont.)

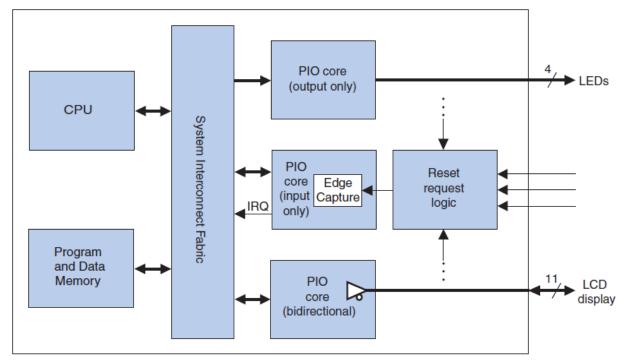

### Parallel port (1)

- Interface for general purpose I/O

- Based on Altera's PIO core customized for DE-series boards

- Controlling LEDs, acquiring data from Switches, etc.

### Parallel port (2)

- 4 32-bit memory-mapped registers

- n actual number of I/O pins

| Table 2. Parallel Port register map |               |        |            |                                                   |

|-------------------------------------|---------------|--------|------------|---------------------------------------------------|

| Offset in bytes                     | Register name |        | Read/Write | Bits $(n-1)0$                                     |

| 0                                   | data          | Input  | R          | Data value currently on Parallel Port inputs.     |

|                                     |               | Output | W          | New value to drive on Parallel Port outputs.      |

| 4                                   | direction     |        | R/W        | Individual direction control for each I/O port.   |

|                                     |               |        |            | A value of 0 sets the direction to input; 1 sets  |

|                                     |               |        |            | the direction to output.                          |

| 8                                   | interruptmask |        | R/W        | IRQ enable/disable for each input port. Set-      |

|                                     |               |        |            | ting a bit to 1 enables interrupts for the corre- |

|                                     |               |        |            | sponding port.                                    |

| 12                                  | edgecapture   |        | R/W        | Edge detection for each input port.               |

## Parallel port (3)

Managing PIO in C program:

Use of pointers to int initialized with PIO base memory address (we'll learn soon other ways!) **Red LEDS** 0x10000000 0x10000000 Red LEDs ptr 0x1000000C Slider switches 0x10000040 0x10000040 Slider switches ptr 0x1000004C

### Parallel port (4)

- Why volatile attribute?

- I/O registers may change even if the program does not modify them!

- The peripheral hardware may modify their contents

- volatile say to the compiler do not make any optimization to the code involving an object declared with the volatile attribute

### Parallel port (5)

Reading/Writing I/O registers:

```

*red_LED_ptr = *Slider_switches_ptr;

```

- Let's start our first program with Nios II

- Control each DE2 red LED through the corresponding slider switch (LEDR<sub>i</sub> = SW<sub>i</sub>)

- To go on:

- Display the status of (SW<sub>15</sub>-SW<sub>0</sub>) on HEX3\_HEX0 as a hexadecimal number

#### References

- Altera "Basic Computer System for the Altera DE2 Board"

- Altera "Parallel Port for Altera DE-Series Boards"