#### SISTEMI EMBEDDED

System Interconnect Fabric Avalon-ST: Streaming Interface Video out: Pixel Buffer DMA component

Federico Baronti

Last version: 20160503

#### **Avalon Streaming Interface**

- Low latency, high throughput, unidirectional point-to-point (from a *source* to a *sink* interface) data transfer (stream)

- Support for complex protocols:

- <u>Packet</u> transfers with packets interleaved across multiple channels

- Sideband (from *source* to *sink*) signalling of channels, errors, start and end of packets

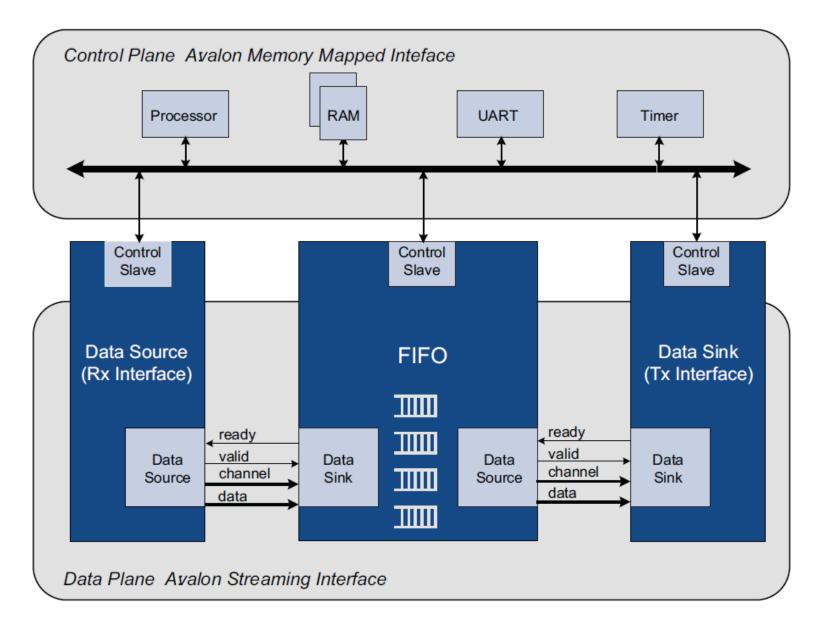

#### Example: Avalon-MM and Avalon-ST

## Some terminology

- Symbol: A symbol is the smallest unit of data. For most packet interfaces, a symbol is a byte. One or more symbols make up the single unit of data transferred in a cycle or a beat

- **Beat**: A single cycle transfer between a source and a sink interface consisting of one or more symbols

- **Channel**: A channel is a physical or logical path or link through which information passes between two ports

- **Packet**: A packet is an aggregation of data and control info that are transmitted together

- A packet may contain a header to help routers and other network devices direct the packet to the correct destination

- The packet format is defined by the application, not by the Avalon specification

# Avalon-ST Interface Signal Roles (1)

| Signal Role         | Signal Role Width Direction |                                                                         | Description                                                                                                                                                                                                                                                         |  |  |  |

|---------------------|-----------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Fundamental Signals |                             |                                                                         |                                                                                                                                                                                                                                                                     |  |  |  |

|                     |                             | Source $\rightarrow$                                                    | The channel number for data being transferred on the current cycle.                                                                                                                                                                                                 |  |  |  |

| channel 1-128       |                             | Sink                                                                    | If an interface supports the channel signal, it must also define the maxChannel parameter.                                                                                                                                                                          |  |  |  |

|                     | 4 4000                      | $\begin{array}{l} \text{Source} \rightarrow \\ \text{Sink} \end{array}$ | The data signal from the source to the sink, typically carries the bulk of the information being transferred.                                                                                                                                                       |  |  |  |

| data 1-4096         | 1-4090                      |                                                                         | The contents and format of the data signal is further defined by parameters.                                                                                                                                                                                        |  |  |  |

| error               | 1–256                       | Source $\rightarrow$ Sink                                               | A bit mask used to mark errors affecting the data being transferred in the current cycle. A single bit in error is used for each of the errors recognized by the component, as defined by the errorDescriptor property.                                             |  |  |  |

| ready               | ceady 1                     |                                                                         | Asserted high to indicate that the sink can accept data. ready is asserted<br>by the sink on cycle <i><n></n></i> to mark cycle <i><n +<="" i=""> readyLatency<i>&gt;</i> as a ready<br/>cycle, during which the source may assert valid and transfer data.</n></i> |  |  |  |

|                     |                             | Source                                                                  | Sources without a ready input cannot be backpressured, and sinks without a ready output never need to backpressure.                                                                                                                                                 |  |  |  |

| valid               | 1                           | Source →<br>Sink                                                        | Asserted by the source to qualify all other source to sink signals. On ready cycles where valid is asserted, the data bus and other source to sink signals are sampled by the sink, and on other cycles are ignored.                                                |  |  |  |

|                     | I                           |                                                                         | Sources without a valid output implicitly provide valid data on every cycle that they are not being backpressured, and sinks without a valid input expect valid data on every cycle that they are not backpressuring.                                               |  |  |  |

# Avalon-ST Interface Signal Roles (2)

| Signal Role   | Width                   | Direction                                                               | Description                                                                                                                                                                                                                                            |  |  |  |  |

|---------------|-------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|               | Packet Transfer Signals |                                                                         |                                                                                                                                                                                                                                                        |  |  |  |  |

| empty         | 1–8                     | $\begin{array}{l} \text{Source} \rightarrow \\ \text{Sink} \end{array}$ | Indicates the number of symbols that are empty during cycles that contain<br>the end of a packet. The empty signal is not used on interfaces where there<br>is one symbol per beat. If endofpacket is not asserted, this signal is not<br>interpreted. |  |  |  |  |

| endofpacket   | 1                       | $\begin{array}{c} \text{Source} \rightarrow \\ \text{Sink} \end{array}$ | Asserted by the source to mark the end of a packet.                                                                                                                                                                                                    |  |  |  |  |

| startofpacket | 1                       | $\begin{array}{c} \text{Source} \rightarrow \\ \text{Sink} \end{array}$ | Asserted by the source to mark the beginning of a packet.                                                                                                                                                                                              |  |  |  |  |

- All transfers of an Avalon-ST connection <u>are synchronous with the rising</u> <u>edge of the associated clock signal</u>

- All outputs from a source interface to a sink interface, including the data, channel, and error signals, must be registered on the rising edge of clock

- Inputs to a sink interface do not have to be registered

- Registering signals only at the source provides for high frequency operation while eliminating back-to-back registers with no intervening logic

## **Avalon-ST Interface Properties**

| Property Name                  | Default<br>Value | Legal Values         | Description                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| symbolsPerBeat                 | 1                | 1–512                | The number of symbols that are transferred on every valid cycle.                                                                                                                                                                                                                                                                                                                |

| associatedClock                | 1                | a clock<br>interface | The name of the Avalon Clock interface to which this Avalon-ST interface is synchronous.                                                                                                                                                                                                                                                                                        |

| associatedReset                | 1                | a reset<br>interface | The name of the Avalon Reset interface to which this Avalon-ST interface is synchronous.                                                                                                                                                                                                                                                                                        |

| dataBitsPerSymbol              | 8                | 1–512                | Defines the number of bits per symbol. For example,<br>byte-oriented interfaces have 8-bit symbols. This value is not<br>restricted to be a power of 2.                                                                                                                                                                                                                         |

| errorDescriptor                | 0                | list of strings      | A list of words that describe the error associated with each bit<br>of the error signal. The length of the list must be the same as<br>the number of bits in the error signal, and the first word in the<br>list applies to the highest order bit. For example, "crc,<br>overflow" means that bit[1] of error indicates a CRC error,<br>and bit[0] indicates an overflow error. |

| firstSymbolInHigh<br>OrderBits | false            | true, false          | When true, the high-order symbol is driven to the MSB of the data interface. The highest-order symbol is labelled $DO$ in this specification.                                                                                                                                                                                                                                   |

| maxChannel                     | 0                | 0–255                | The maximum number of channels that a data interface can support.                                                                                                                                                                                                                                                                                                               |

| readyLatency                   | 0                | 0–8                  | Defines the relationship between assertion and deassertion of<br>the ready signal, and cycles which are considered to be ready<br>for data transfer, separately for each interface.                                                                                                                                                                                             |

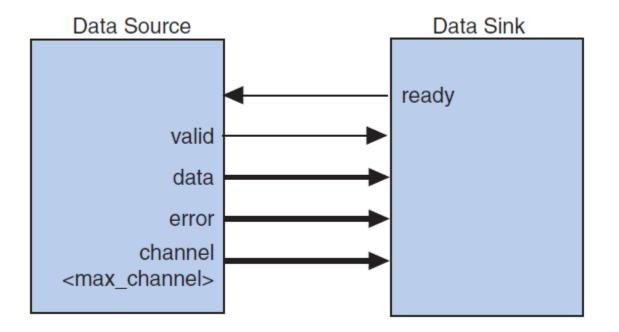

#### Example of a Source-Sink connection

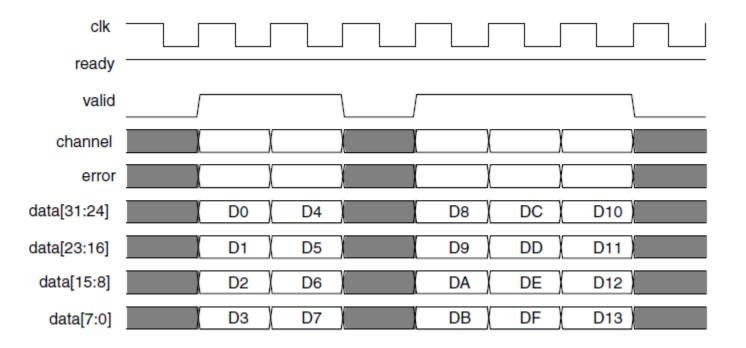

#### Data layout

<u>Example</u>: data width = 32 bits; dataBitsPerSymbol = 8 firstSymbolInHighOrderBits = true

| 31 24    | 23 16    | 15 8     | 7 0      |

|----------|----------|----------|----------|

| Symbol 0 | Symbol 1 | Symbol 2 | Symbol 3 |

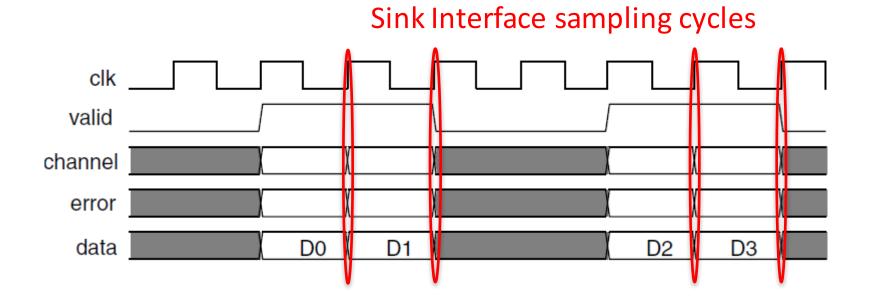

#### Data Transfer without Backpressure

- When the source interface wants to send data, it drives the *data* and the optional *channel* and *error* signals and asserts *valid*

- The sink interface samples these signals on the rising edge of the reference clock when *valid* is asserted

# Data Transfer with Backpressure (1)

- The sink indicates to the source that it is ready for an active cycle by asserting *ready* for a single clock cycle. Cycles during which the sink is ready for data are called ready cycles

- During a ready cycle, the source may assert valid and provide data to the sink. If it has no data to send, it deasserts valid and can drive data to any value

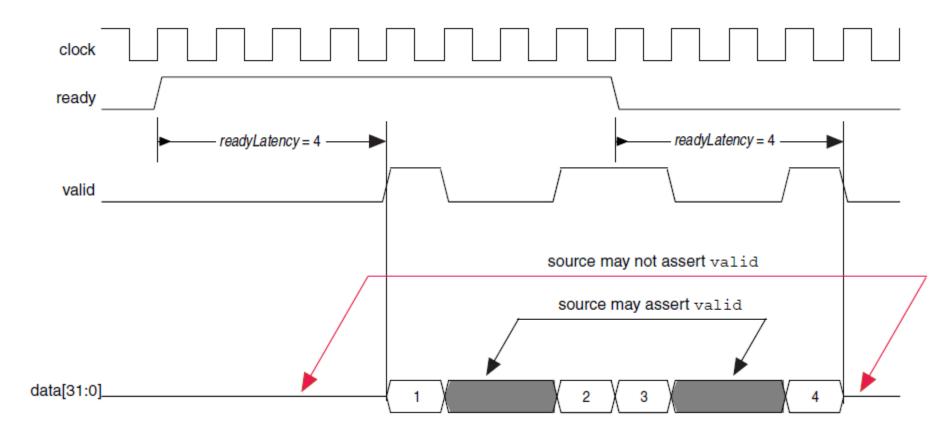

- Each interface that supports backpressure defines the *readyLatency* parameter to indicate the number of cycles from the time that *ready* is asserted until valid data can be driven

- If *readyLatency* has a nonzero value, the source interface must consider cycle

<n + readyLatency> to be a ready cycle if *ready* is asserted on cycle <n>

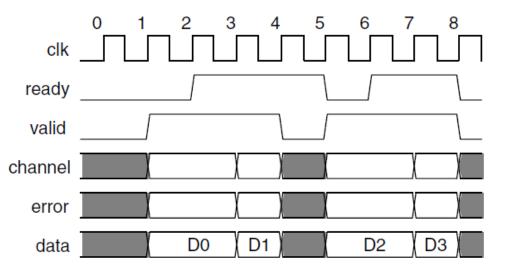

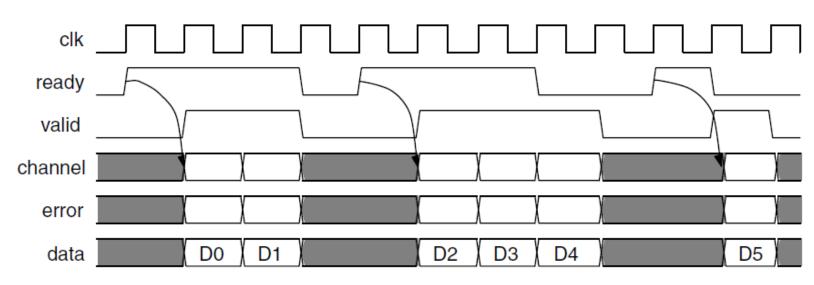

- When *readyLatency* = 0, data is transferred only when ready and valid are asserted on the same cycle. In this mode of operation, the source does not receive the sink's ready signal before it begins sending valid data. The source provides the data and asserts valid whenever it can and waits for the sink to capture the data and assert *ready*. The source can change the data it is providing at any time. The sink only captures input data from the source when *ready* and *valid* are both asserted

- When readyLatency >= 1, the sink asserts ready before the ready cycle itself. The source can respond during the appropriate cycle by asserting valid. It may not assert valid during a cycle that is not a ready cycle

#### Data Transfer with Backpressure (2)

• readyLatency = 4

## Data Transfer with Backpressure (3)

readyLatency = 0

readyLatency = 1

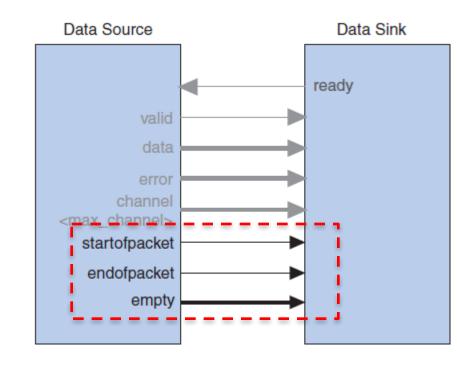

# Packet Data Transfer (1)

- Three additional signals:

- startofpacket, endofpacket, empty

- Both source and sink interfaces must include these additional signals

- No automatic adaptation (by system interconnect fabric)

# Packet Data Transfer (2)

- *startofpacket* is required by all the interfaces supporting packet transfers and marks the active cycle containing the start of the packet. This signal is only interpreted when *valid* is asserted

- *endofpacket* is required by all interfaces supporting packet transfer and marks the active cycle containing the end of the packet. This signal is only interpreted when *valid* is asserted.

- *empty* is optional and indicates the number of symbols that are empty during the cycles that mark the end of a packet. The sink only checks the value of the empty during active cycles that have *endofpacket* asserted

- The *empty* symbols are always the last symbols in data, those carried by the low-order bits when *firstSymbolInHighOrderBits* = true

- The empty signal is required on all packet interfaces whose data signal carries more than one symbol of data and have a variable length packet format

- The size of the empty signal in bits is ceiling(log<sub>2</sub>(<symbols per cycle>))

# Packet Data Transfer (3)

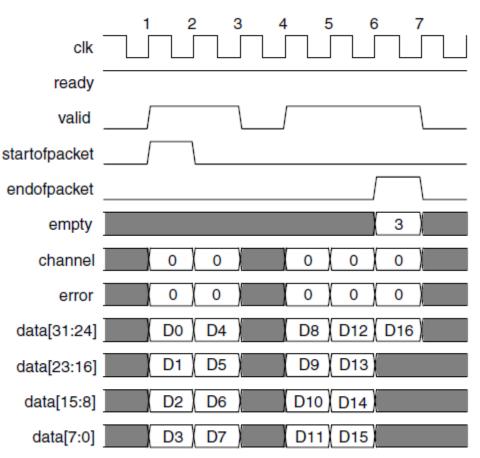

- Transfer of a 17-byte packet (*readyLatency* = 0)

- Data transfer occurs on cycles 2, 3, 5, 6, and 7, when both *ready* and *valid* are asserted

- During cycle 1, startofpacket is asserted, and the first 4 bytes of packet are transferred

- During cycle 6, endofpacket is asserted, and empty has a value of 3, indicating that this is the end of the packet and that 3 of the 4 symbols are empty

- D16 is transmitted over data[31:24] (*firstSymbolInHighOrderBits* = true)

# **Avalon-ST: Adapters**

- Adapters are configurable Qsys/SOPC Builder components that are part of the streaming interconnect fabric. They are used to connect source and sink interfaces that do not match exactly

- **Qsys** includes the following four adapters:

- Data Format Adapter

- Timing Adapter

- Channel Adapter

- Error Adapter

- If you connect mismatched Avalon-ST sources and sinks in Qsys without inserting adapters, Qsys generates error messages

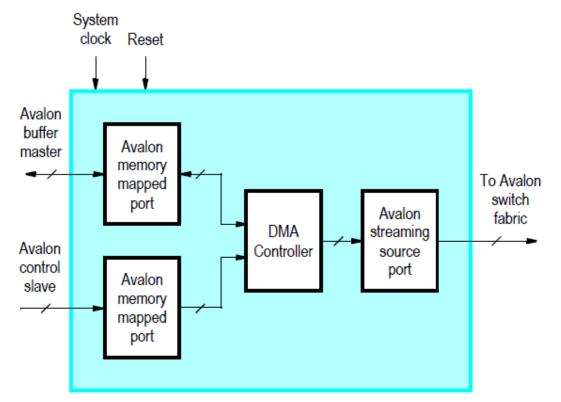

## Example of Avalon-ST Component

- Pixel Buffer DMA Controller

- The DMA controller uses its Avalon-MM master interface to read video frames from an external memory. Then, it sends the video frames out via the Avalon-ST interface. The controller's Avalon-MM slave interface is used to read/write the controller's internal registers by the processor

# Pixel Buffer DMA Controller (1)

• Avalon-MM Slave interface:

| Table 4. Pixel Buffer register map        |      |          |      |                                 |      |     |    |   |    |   |   |

|-------------------------------------------|------|----------|------|---------------------------------|------|-----|----|---|----|---|---|

| Offset                                    | R    | Register | R/W  | Bit Description                 |      |     |    |   |    |   |   |

| in bytes                                  |      | Name     | K/ W | 3124                            | 2316 | 158 | 74 | 3 | 2  | 1 | 0 |

| 0                                         | Buf  | fer      | R    | R Buffer's start address        |      |     |    |   |    |   |   |

| 4                                         | Bac  | kBuffer  | R/W  | R/W Back buffer's start address |      |     |    |   |    |   |   |

| 8                                         | Res  | olution  | R    | Y X                             |      |     |    |   |    |   |   |

| 12                                        | Sta  | tus      | R    | m                               | n    | (1) | В  | ( | l) | Α | S |

| Table 5. Status register bits             |      |          |      |                                 |      |     |    |   | •  |   |   |

| Bit num                                   | ıber | Bit name | R/W  | V Description                   |      |     |    |   |    |   |   |

| 31 - 24 m R Width of Y coordinate address |      |          |      |                                 |      |     |    |   |    |   |   |

| 31 - 24 | m | R                                                     | Width of Y coordinate address                   |  |

|---------|---|-------------------------------------------------------|-------------------------------------------------|--|

| 23 - 16 | n | R                                                     | R Width of X coordinate address                 |  |

| 7 - 4   | В | R number of bytes of color: 1 (greyscale, 8-bit color |                                                 |  |

|         |   |                                                       | 2 (9-bit and 16-bit color), 3 (24-bit color) or |  |

|         |   |                                                       | 4 (30-bit and 32-bit color)                     |  |

| 1       | А | R                                                     | Addressing mode: 0 (X,Y), or 1 (consecutive)    |  |

| 0       | S | R                                                     | Swap: 0 when swap is done, else 1               |  |

# Pixel Buffer DMA Controller (1)

- The Buffer register holds the 32-bit address of the start of the memory buffer. This register is read-only, and shows the address of the first pixel of the frame currently being sent out via the Avalon-ST

- The BackBuffer register allows the start address of the frame to be changed under program control

- To change the frame being displayed, the desired frame's start address is first written into the BackBuffer register

- Then, a second write operation is performed on the Buffer register. The value of the data provided in this second write operation is discarded. Instead, it interprets a write to the Buffer register as a request to swap the contents of the Buffer and BackBuffer registers.

- The swap does not occur immediately. Instead, the swap is done after the Pixel Buffer reaches the last pixel associated with the current frame. In the meantime, bit S of the Status register will be set to 1. After the current frame is finished, the swap is performed and bit S is cleared.

# Pixel Buffer DMA Controller (1)

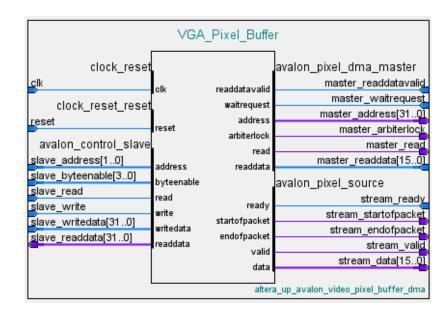

#### module VGA\_Pixel\_Buffer (

// Inputs clk, reset,

slave\_address, slave\_byteenable, slave\_read, slave\_write, slave\_writedata, // Bi-Directional

// Outputs

slave readdata,

master\_address, master\_arbiterlock, master\_read,

master\_readdata, master\_readdatavalid, master\_waitrequest,

stream\_ready, //.... stream\_data, stream\_startofpacket, stream\_endofpacket, stream\_empty, stream\_valid

);

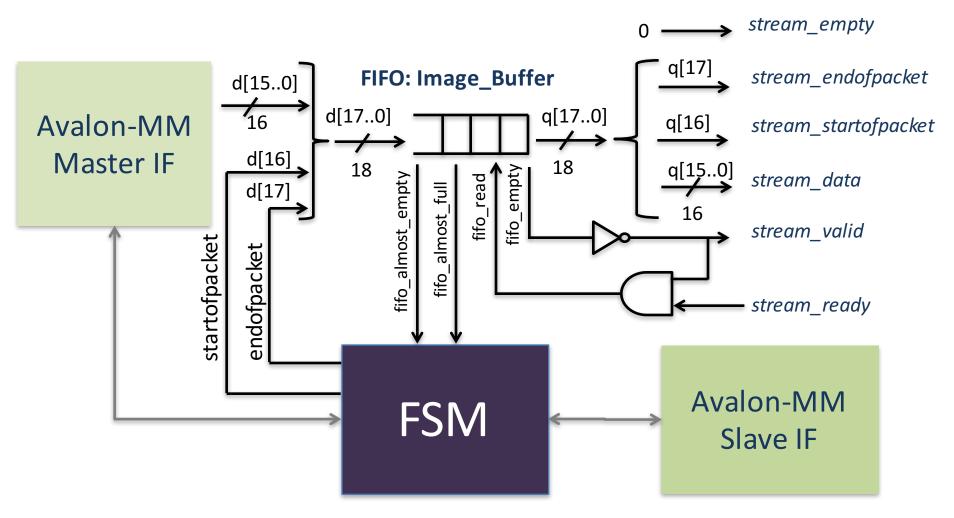

# Pixel Buffer DMA Controller (2)

FSM manages Avalon-MM Master transfers to keep FIFO level between almost-full and almost-empty VGA F

VGA\_Pixel\_Buffer.v

#### References

- Altera, "Avalon Interface Specifications," mnl\_avalon\_spec.pdf

- 5. Avalon Streaming Interfaces