## The CMOS Process

- Planar CMOS process is used up to the 28 nm technology node.

- For later technology nodes, 3D CMOS MOSFETs (FinFETs) are used.

- Planar CMOS processes are still extensively used for analog and mixed-signal ICs.

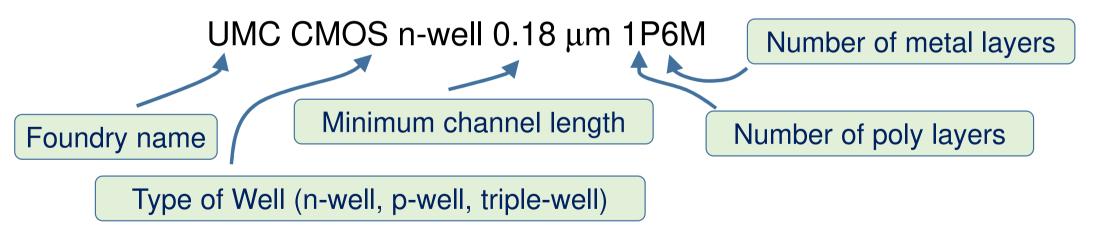

Classification of planar CMOS processes: example

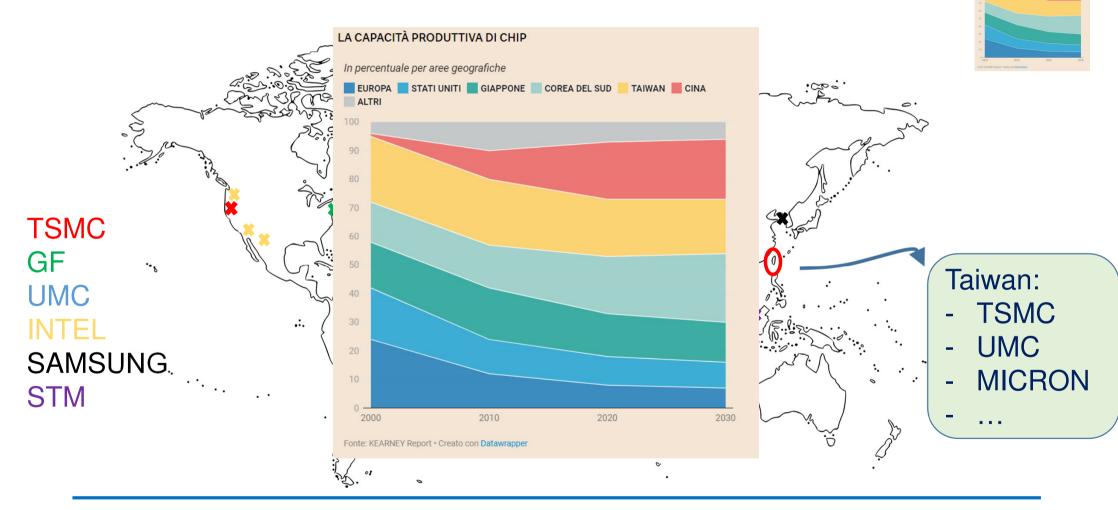

## **Semiconductor Fabrication Plants**

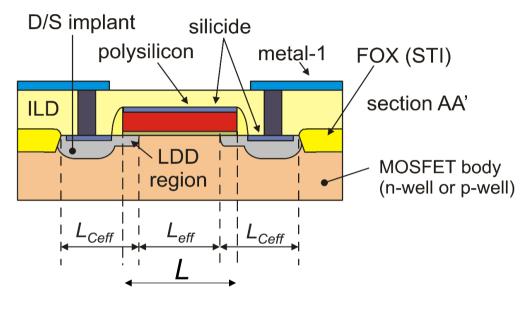

# Technology node

| Year | Node (nm) | Half-pitch<br>(nm) | Gate Length<br>L <sub>eff</sub> (nm) |

|------|-----------|--------------------|--------------------------------------|

| 1997 | 250       | 250                | 250                                  |

| 1999 | 180       | 239                | 140                                  |

| 2001 | 130       | 150                | 65                                   |

| 2003 | 90        | 90                 | 37                                   |

| 2005 | 65        | 90                 | 32                                   |

| 2007 | 45        | 68                 | 38                                   |

| 2009 | 32        | 52                 | 29                                   |

- Until 2000 the technology node represented the minimum channel length (gate length)

- After 180 nm the technology node started representing the half-pitch

- Since 2017 the technology node does not represent any geometrical dimension

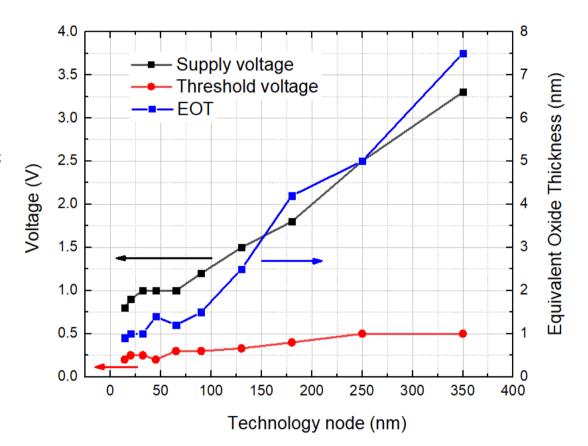

## **Technology Scaling**

- Smaller W and L → Higher transistor density, higher f<sub>T</sub>

- Lower Vdd and Vth → Lower dynamic power consumption, higher static power consumption

- Lower tox → Higher gate leakage (from SiO2/PolySi to High-k materials/metal gate around 45 nm)

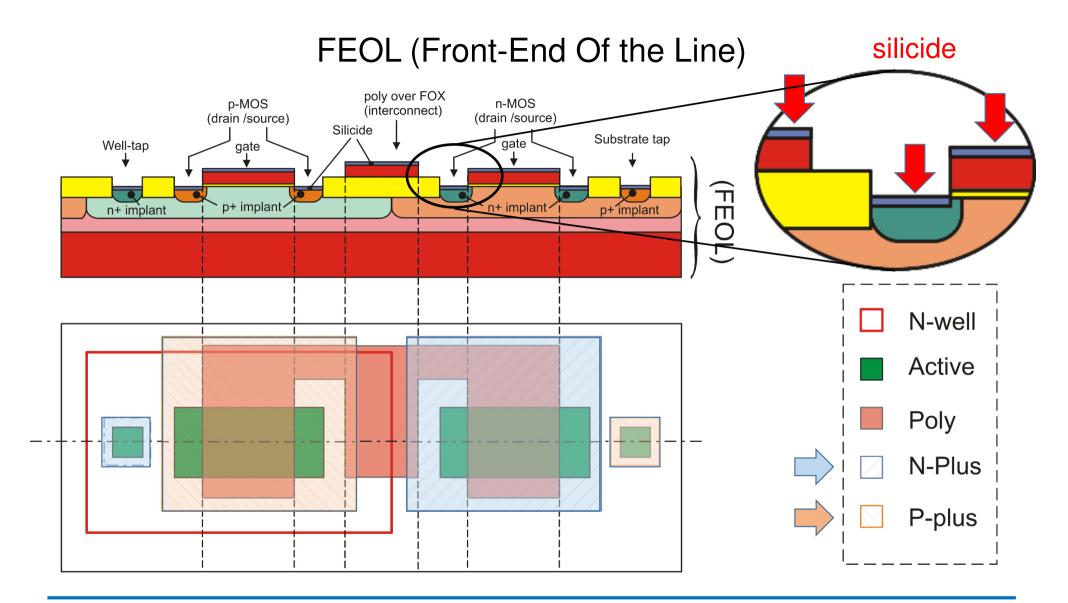

## Simplified designer's view of a CMOS Process

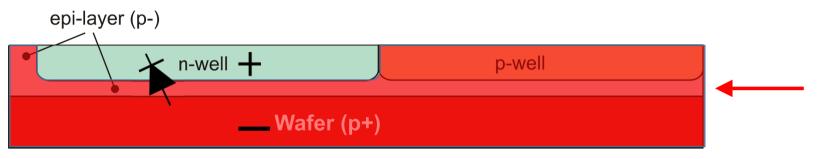

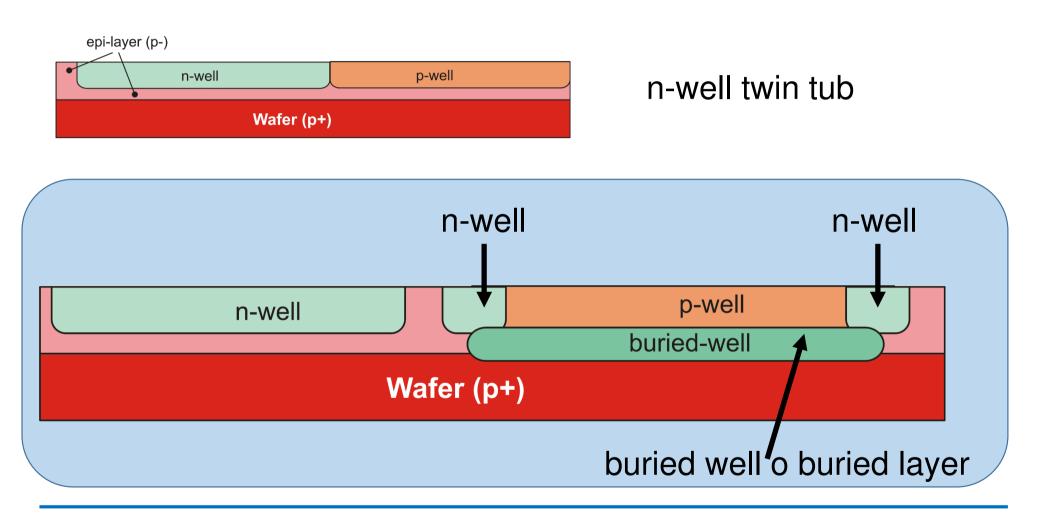

- We are considering a simple n-well (twin-Tub) 1P2M process

- The starting substrate is p-type: all p-wells are shorted together since there are no insulation junctions with the substrate.

- N-wells are insulated from the substrate if the latter is biased at the lowest voltage in the circuit.

- A very lightly doped epitaxial layer is often present on top of a strongly doped wafer. P-wells are necessary to obtain the optimal doping for n-MOSFETS.

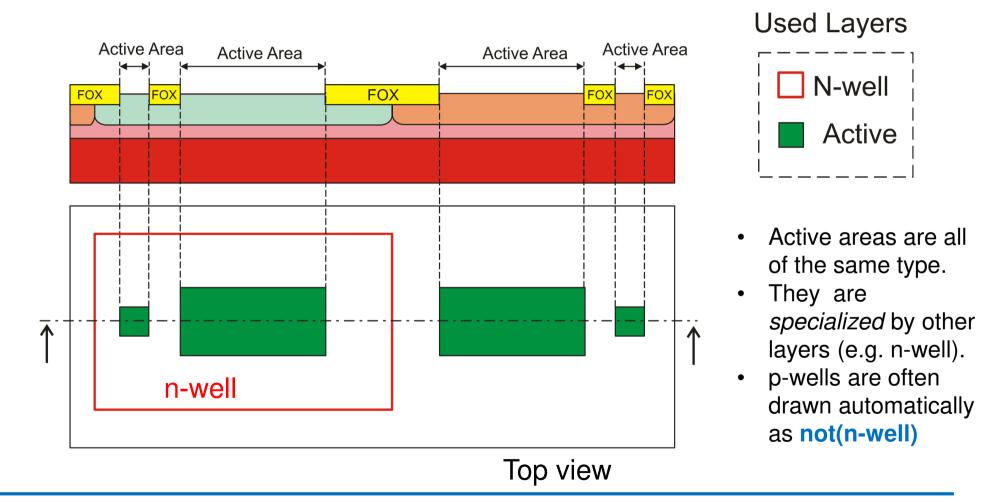

### The active areas

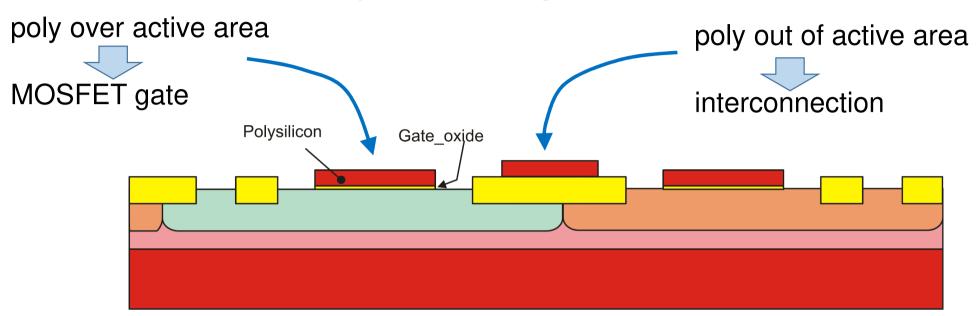

Polysilicon and gate oxide

- The gate (thin) oxide is grown on **all** active areas.

- After that, it is covered by the polysilicon layer

- When the poly is patterned, the gate oxide remains only where polysilicon remains, forming the gate.

- Only one layer (poly) is required to control the final result of this step.

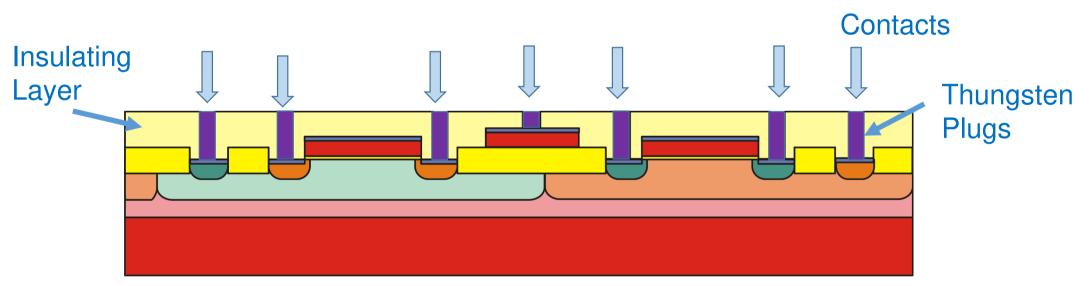

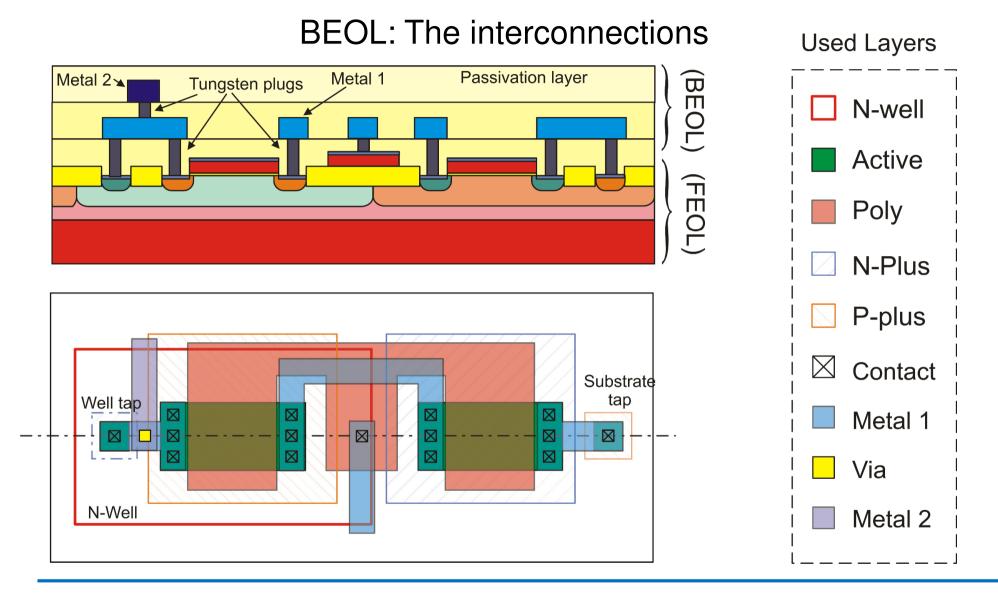

BEOL (Back End Of the Line) - Contacts

- All devices created in the FEOL are covered by an insulating layer and holes are opened only where we want to contact them. These opening are the **CONTACTS**

- Contacts can reach active areas (p+ or n+ doped portions of the substrate) or polysilicon (over the FOX).

- Direct contact of polysilicon over the gates is not allowed

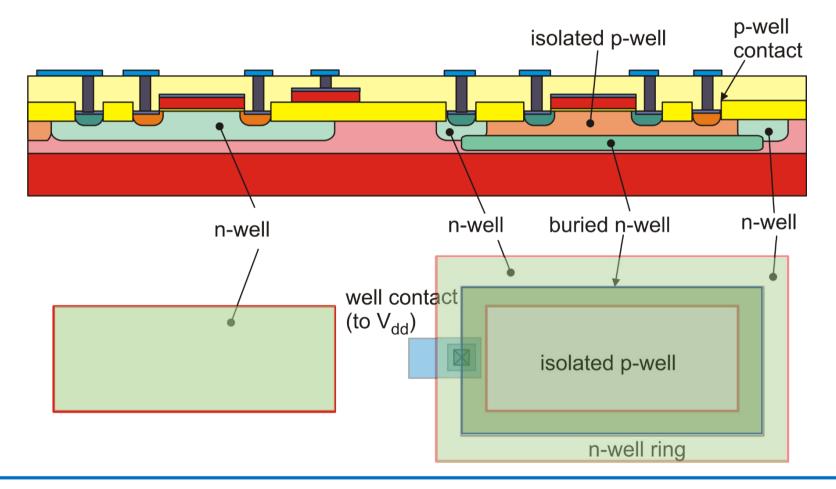

### The Triple Well

### Triple Well: Multiple PWells and NWells at independent voltages

#### Bipolar processes

| Technology               | Available Devices          | Notes                                                                               |

|--------------------------|----------------------------|-------------------------------------------------------------------------------------|

| Bipolar                  | Vertical NPN, Lateral PNP  | Used for precision and/or fast amplifier. <b>Si-Ge</b> versions for RF applications |

| Complementary<br>Bipolar | Vertical NPN, Vertical PNP | <u>or de</u> versions for le appreadons                                             |

| BiFet                    | BJTs and JFETs             | Used for precision / low bias current amplifiers                                    |

## BiCMOS, BCD, SOI

| Technology                   | Available Devices      | Notes                                               |

|------------------------------|------------------------|-----------------------------------------------------|

| BiCMOS                       | CMOS + BJTs            | Mixed Signal ICs<br>High speed digital line drivers |

| BCD                          | Bipolar, CMOS, DMOS    | Smart Power                                         |

| SOI Silicon on<br>Insulator. | As CMOS, BiCMOS or BCD | High Voltage and Rad Hard (e.g. space applications) |

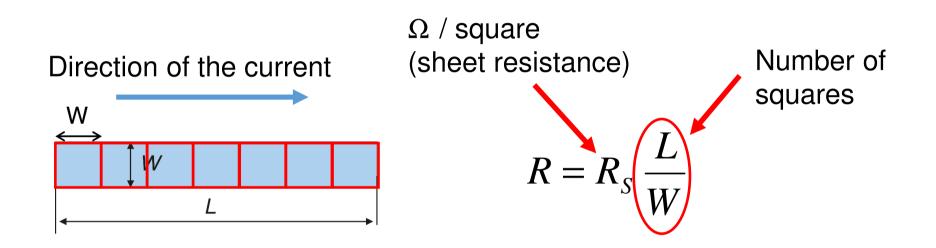

Resistances in planar ICs

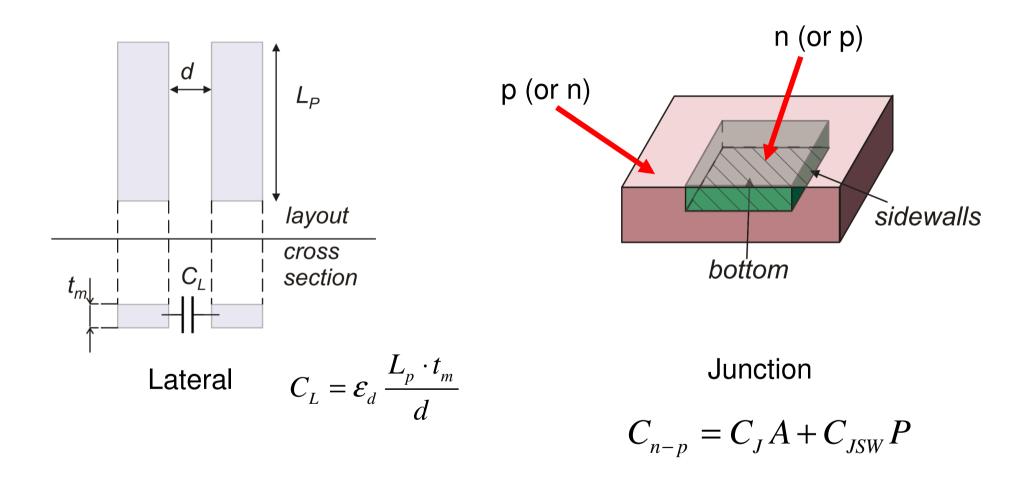

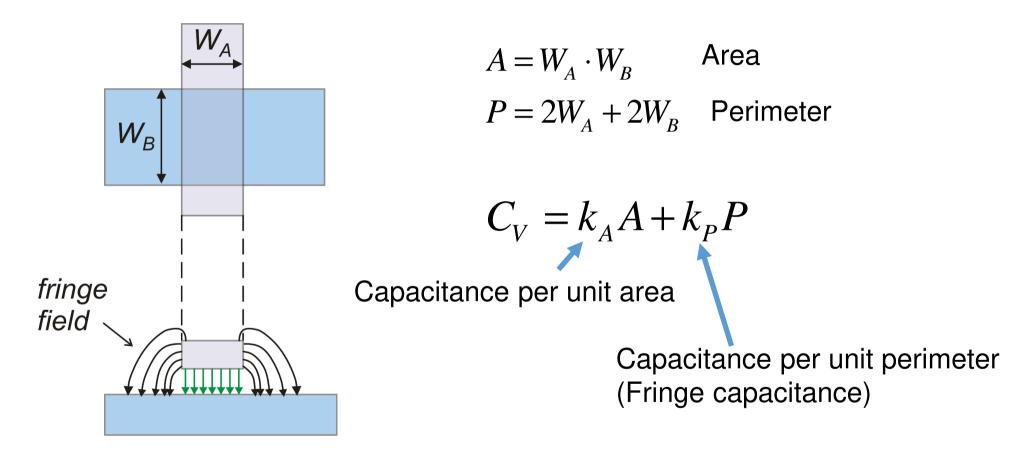

### Vertical and lateral capacitances

#### Lateral and Junction Capacitances