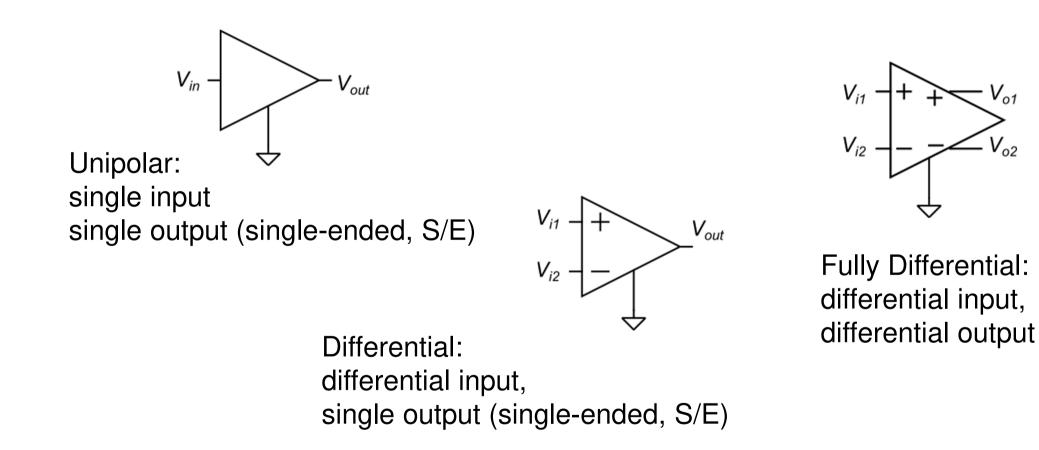

# Voltage amplifiers: number of inputs and outputs

Voltage Amplifiers: gains

Differential amplifiers: parameters

$V_{out} = A_d \left( V_{id} - V_{io} \right)$

#### Linear response (with input offset voltage)

#### Input voltage ranges:

Input differential range (maximum  $V_{ID}$  ( $V_D$ ) to maintain an acceptable input-output linearity

$-V_{\rm DMAX} \leq V_{\rm D} \leq V_{\rm DMAX}$

#### Input common-mode range:

Interval of VC values where the amplifier behaves as designed

$$V_{\rm CMIN} \leq V_{\rm C} \leq V_{\rm CMAX}$$

#### Output voltage range (Output voltage swing)

$V_{\rm OMIN} \leq V_{\rm out} \leq V_{\rm OMAX}$

Outside the output range the amplifier stop working correctly (e.g. the output voltage tends to saturate) Differential amplifiers: role of the input common mode range

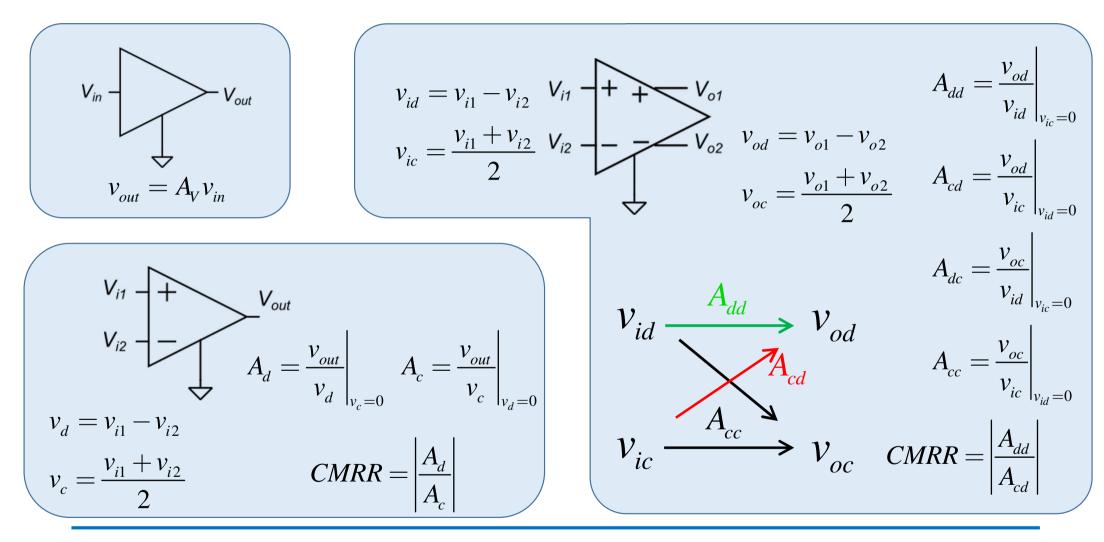

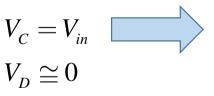

Example: voltage follower (buffer amplifier)

In the ideal case:

$$V_{io}=0, \ A_d \to \infty$$

We have:

The voltage follower operates correctly only for V<sub>in</sub> within the CM range Another condition is clearly that  $V_{out}$  is within the output range

Then the conditions for correct operation are:

$$V_{out} = V_{in} \text{ only for } \begin{cases} V_{CMIN} \leq V_{in} \leq V_{CMAX} \\ V_{OMIN} \leq V_{out} \leq V_{OMAX} \end{cases}$$

# Single Stage Voltage Amplifiers

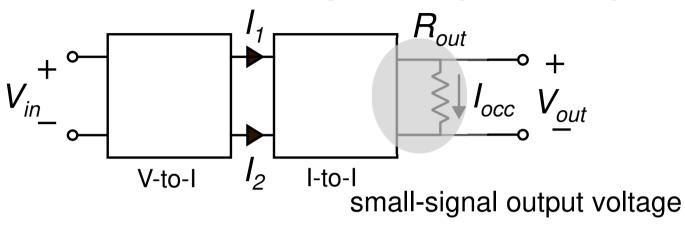

$$v_{out} = i_{occ} R_{out}$$

The first component converts the input voltage (single or differential) into a current (single or differential)

example

$I_1 - I_2 = G_{m1}V_{in}$

- The second component is a current processing network, that takes the input currents and applies simple linear operations such as:

- Addition and subtraction

- Addition of constant currents

- Multiplication by a constant gain factor

The processed currents are finally conveyed to an output resistance ( $R_{out}$ ) and converted back to a voltage ( $V_{out}$ ). In most cases, Rout is not a physical resistor, but is the output differential resistance of the I-to-I network. For this reason, one of the function of the I-to-I network is increasing the output resistance to increase gain

#### example

$$I_{occ} = k_I (I_1 - I_2) = G_{m1} k_I V_{in}$$

$$v_{out} = G_{m1} k_1 v_{in} R_{out}$$

defining:  $G_m = k_I G_{m1}$

$A = G_m R_{out}$

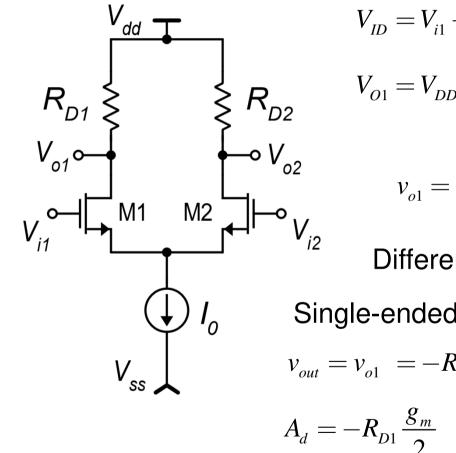

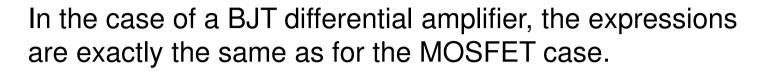

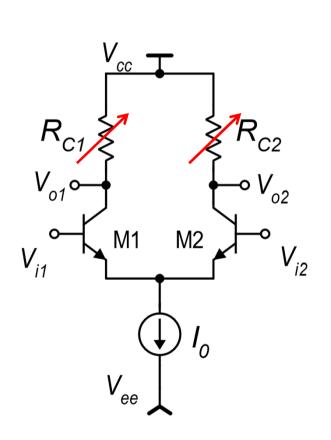

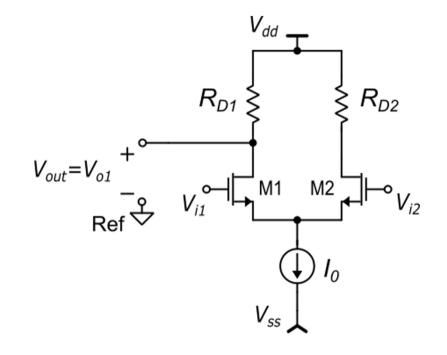

#### Differential amplifier with resistive loads

$$\begin{aligned} V_{1D} &= V_{i1} - V_{i2} \quad V_{0D} = V_{o1} - V_{o2} \\ V_{01} &= V_{DD} - R_{D1}I_{D1} \quad V_{02} = V_{DD} - R_{D2}I_{D2} \quad V_{0D} = R_{D2}I_{D2} - R_{D1}I_{D1} \\ & \text{Small signal analysis} \\ v_{o1} &= -R_{D1}i_{d1} \quad v_{o2} = -R_{D2}i_{d2} \quad v_{od} = i_{d2}R_{D2} - i_{d1}R_{D1} \\ & \text{Differential mode:} \quad i_{d1} = \frac{g_m}{2}v_{id} \quad i_{d2} = -\frac{g_m}{2}v_{id} \\ & \text{e-ended case:} \\ & \text{Fully-differential case:} \\ v_{out} &= v_{od} = -\frac{g_m}{2}(R_{D1} + R_{D2})v_{id} \\ & R_{D1}\frac{g_m}{2} \quad & A_{dd} = -g_m\frac{(R_{D1} + R_{D2})}{2} \end{aligned}$$

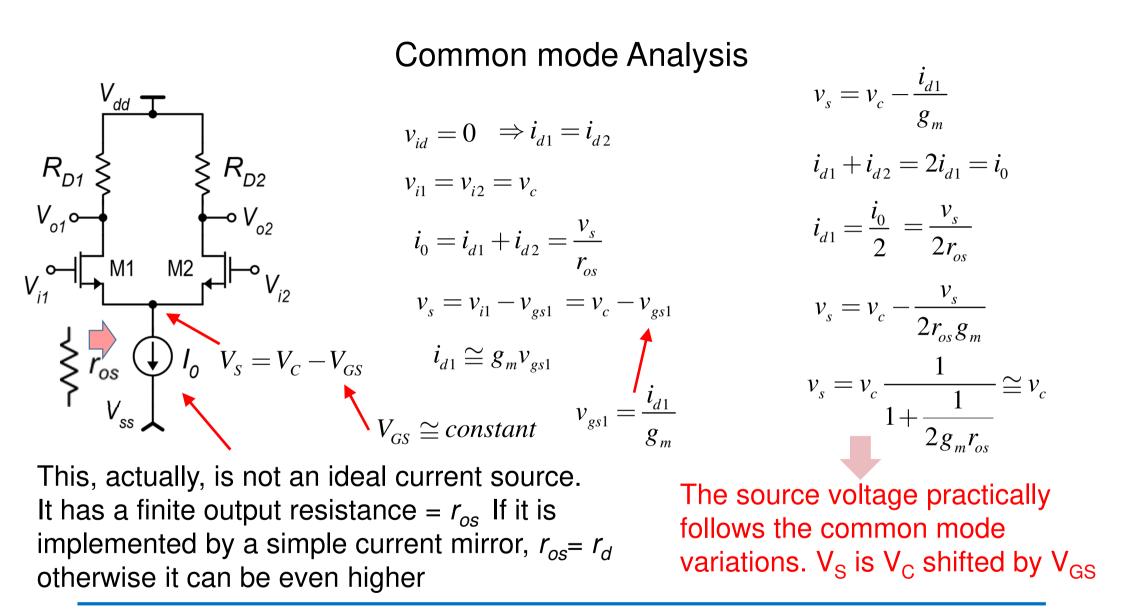

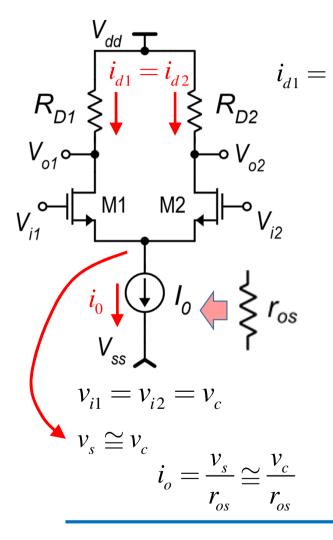

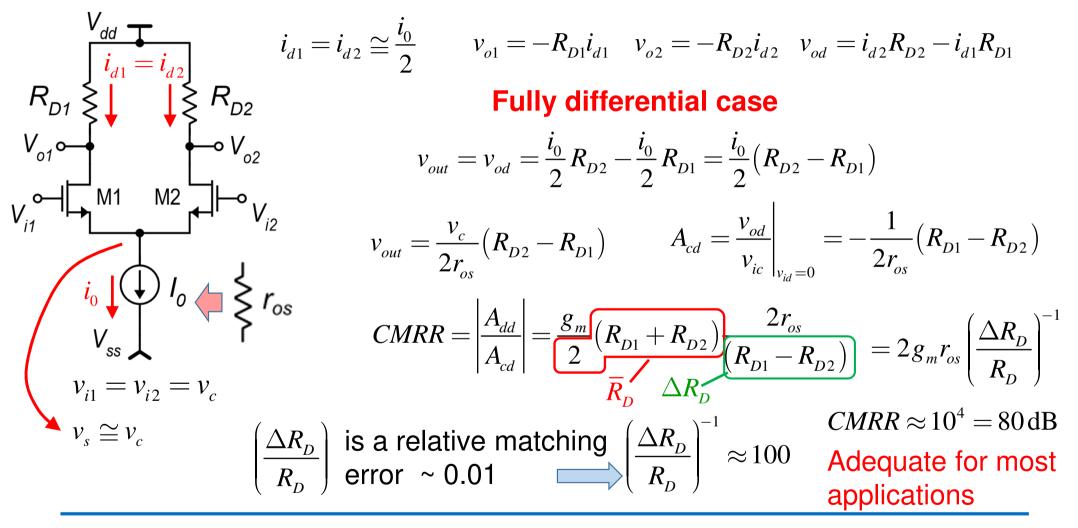

## Common mode gain and CMRR

output voltages  $i_{d1} = i_{d2} \cong \frac{i_0}{2}$   $i_{d1} = i_{d2} \cong \frac{i_0}{2}$   $v_{o1} = -R_{D1}i_{d1}$   $v_{o2} = -R_{D2}i_{d2}$   $v_{od} = i_{d2}R_{D2} - i_{d1}R_{D1}$ Single-ended case  $v_{o2}$   $v_{out} = v_{o1} = -R_{D1}i_{d1}$   $v_{out} - R_{D1}\frac{i_0}{2} \cong -R_{D1}\frac{v_c}{2r_{os}}$  $A_{c} = \frac{v_{out}}{v_{c}}\Big|_{v_{d}=0} \cong -\frac{R_{D1}}{2r_{os}} \qquad CMRR = \frac{A_{d}}{A} = \frac{g_{m}R_{D1}}{2}\frac{2r_{os}}{R}$  $CMRR = \left| \frac{A_d}{A_c} \right| = g_m r_{os}$  Considering that generally  $I_0$  is produced by a simple current mirror,  $r_{os} = r_d$ , then CMRR~40 dB,

This CMRR is not sufficient for many applications

### Common mode gain and CMRR

## BJT case

The only important difference is the presence of a base current that is drawn from the voltage sources that provide  $V_{i1}$  and  $V_{i2}$ . In terms of small signal analysis, this base current is the cause of a finite input resistance that may result in an input attenuation if the signal voltage sources ( $V_{i1}$ ,  $V_{i2}$ ) have a significant internal resistance.

Equivalent circuit of the input terminals

CC

M1

**I<sub>R1</sub>**

M2

'n

## Maximum gain for a given supply voltage

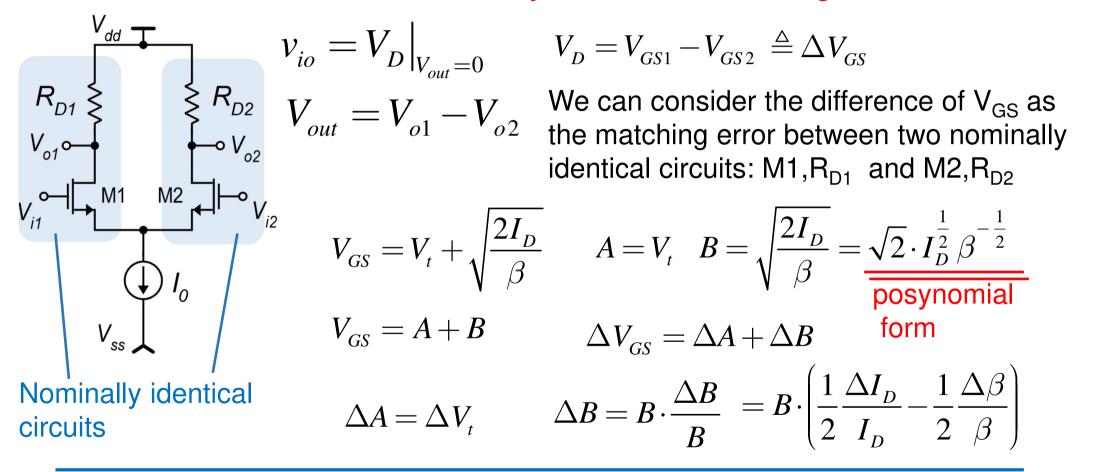

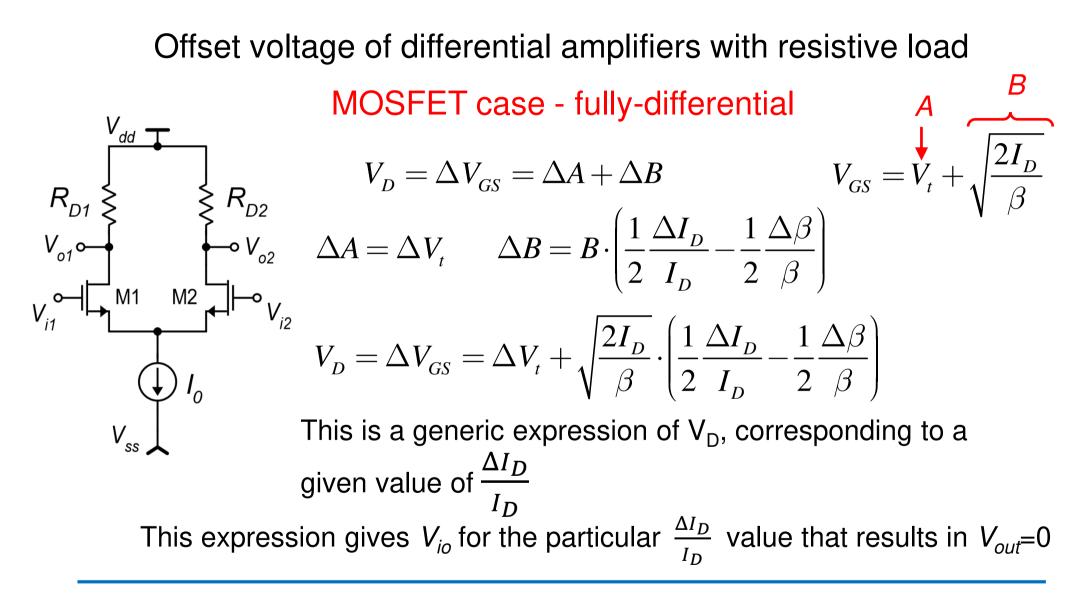

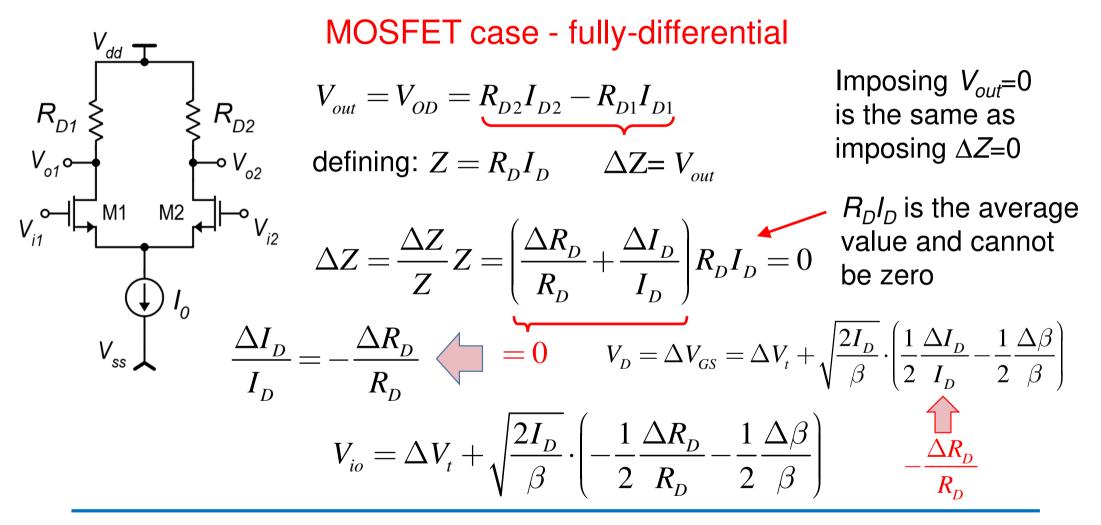

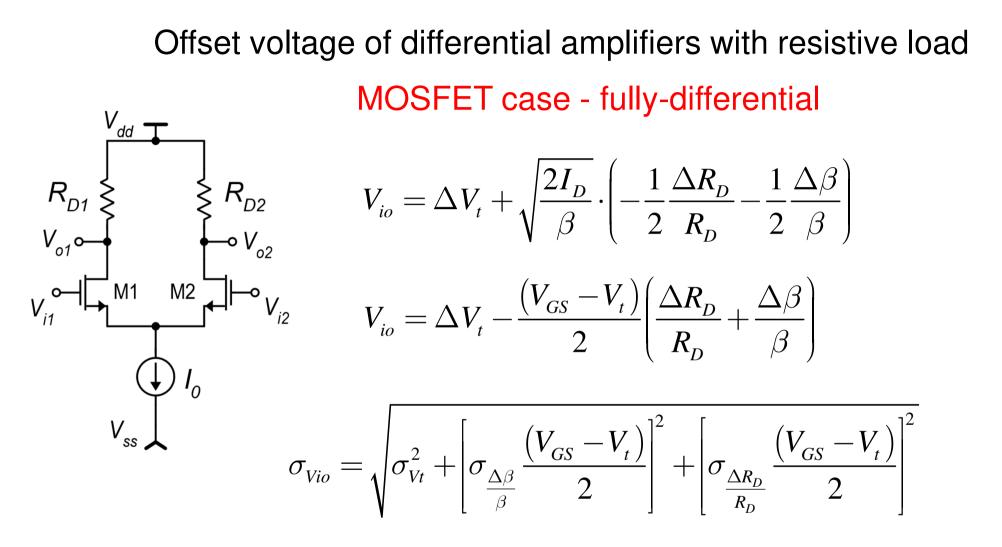

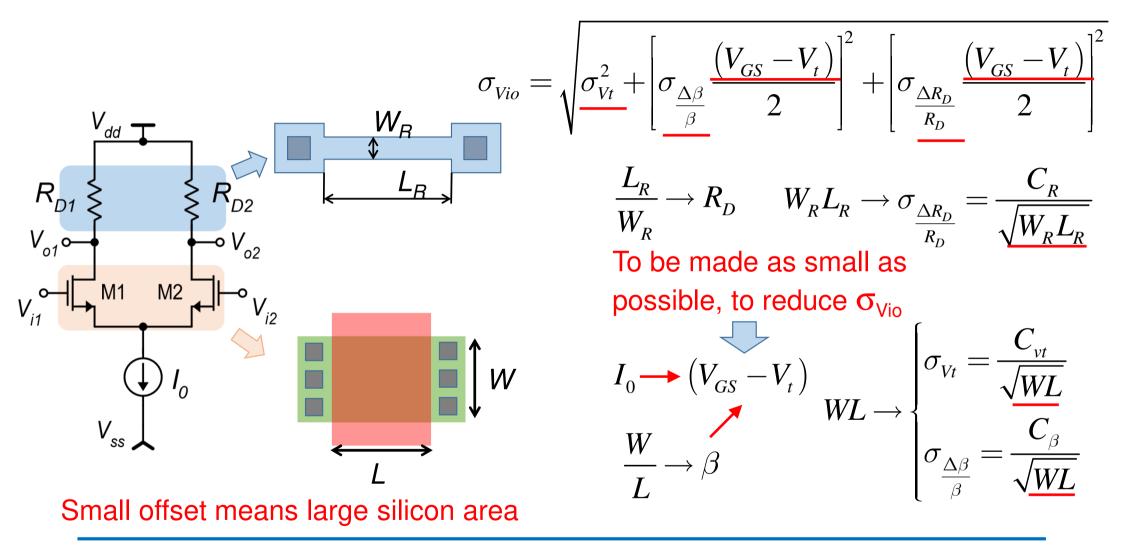

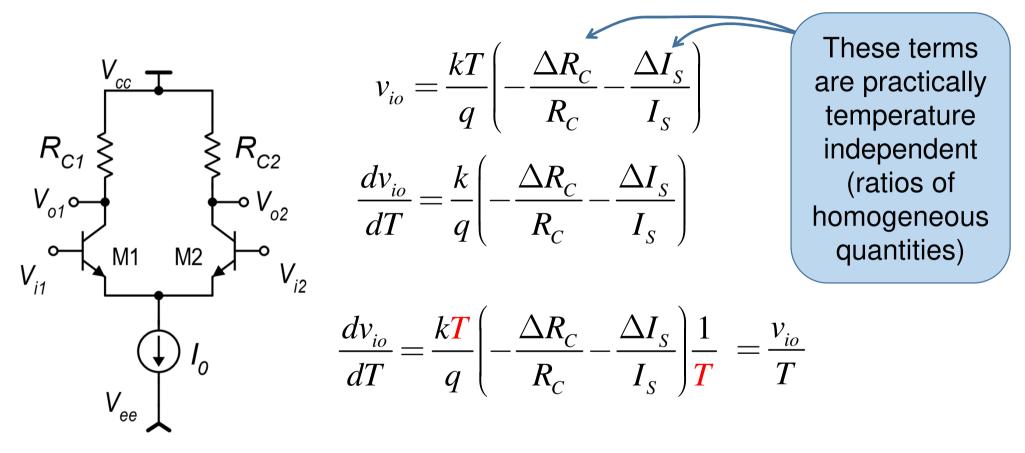

# Offset voltage of differential amplifiers with resistive load MOSFET case - fully-differential - Strong inversion

#### Offset voltage of differential amplifiers with resistive load

#### Role of the design parameters

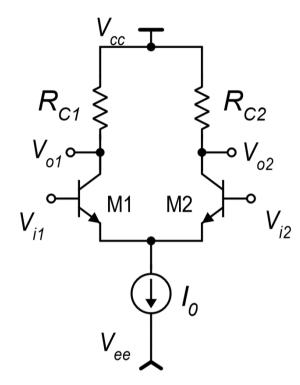

Offset voltage of a BJT differential amplifier with resistor load

$$\begin{aligned} v_{io} &= V_{id} \Big|_{V_{od}=0} \quad V_{od} = V_{o1} - V_{o2} = R_{C2}I_{C2} - R_{C2}I_{C2} \\ V_{id} &= V_{i1} - V_{i2} = V_{BE1} - V_{BE2} = \Delta V_{BE} \\ V_{BE} &= V_T \ln\left(\frac{I_C}{I_S}\right) \quad V_{id} = \Delta V_{BE} = V_T \left(\frac{\Delta I_C}{I_C} - \frac{\Delta I_S}{I_S}\right) \\ \underline{V_{od}} &= 0 \implies \Delta (R_C I_C) = 0 \implies \frac{\Delta I_C}{I_C} = -\frac{\Delta R_C}{R_C} \\ v_{io} &= V_T \left(-\frac{\Delta R_C}{R_C} - \frac{\Delta I_S}{I_S}\right) \end{aligned}$$

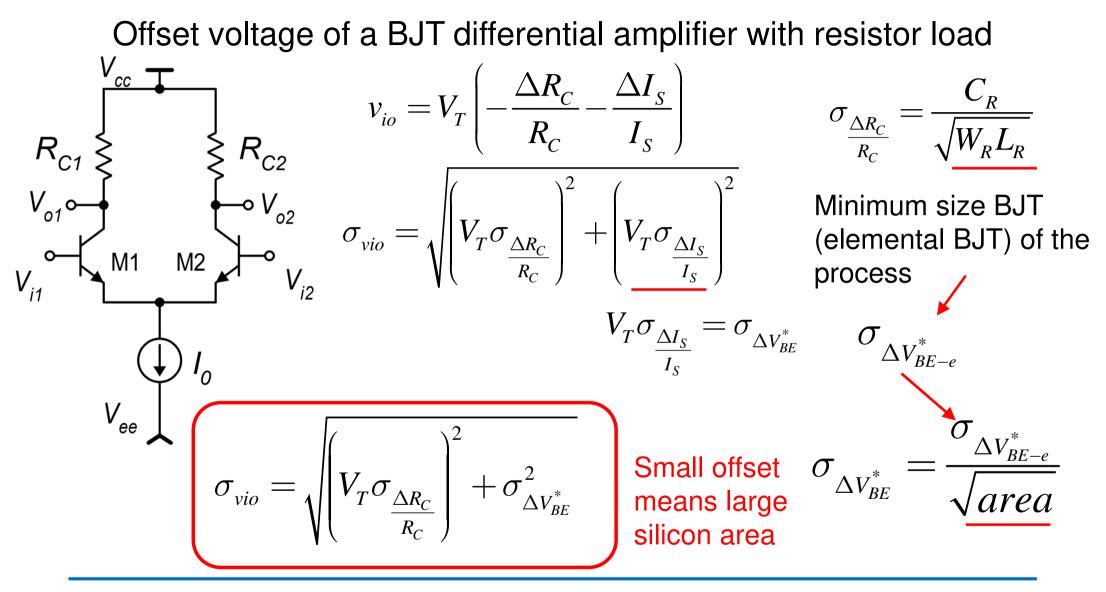

Temperature drift of the input offset voltage: BJT case

#### A method to reduce the offset voltage and its drift

$$\frac{dv_{io}}{dT} = \frac{v_{io}}{T}$$

$$\frac{dv_{io}}{dT} = \frac{1.0 \times 10^{-3}}{300} = 3.3 \ \mu\text{V/K}$$

By trimming the resistors, I can null the offset. In this way, also the temperature drift is nulled.

This is an advantage of the BJT amplifier. Trimming the offset of a MOSFET differential amplifier does not null the drift.

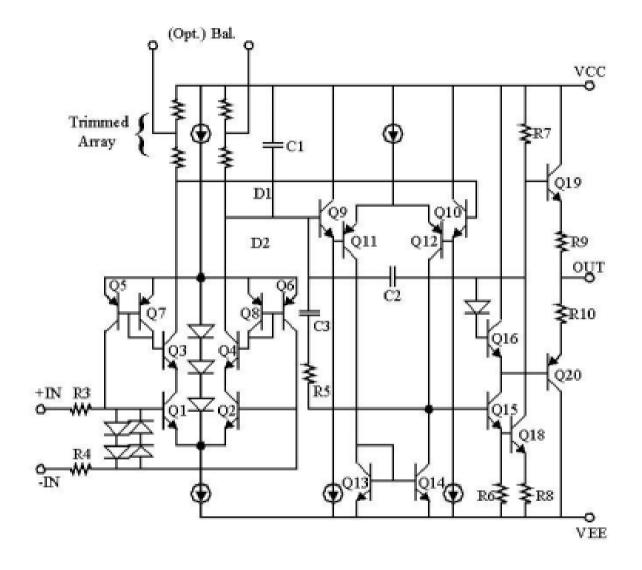

# Example: the OP07

- Resistors are varied by laser trimming to null the offset

- 2. In this way, also the offset drift is strongly reduced

- 3. The base currents of the input devices (Q1,Q2) are reproduced by Q3 and Q4 and than fed back to the input terminals by mirrors Q8,Q6 and Q7,Q5. This approach allows to reduce the input bias currents.

## OP07 vs $\mu$ A741

|      | Table 1.                                         |                       |                      |     |      |      |          |

|------|--------------------------------------------------|-----------------------|----------------------|-----|------|------|----------|

|      | Parameter                                        | Symbol                | Conditions           | Min | Тур  | Max  | Unit     |

| OP07 | INPUT CHARACTERISTICS                            |                       |                      |     |      |      |          |

|      | $T_A = 25^{\circ}C$                              |                       |                      |     |      |      |          |

|      | Input Offset Voltage <sup>1</sup>                | Vos                   |                      |     | 30   | 75   | μV       |

|      | Long-Term Vos Stability <sup>2</sup>             | V <sub>os</sub> /Time |                      |     | 0.3  | 1.5  | μV/Month |

|      | Input Offset Current                             | los                   |                      |     | 0.5  | 3.8  | nA       |

|      | Input Bias Current                               | IB                    |                      |     | ±1.2 | ±4.0 | nA       |

|      | 0°C ≤ T <sub>A</sub> ≤ 70°C                      |                       |                      |     |      |      |          |

|      | Input Offset Voltage <sup>1</sup>                | Vos                   |                      |     | 45   | 130  | μV       |

|      | Voltage Drift Without External Trim <sup>4</sup> | TCVos                 |                      |     | 0.3  | 1.3  | μV/°C    |

|      | Voltage Drift with External Trim <sup>3</sup>    | TCV <sub>OSN</sub>    | $R_P = 20 \ k\Omega$ |     | 0.3  | 1.3  | μV/°C    |

at specified virtual junction temperature, v<sub>CC±</sub> - ±15 v (unless otherwise noted)

μA741

| PARAMETER            |                             | T                  | TEST CONDITIONS <sup>(1)</sup> |  | TYP | MAX | UNIT |

|----------------------|-----------------------------|--------------------|--------------------------------|--|-----|-----|------|

| v                    | Input offset voltage        | V = 0              | 25°C                           |  | 1   | 6   | mV   |

| Vio                  |                             | V <sub>0</sub> = 0 | Full range                     |  |     | 7.5 |      |

| $\Delta V_{IO(adj)}$ | Offset voltage adjust range | V <sub>0</sub> = 0 | 25°C                           |  | ±15 |     | mV   |

|                      | Input offset current        | V = 0              | 25°C                           |  | 20  | 200 | nA   |

| 10                   |                             | V <sub>0</sub> = 0 | Full range                     |  |     | 300 |      |

|                      | Input bias current          | V = 0              | 25°C                           |  | 80  | 500 | n A  |

| IB                   |                             | V <sub>0</sub> = 0 | Full range                     |  |     | 800 |      |

P. Bruschi – Microelectronic System Design

22

How is the amplifier offset when the single ended option is chosen?

$$V_{out} = V_{O1} = V_{dd} - R_1 I_{D1}$$

Single ended (S/E): device parameters do not appear as differences: the output voltage is affected mainly by global errors

> The single ended case is subjected to a much larger offset!

Compare with the fully-differential case: the output voltage depends only on matching differences  $V_o$

$$V_{od} = R_{D2} I_{D2} - R_{D1} I_{D1}$$