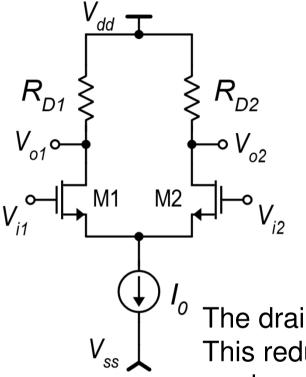

CMOS differential amplifier with resistive load: limitations

- 1. The S/E version has a poor CMRR (large  $A_c$ ) and large input offset voltage

- 2. Both the S/E and fully-diff. versions reach low voltage gains at small supply voltage

**Suggestion for problem 1**: Consider the output voltage in the fully-differential case with no resistor mismatch:

$$V_{OD} = R_D \left( I_{D2} - I_{D1} \right) \text{ (for } R_{D1} = R_{D2} \text{)}$$

The drain current difference appears:

This reduces  $A_c$  ( $I_{D1}$  and  $I_{D2}$  tend to be equal for only common mode applied) and the output voltage for  $V_D=0$  is affected only by matching errors.

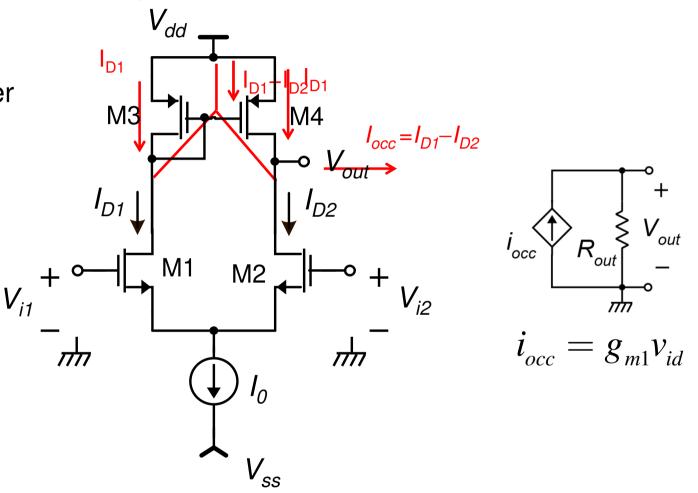

Solution for a S/E amplifier: produce the current difference  $(I_{D1}-I_{D2})$  and then put it into a single resistor. **Problem 2:** Do not use a passive component for the resistor

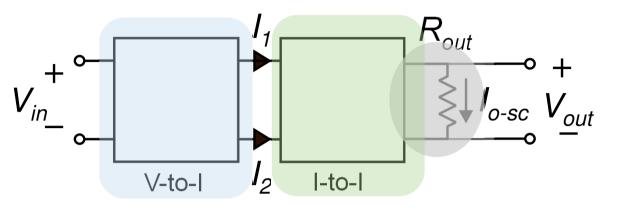

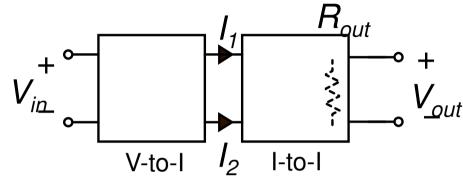

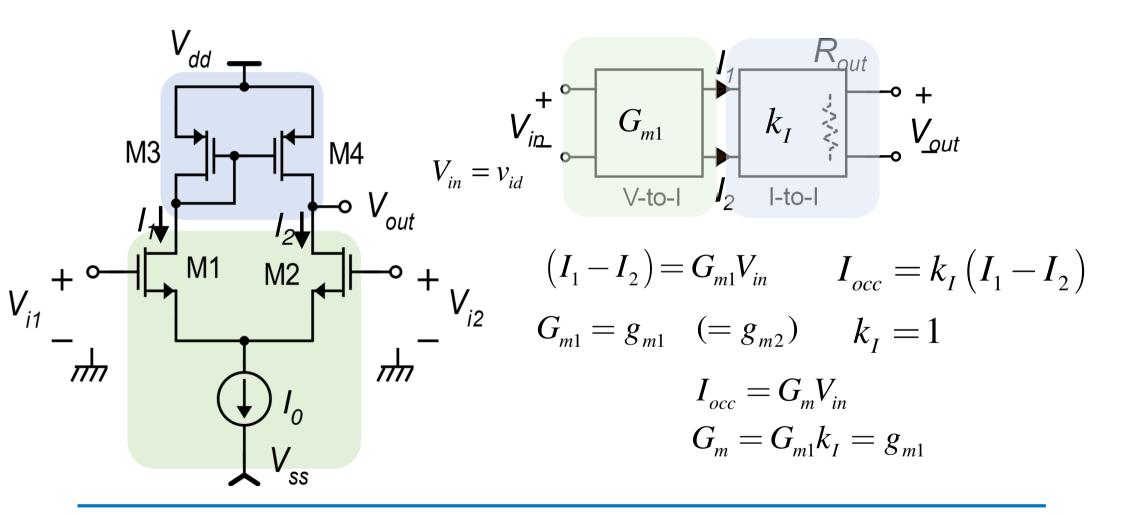

#### A more general case: single-stage voltage amplifiers

The first component converts the input voltage (single or differential) into a current (single or differential)

example:

$$I_1 - I_2 = G_{m1}V_{in}$$

(Linear Model)

The second component is a current processing network, that takes the input currents and applies simple linear operations such as:

- Addition and subtraction

- Addition of constant currents

- Multiplication by a constant gain factor

example:

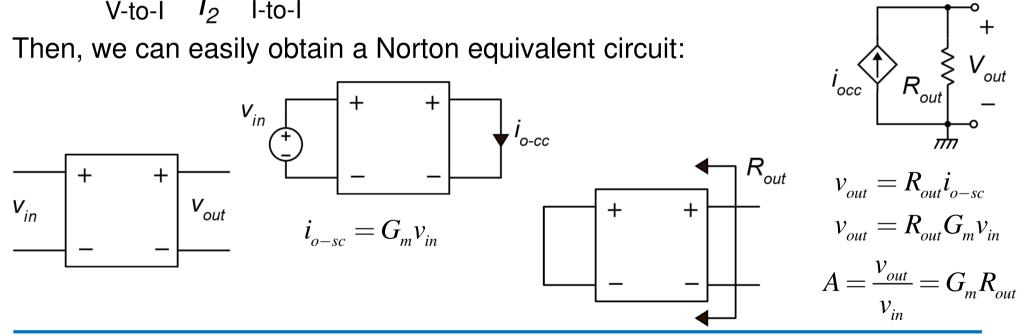

The processed currents are finally conveyed to an output resistance ( $R_{out}$ ) and converted back to a voltage ( $V_{out}$ ). In most cases,  $R_{out}$  is not a physical resistor, but it is the output differential resistance of the I-to-I network. For this reason, one of the function of the I-to-I network is increasing the

output resistance to increase gain  $V_{out} = I_{o-sc}R_{out} = k_1G_{m1}V_{in}R_{out}$

defining:  $G_m = k_I G_{m1}$  $I_{o-sc} = G_m V_{in} \implies V_{out} = G_m V_{in} R_{out}$

$$A = \frac{V_{out}}{V_{in}} = G_m R_{out}$$

Output short circuit current

$$\Rightarrow I_{o-sc} = k_I (I_1 - I_2) = k_I G_{m1} V_{in}$$

A general method for calculation of the gain in single-stage amplifiers

In a single-stage amplifier it is generally simple to calculate the output short-circuit current  $i_{o-sc}$

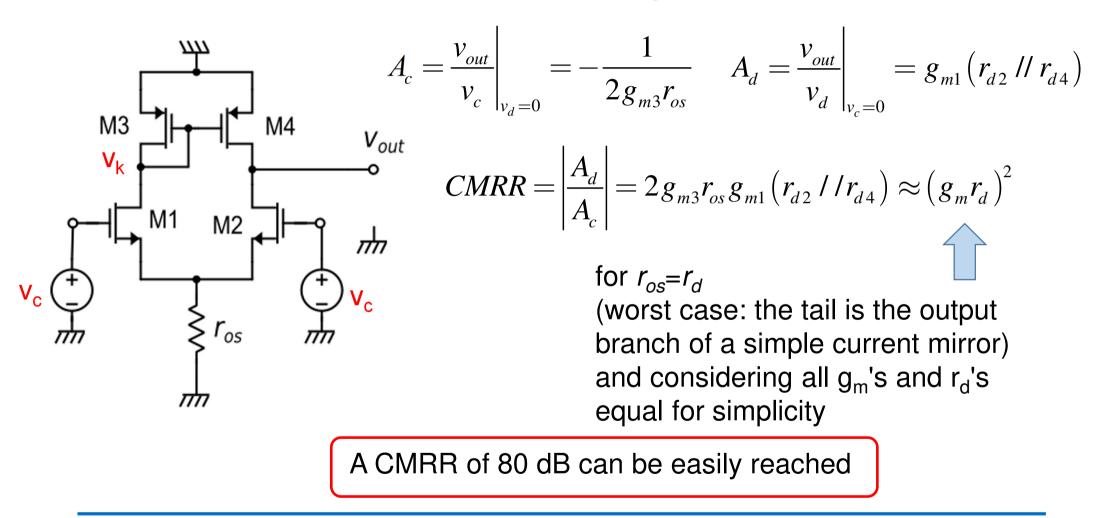

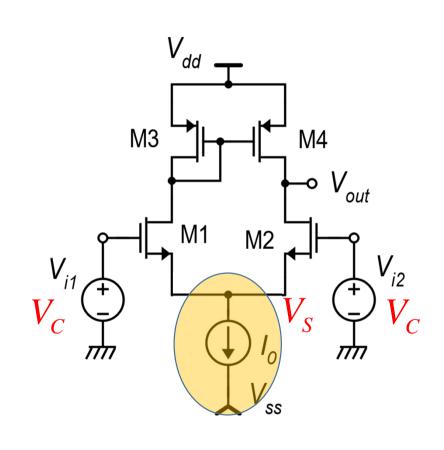

#### CMOS differential amplifier with current mirror load

Specifications

- We need a S/E amplifier

- High CMRR (> 80 dB)

- High gain (~ 40 dB) even at low supply voltages (V<sub>dd</sub>-V<sub>ss</sub>).

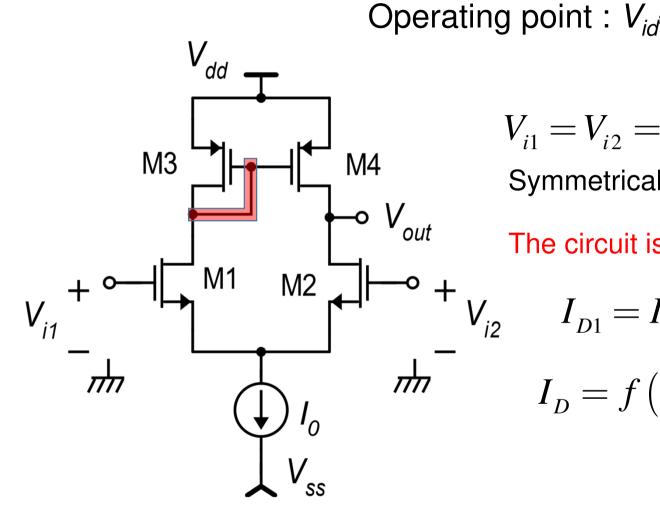

Subunits of the amplifier with mirror load

$V_{i1} = V_{i2} = V_C$

Symmetrical stimulus, but ....

The circuit is not symmetrical

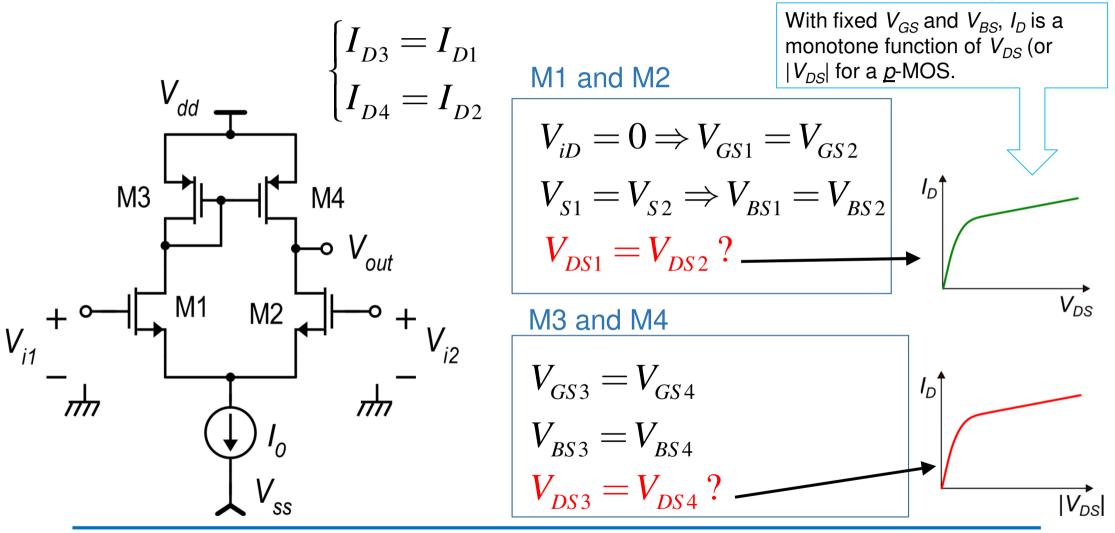

$$I_{D1} = I_{D2}$$

exactly?

$$I_D = f\left(V_{GS}, V_{BS}, V_{DS}\right)$$

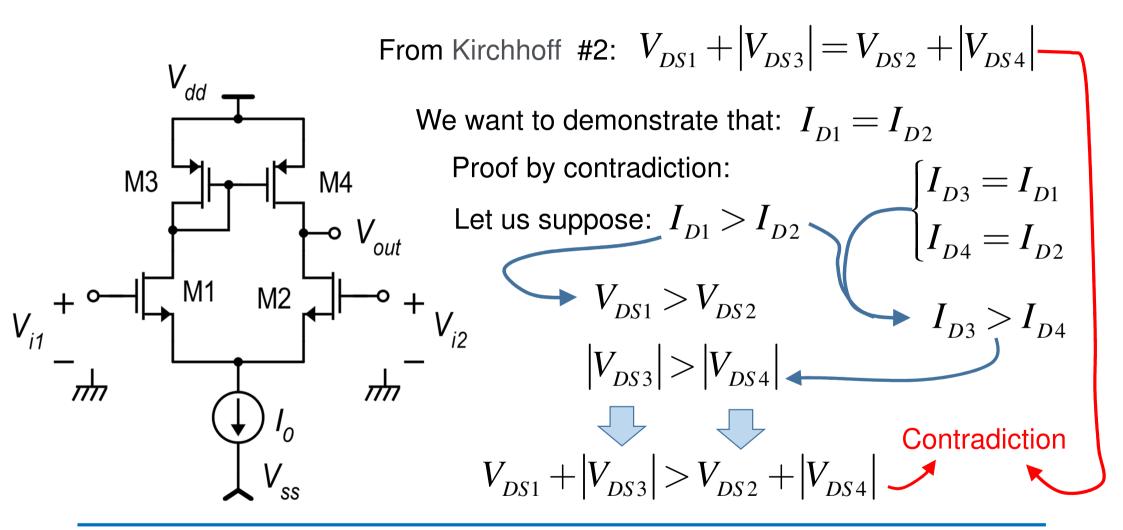

Demonstration of the exact symmetry of the electrical solution for  $V_{id}=0$

P. Bruschi – Microelectronic System Design

7

Demonstration of the exact symmetry of the electrical solution for  $V_{id}=0$

Demonstration of the exact symmetry of the electrical solution for  $V_{id}=0$

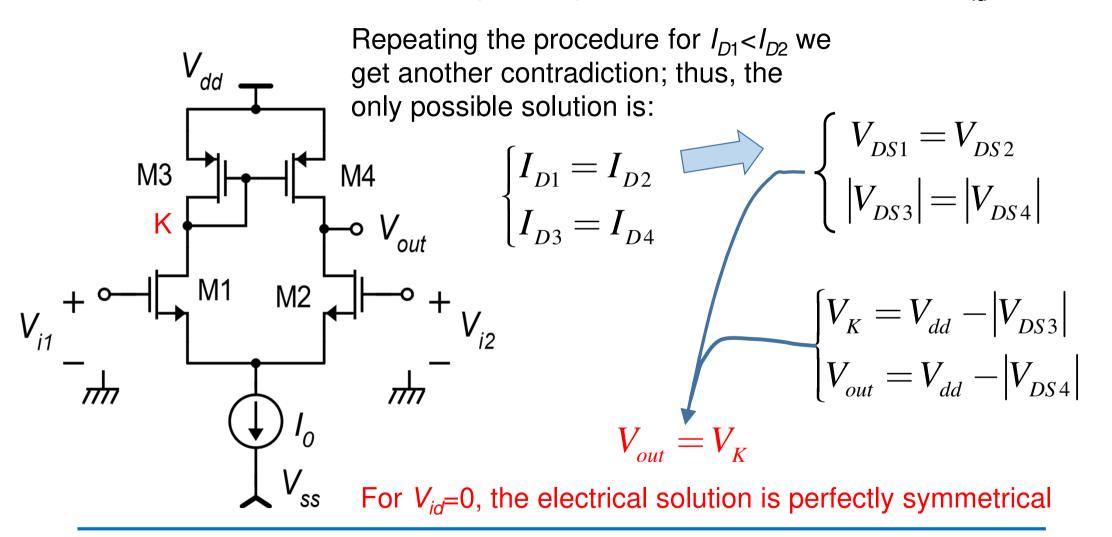

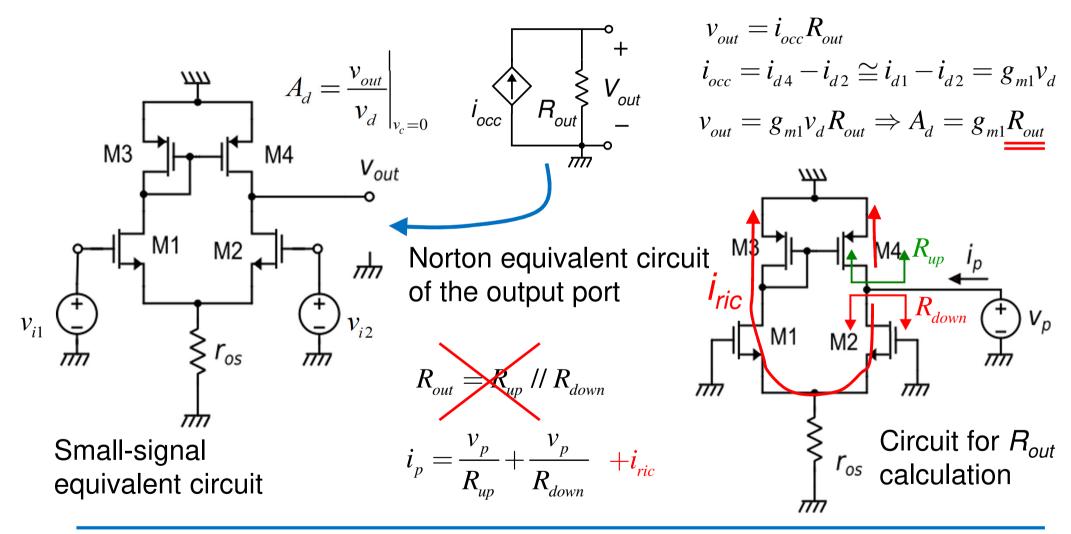

### Differential mode gain

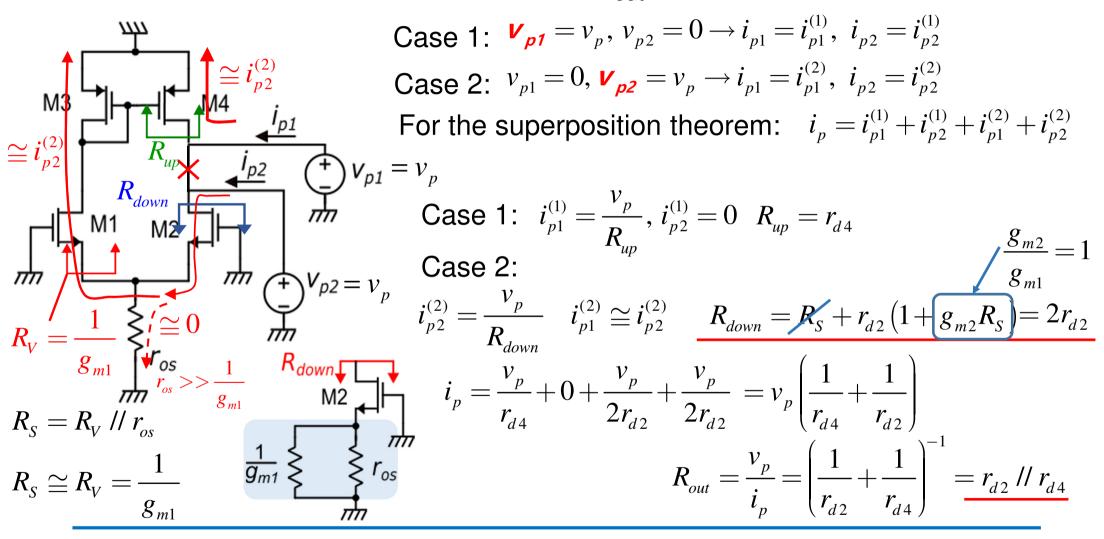

#### Differential mode gain: $R_{out}$ calculation.

P. Bruschi – Microelectronic System Design

11

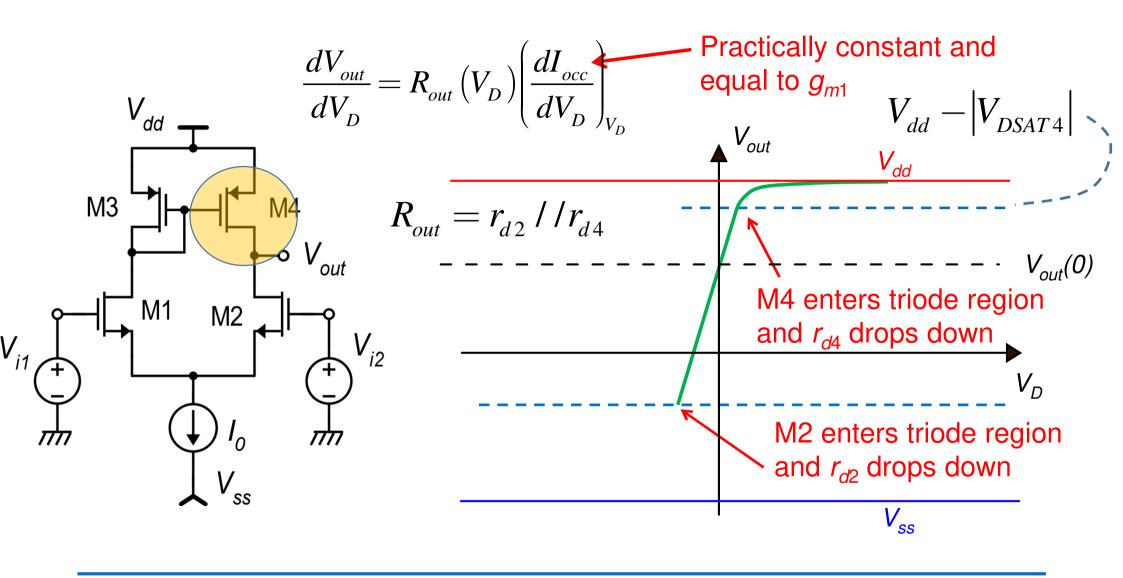

### Differential mode gain

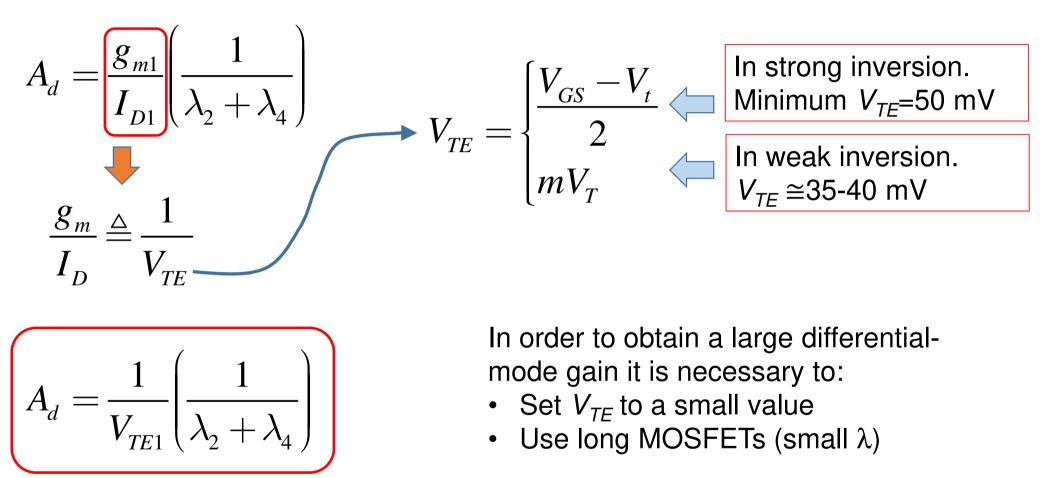

$R_{out} = r_{d2} / r_{d4}$ Just to find the order of magnitude we can assume:  $r_{d2} = r_{d4} = r_d$  $A_d = g_{m1} R_{out} = g_{m1} (r_{d2} / r_{d4})$  $A_d = \frac{g_m r_d}{2} \sim 50$  Independently from the supply voltage  $A_{d} = g_{m1} \left[ \frac{1}{\frac{1}{r_{d2}} + \frac{1}{r_{d4}}} \right] \qquad \frac{1}{r_{d}} = g_{d} = \lambda I_{D} \qquad A_{d} = g_{m1} \left[ \frac{1}{\lambda_{2} I_{D2} + \lambda_{4} I_{D4}} \right]$  $A_{d} = \frac{g_{m1}}{I_{D1}} \left[ \frac{1}{\lambda_{2} + \lambda_{4}} \right] \qquad I_{D2} = I_{D4} = I_{D1}$

Differential mode gain

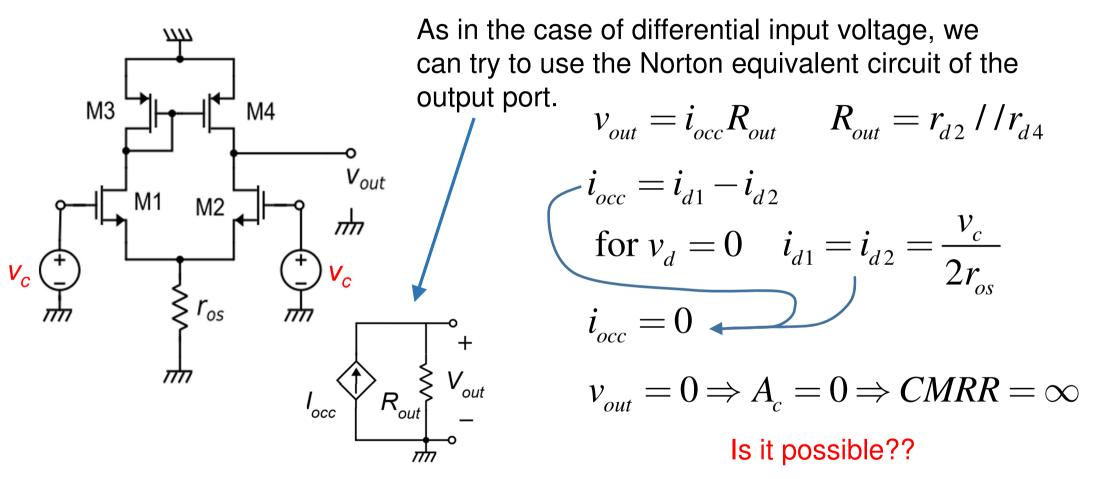

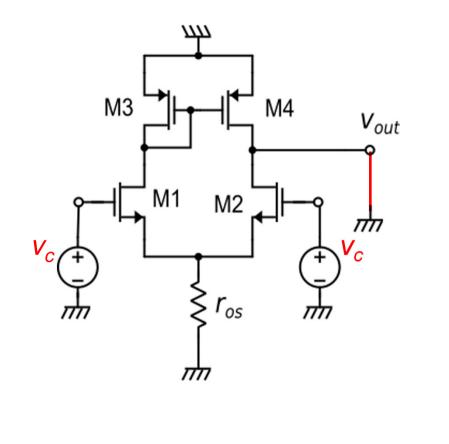

The problem occurs when we calculate iocc. Placing a short circuit across the output port, disrupts the symmetry:

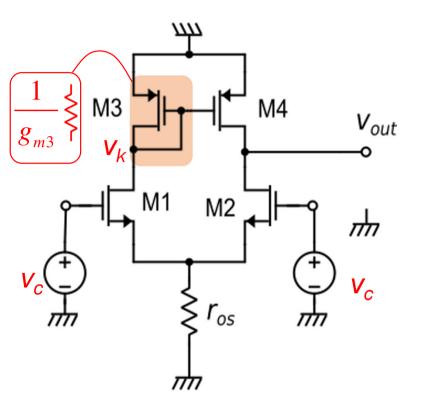

$$v_{ds4} = 0 \quad v_{ds3} = -\frac{1}{g_{m3}} i_{d1} \neq 0$$

$$v_{ds1} = -\frac{1}{g_{m3}} i_{d1} - v_{s1} \quad v_{ds2} = -v_{s1} \neq v_{ds1}$$

$$i_{d1} \neq i_{d2} \qquad i_{occ} = i_{d4} - i_{d2} \neq 0$$

<sup>*i*</sup>d2

$$i_{d3} \neq i_{d4}$$

It is possible to exactly calculate  $i_{occ}$ , taking into account the actual  $i_{d1}/i_{d2}$  ratio and  $i_{d4}/i_{d3}$  ratio ....

... but this is a very tedious approach There is a much simpler way:

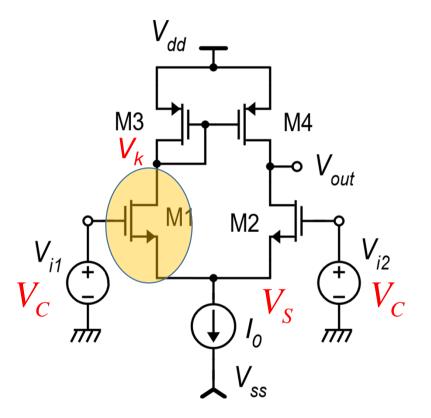

Let us remove the short circuit and directly calculate  $v_{out}$ . Now , for  $v_{id}=0$ , the circuit is symmetric again and, in particular:  $v_k = v_{out}$  $v_{out} = v_k = -\frac{1}{g_{m3}}i_{d1} \cong -\frac{v_c}{2r_{os}g_{m3}}$

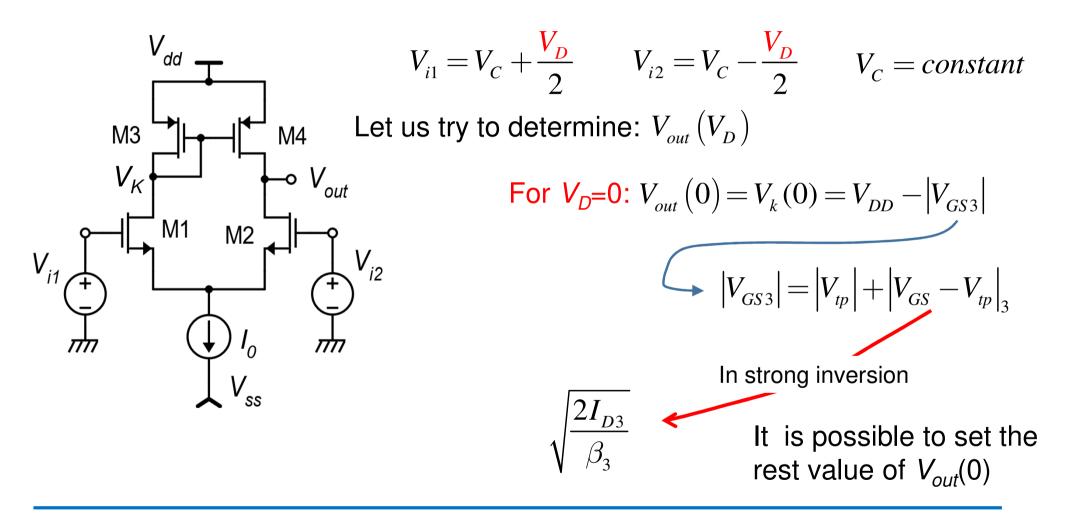

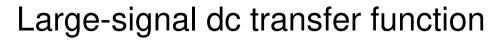

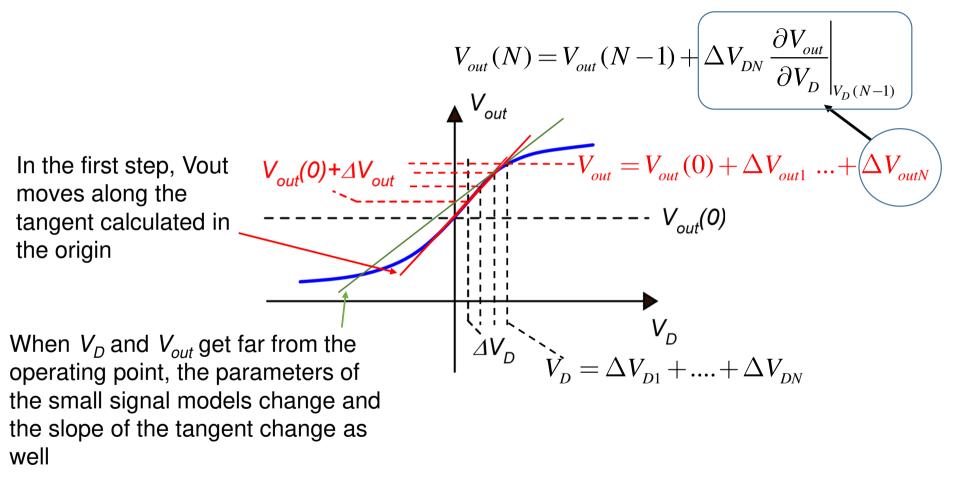

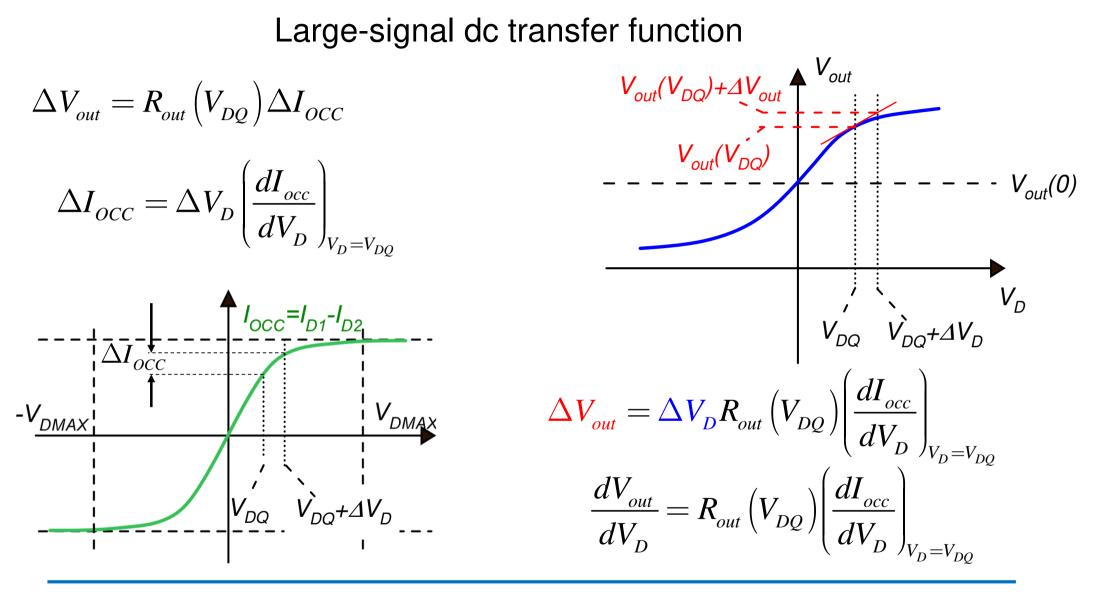

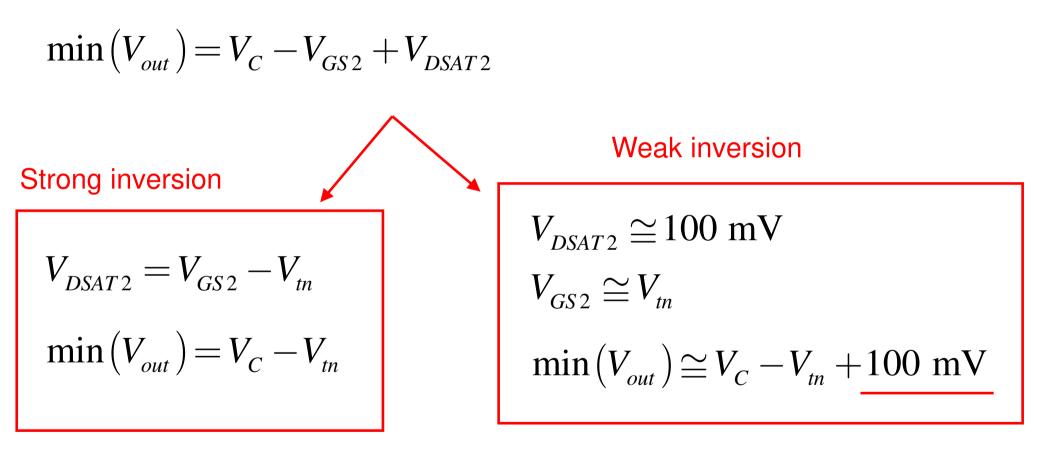

Large-signal dc transfer function

Moving away from the origin, step by step

P. Bruschi – Microelectronic System Design

#### Approximate dc transfer characteristic

P. Bruschi – Microelectronic System Design

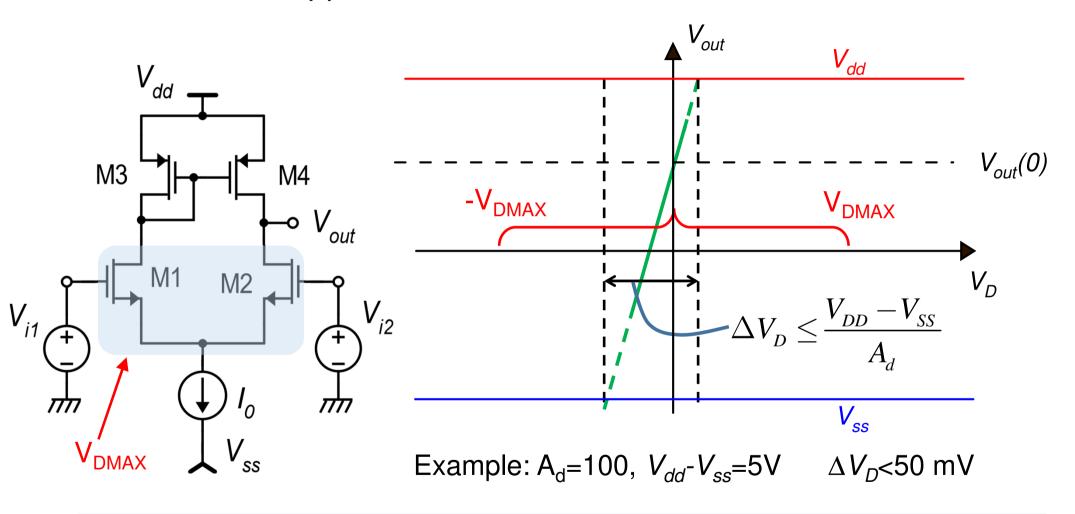

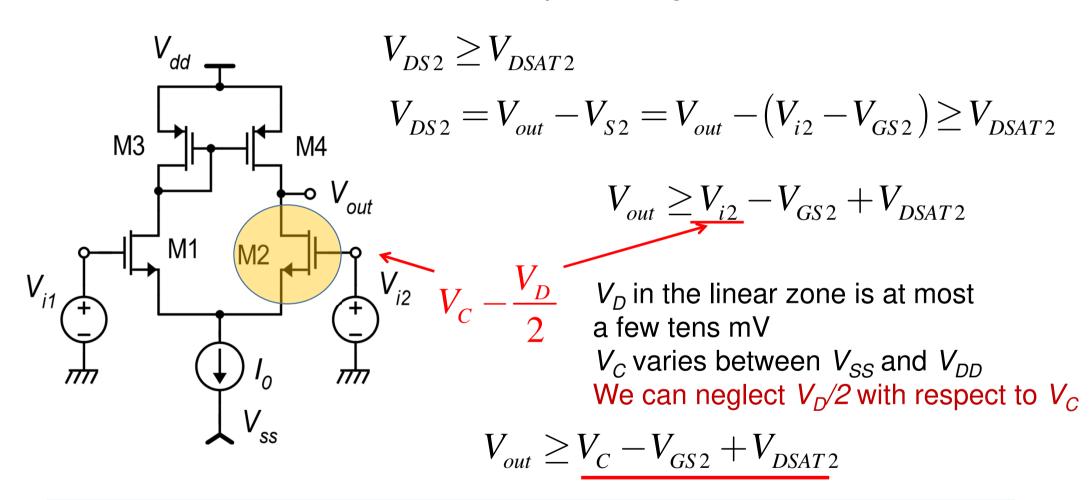

Minimum output voltage

### Minimum output voltage

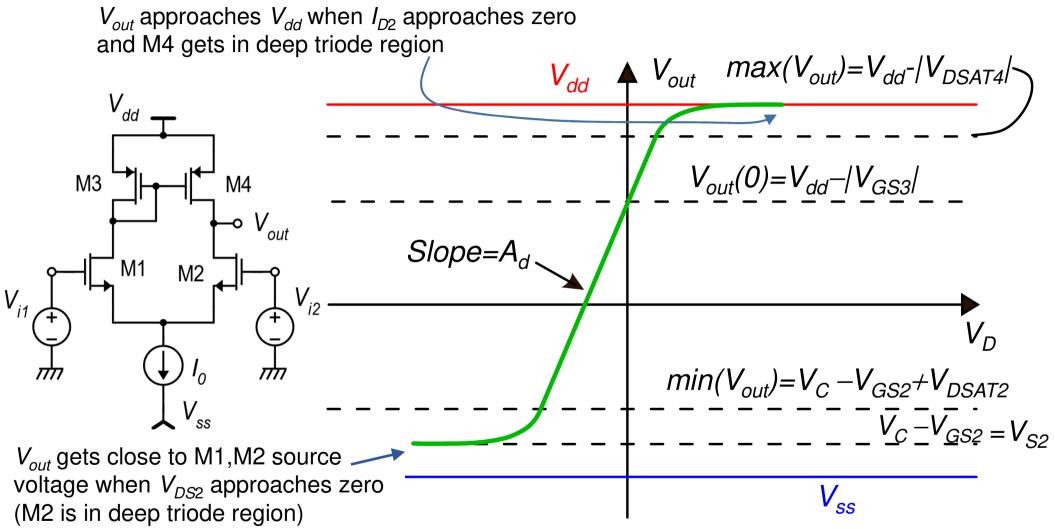

### Complete dc transfer characteristic

P. Bruschi – Microelectronic System Design

Minimum supply voltage  $V_{dd}$ - $V_{ss}$

# Input common mode range

#### Lower limit

As  $V_C$  is progressively decreased, also  $V_S$  decreases at the same pace and eventually the voltage across the current source  $I_0$  will get smaller than the minimum value  $V_{MIN}$ . From that point on,  $I_0$  will rapidly decrease, turning off the stage.

$$\min\left(V_{C}\right) = V_{SS} + V_{MIN} + V_{GS1}$$

Note: when the output voltage of the current source  $I_0$  gets below  $V_{MIN}$ , its output resistance  $(r_{os})$  gets small, degrading the CMRR.

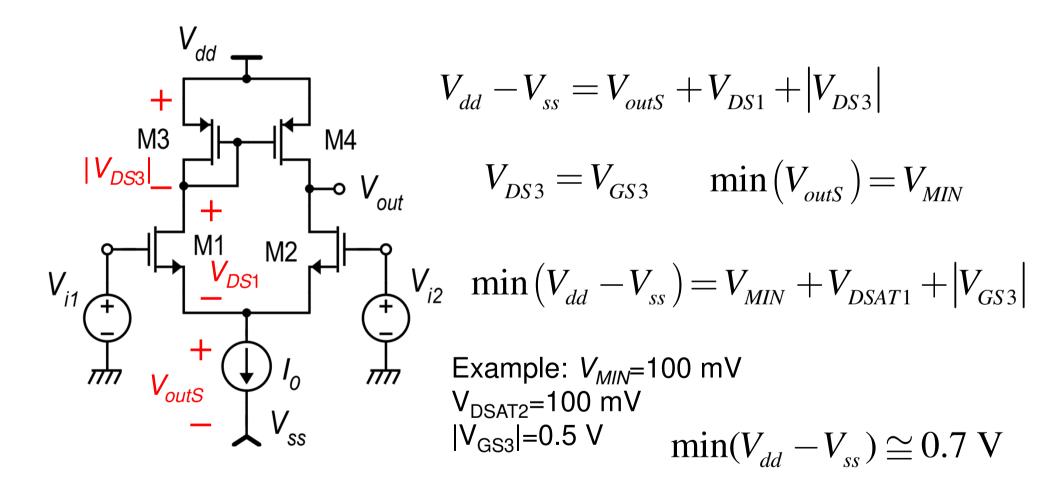

### Input common mode range

#### **Upper limit**

As  $V_C$  is progressively increased, also  $V_S$ increases at the same pace. Since  $V_{out} = V_K = V_{D2}$ =  $V_{D1}$  is fixed, eventually  $V_{DS1}$  and  $V_{DS2}$  will drop below the saturation voltage.

$$V_{DS1} = V_{K} - V_{S1} \ge V_{DSAT1}$$

$$V_{dd} - |V_{GS3}| - (V_{C} - V_{GS1}) \ge V_{DSAT1}$$

$$V_{dd} - |V_{GS3}| + V_{GS1} - V_{DSAT1} \ge V_{C}$$

Input common mode range: upper limit  $V_{dd}$  $V_{dd} - |V_{GS3}| + V_{GS1} - V_{DSAT1} \ge V_C$ M4 М3  $V_{out}$   $|V_{GS3}| = |V_{tp3}| + |V_{GS3} - V_{tp3}|$ M1 M2 *V*<sub>i2</sub>  $V_{GS1} = V_{tn1} + (V_{GS1} - V_{tn1})$  These overdrive voltages can be made equal by design, so they cancel each other  $\max(V_C) =$  $= V_{dd} - |V_{tp3}| + V_{tn1} - |V_{GS3} - V_{tp3}| + (V_{GS1} - V_{tn1}) - V_{DSAT1}$ This difference can be >0 because it is likely that:  $V_{tn1} > |V_{tp3}|$   $(V_{t1} \text{ is affected by body effect}$ if M1 and M2 body is at  $V_{SS}$ ) This difference can be >0The input common mode voltage can get even slightly higher than  $V_{dd}$