#### Comparators

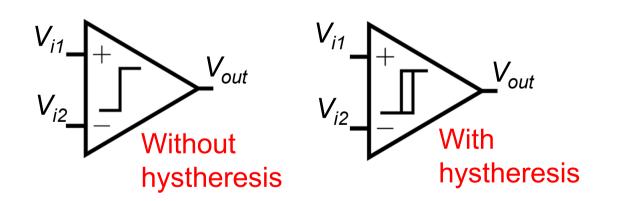

Continuous-time vs dynamic comparator

#### **Continuous-time comparator:**

- Higher power consumption

- Hystheresis

- Output always valid

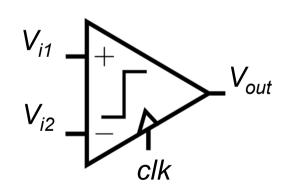

Dynamic comparator (or latched comparator):

- Lower power consumption

- No hysteresis

- Need a clock signal

## Comparators: amplifier-based implementations

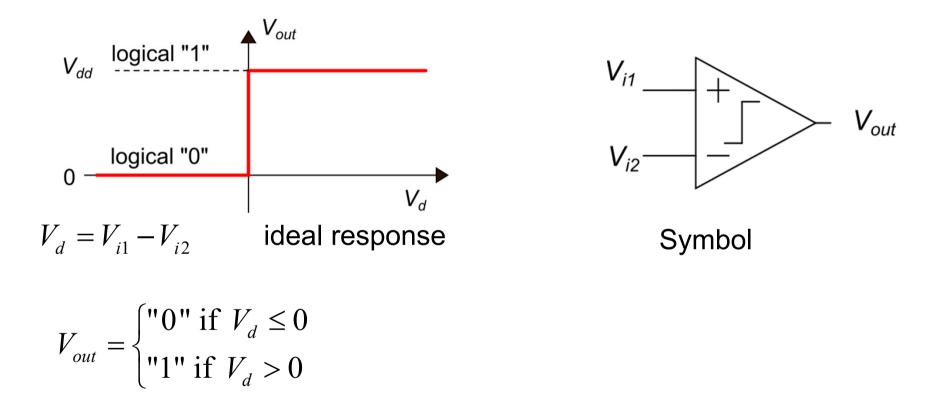

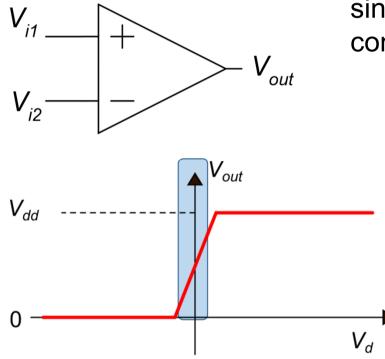

An amplifier with very high gain can be used as a comparator. Opamp topologies can be used with no need of frequency compensation

Note:

a region exists

where the logical

level is undefined

since the comparator is used in open loop configuration or positive feedback.

In several application this may lead to unwanted stable or metastable states. For slow-varying signals, threshold crossing may be too noisy Regenerative comparators: hysteresis

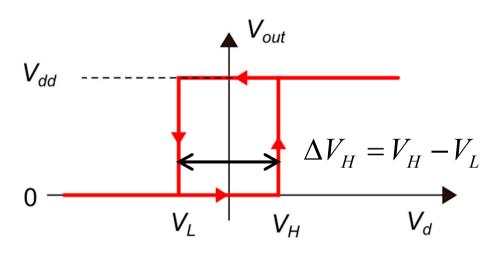

Thanks to the hysteresis, the comparator produces a valid output level across the whole input range

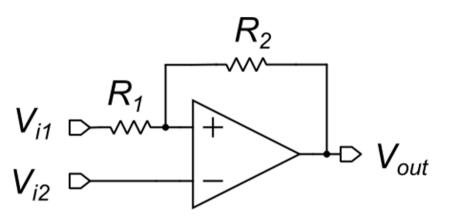

The hysteresis introduces an uncertainty band that reduces the accuracy but helps rejecting noise when the input voltage is close to zero. Possible regenerative comparator

Op-amp based Smith trigger.

### Drawbacks

- Oversized solution for integrated cells

- Low impedance on the non-inverting input

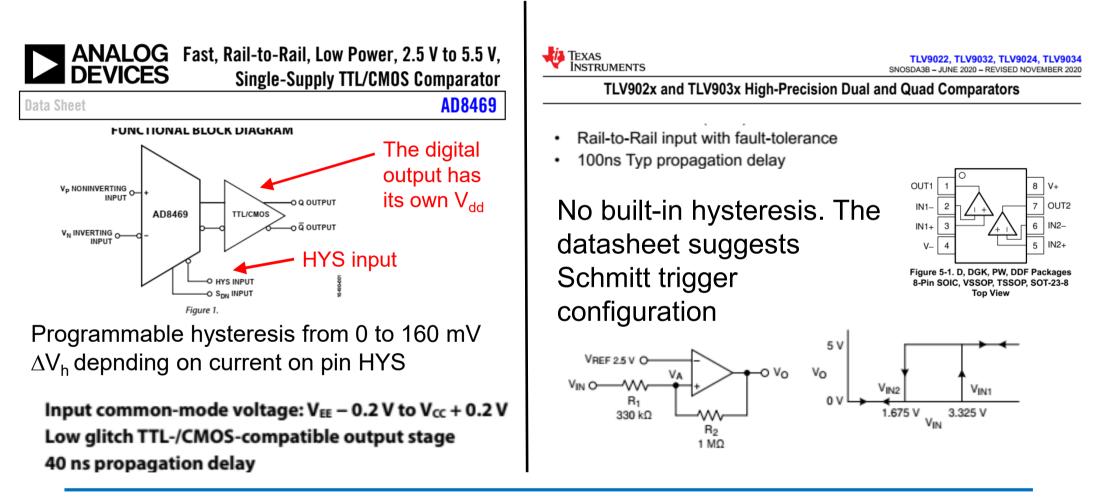

# **Commercial products**

Compact comparator cell for Systems on a Chip

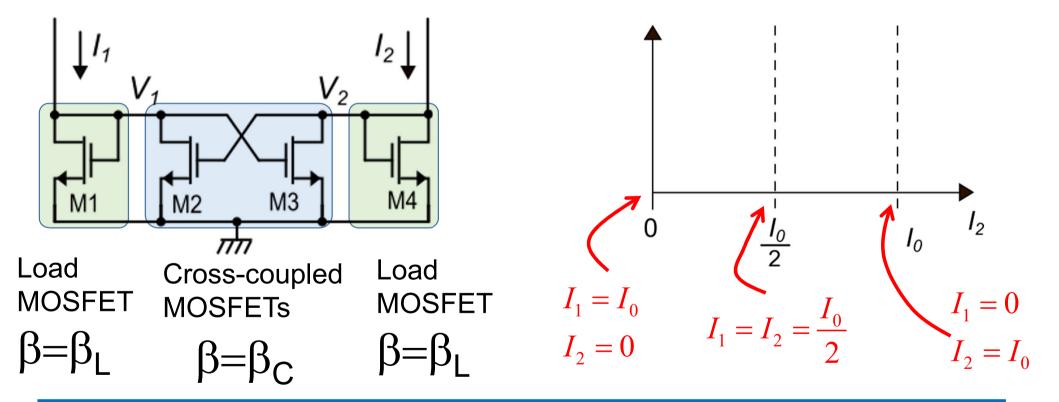

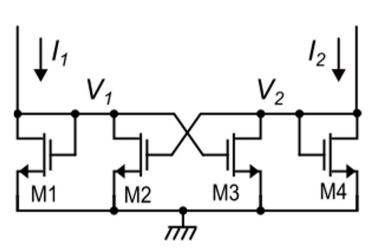

Four-transistor hysteresis cell

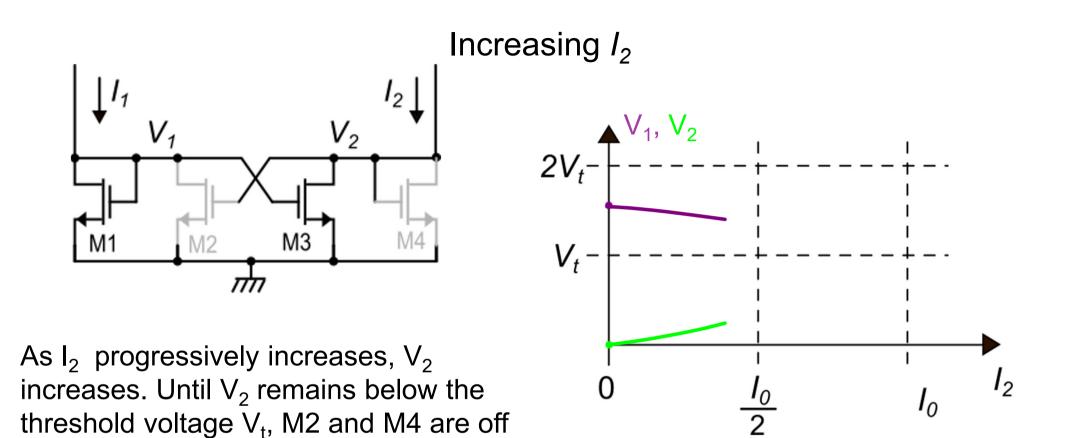

Currents  $I_1$  and  $I_2$  varies with the input signal in such a way that:  $I_1 + I_2 = I_0 = constant$

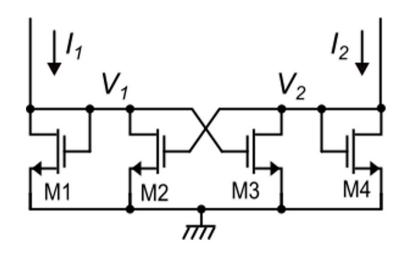

Analysis of the four-transistor hysteresis cell: starting point

Let us start from:  $I_2=0$  ( $I_1=I_0$ )  $I_2 = I_{D3} + I_{D4} = 0$ since:  $I_{D3}, I_{D4} \ge 0$   $I_{D3} = I_{D4} = 0$ Considering M4:  $V_{GS4} \leq V_t$  $V_{GS2} = V_{GS4}$   $I_{D2} = 0$ Then it is M1 that carries all current I<sub>1</sub>:  $V_1 = V_{GS1} = V_t + \sqrt{\frac{2I_1}{\beta_t}} = V_t + \sqrt{\frac{2I_0}{\beta_t}}$  $V_{GS3} = V_{GS1} \ge V_t \quad (M3 \text{ is on})$   $I_{D3} = 0$   $V_{DS3} = V_2 = 0$

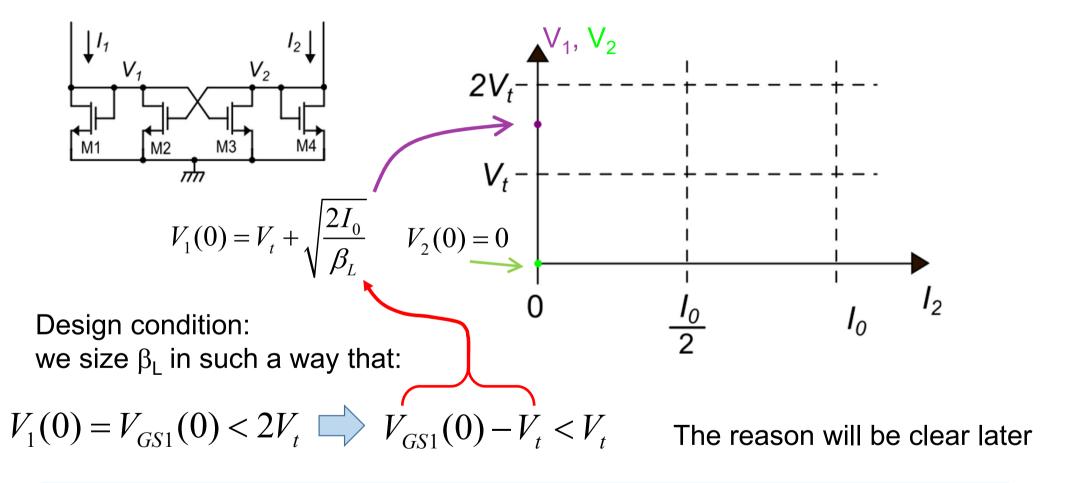

#### Analysis of the 4-transistor cell

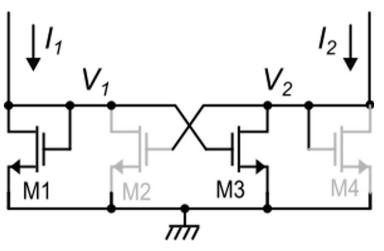

V<sub>2</sub> reaches the threshold

For  $V_2=V_t$ , M2 and M4 are still off. Then:

$I_1 = I_{D1}$   $I_2 = I_{D3}$ Since M3 is in saturation:

$$\frac{I_2}{I_1} = \frac{\beta_C}{\beta_L}$$

$$V_2 = V_t$$

Let us check whether M3 is now in saturation (was in triode region at the beginning)

$$V_{DS3} = V_2 = V_t$$

$$V_{GS3} = V_1 < V_1(0) < 2V_t$$

$$V_{GS3} - V_t < V_t = V_{DS3}$$

$$V_{DS3} > V_{GS3} - V_t$$

M3 is in saturation

V<sub>2</sub> reaches the threshold

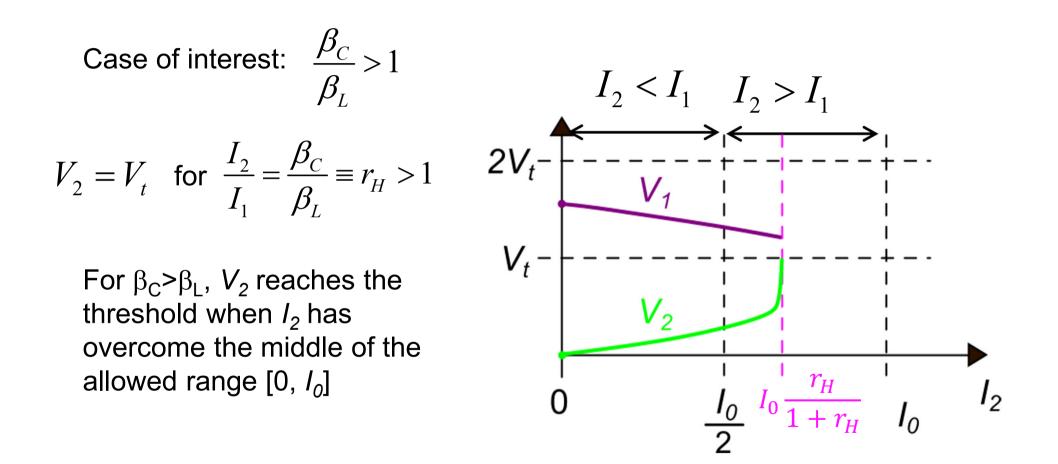

Starting from the other extreme

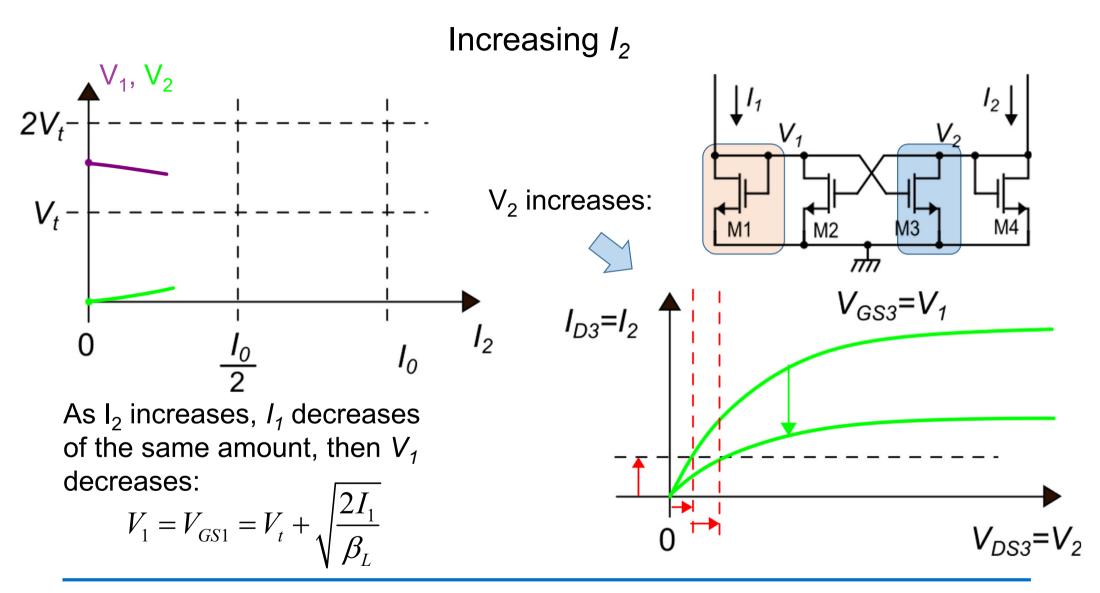

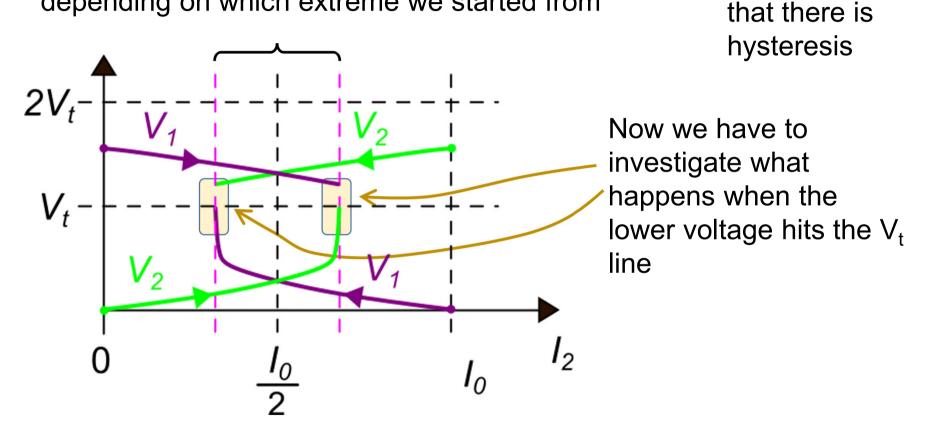

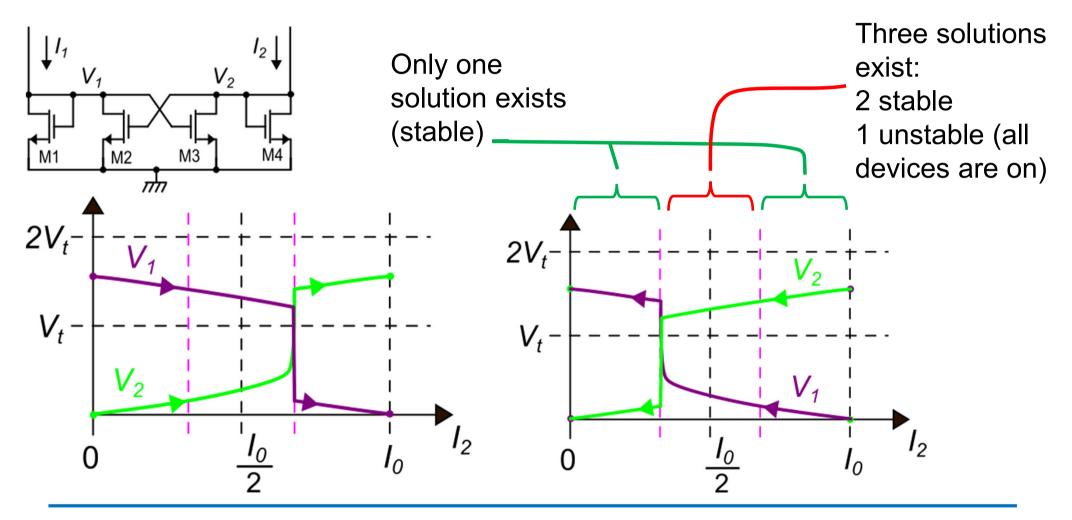

Putting the two behaviors together:

In this region, there are two possible states, depending on which extreme we started from

This means

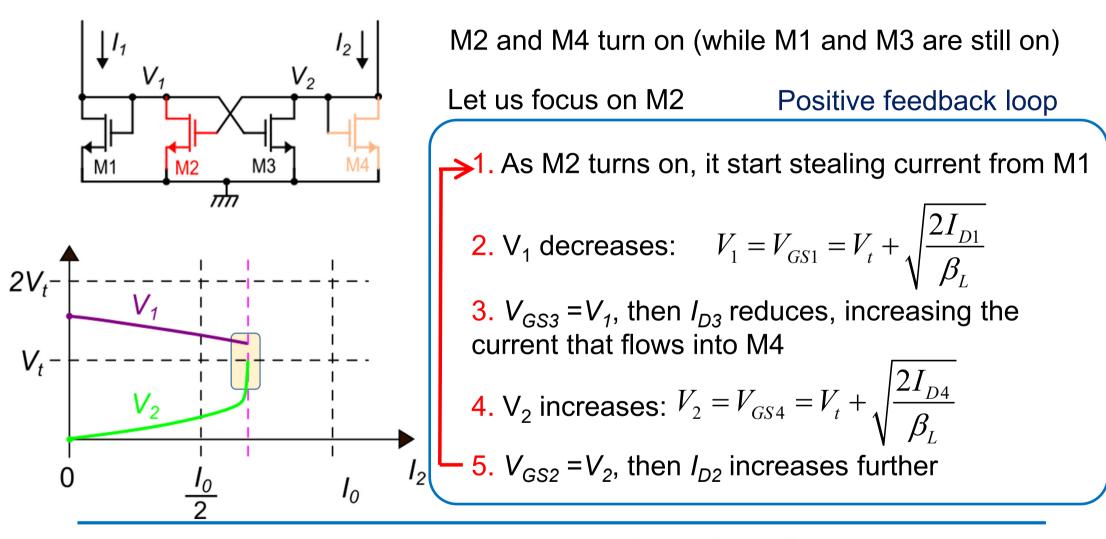

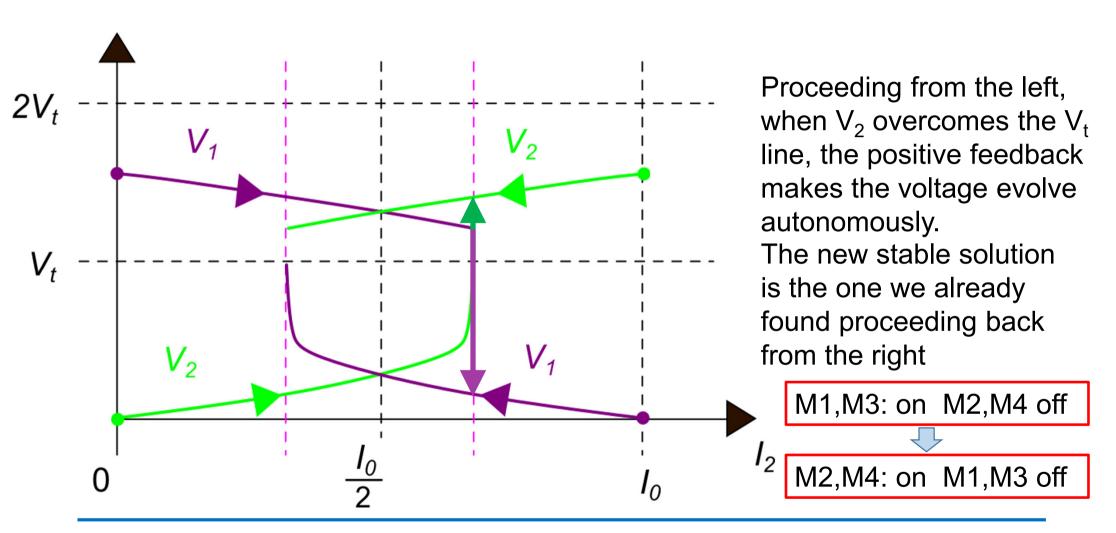

Phenomena that happen when  $V_2$  overcome  $V_t$

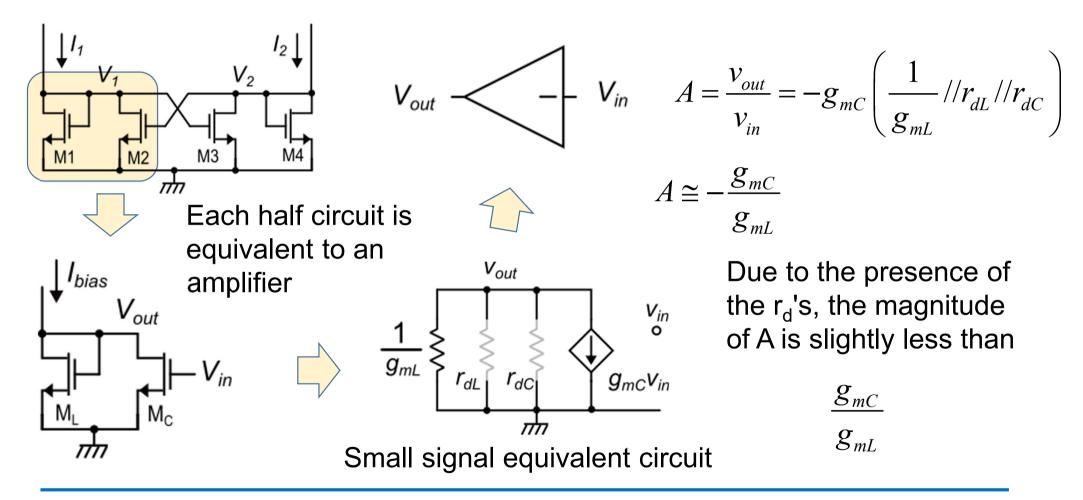

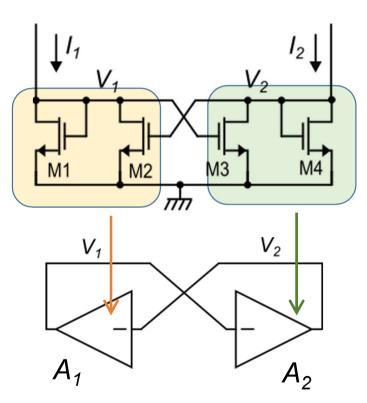

Positive feedback loop: small signal analysis

Positive feedback loop: dc instability

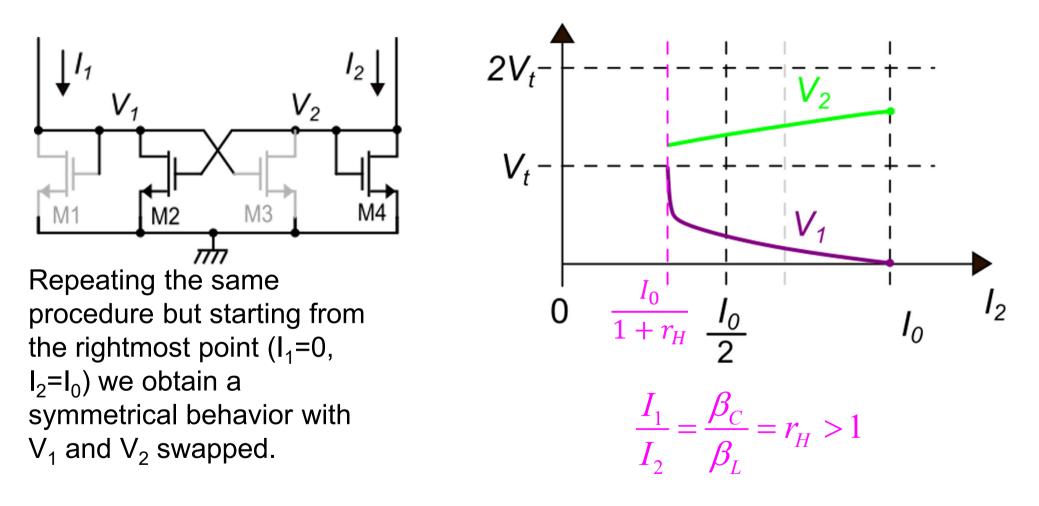

When  $V_2$  overcomes  $V_{t_1}$  all MOSFETs are on:

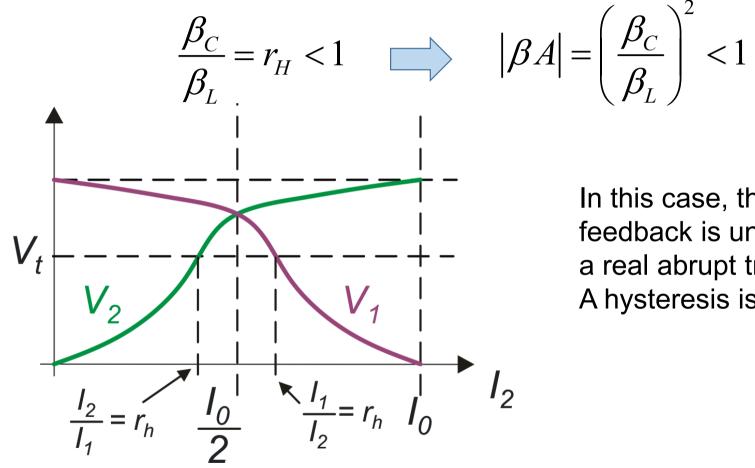

$$\begin{split} A_{1} &= -\frac{g_{m2}}{g_{m1}}; \ A_{2} = -\frac{g_{m3}}{g_{m4}}\\ \beta A &= A_{1}A_{2} > 0 \quad \text{Positive feedback}\\ g_{m1} &= \beta_{L} \left( V_{GS1} - V_{t} \right), \ g_{m2} = \beta_{C} \left( V_{GS2} - V_{t} \right)\\ g_{m3} &= \beta_{C} \left( V_{GS3} - V_{t} \right), \ g_{m4} = \beta_{L} \left( V_{GS4} - V_{t} \right)\\ V_{GS1} &= V_{GS3} = V_{1}, \ V_{GS2} = V_{GS4} = V_{2}\\ \beta A &= \frac{\beta_{C} \left( V_{2} - V_{t} \right)}{\beta_{L} \left( V_{1} - V_{t} \right)} \cdot \frac{\beta_{C} \left( V_{1} - V_{t} \right)}{\beta_{L} \left( V_{2} - V_{t} \right)} = \left( \frac{\beta_{C}}{\beta_{L}} \right)^{2} \end{split}$$

The effect of positive feedback

$$\frac{\beta_C}{\beta_L} = r_H > 1 \quad \square \quad |\beta A| > 1 \quad (\text{dc instability})$$

Therefore, a stable condition cannot exist if all MOSFETs are on.

#### Important condition

$V_1$  and  $V_2$  cannot be greater than  $V_t$  at same time in a stable condition Then, when M1 is on, M4 is off and vice versa

The "click"

P. Bruschi – Design of Mixed Signal Circuits

The two stable characteristics

P. Bruschi – Design of Mixed Signal Circuits

Non regenerative case (no hysteresis)

In this case, the positive feedback is unable to cause a real abrupt transition A hysteresis is not present

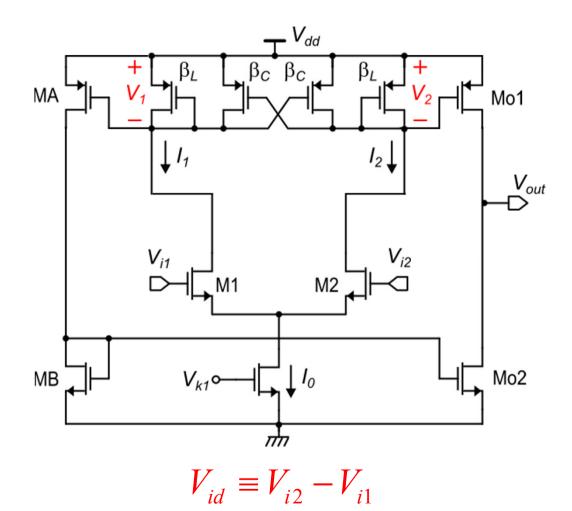

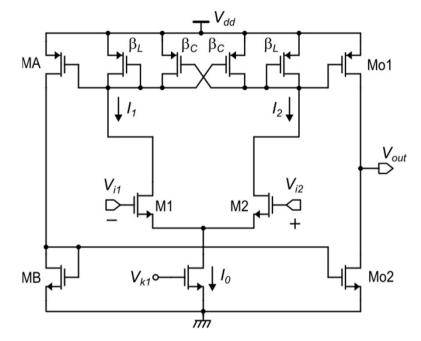

A simple comparator based on the 4-transistor hysteresis cell

We start with a p-version of the hysteresis cell

Currents  $I_1$  and  $I_2$  are derived from the input voltage  $v_{id} = v_{i2} - v_{i1}$  by means of a differential pair

Only one at a time between  $V_1$ and  $V_2$  is greater than the p-mos threshold voltage.

If  $V_1 > |V_{tp}|, V_2 < |V_{tp}| MA$ , MB and Mo2 are on, while Mo1 is off:

If  $V_2 > |V_{tp}|, V_1 < |V_{tp}|, \text{ only } V_{out} = V_{dd}$ Mo1 is on:

$V_{out} = 0$

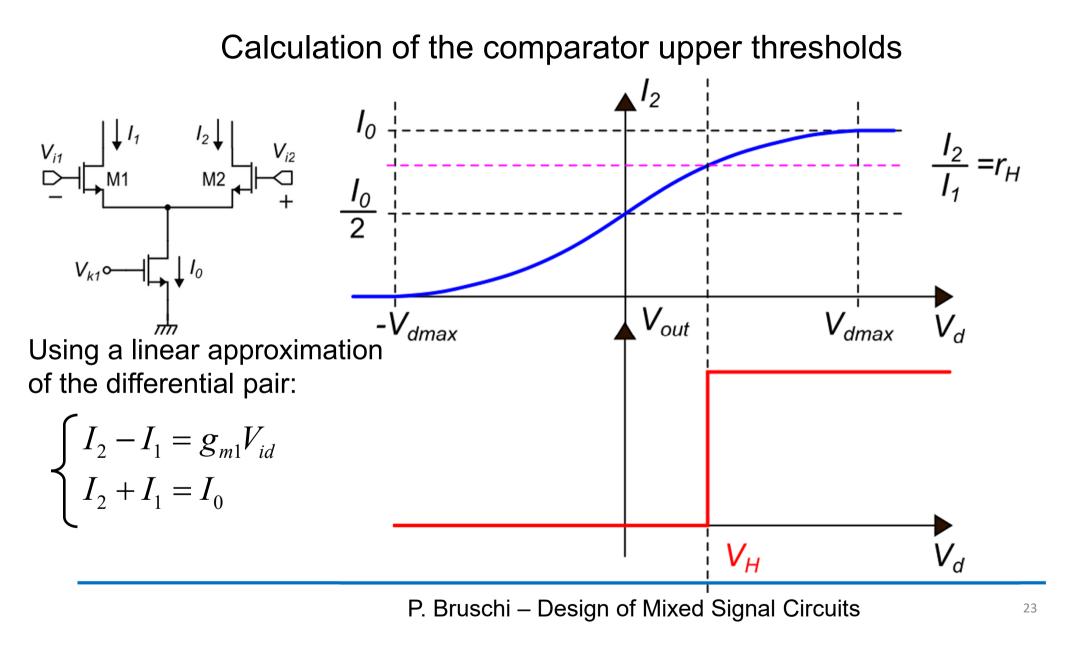

Calculation of the comparator upper thresholds

$$\begin{cases} I_{2} - I_{1} = g_{m1}V_{H} \\ I_{2} + I_{1} = I_{0} \\ I_{2} = r_{H} \end{cases} I_{2} - I_{1} = I_{1}(r_{H} - 1) = g_{m1}V_{H} \\ I_{2} + I_{1} = I_{1}(r_{H} + 1) = I_{0} \\ I_{2} = r_{H} \end{cases} \frac{r_{H} - 1}{r_{H} + 1} = \frac{g_{m1}}{I_{0}}V_{H}$$

Dividing the upper equation by the lower one

In quiescent conditions:  $I_0 = 2I_{D1-Q} = 2V_{TE1}g_{m1}$

$$\frac{r_H - 1}{r_H + 1} = \frac{1}{2V_{TE1}} V_H \qquad V_H = 2V_{TE1} \frac{r_H - 1}{r_H + 1}$$

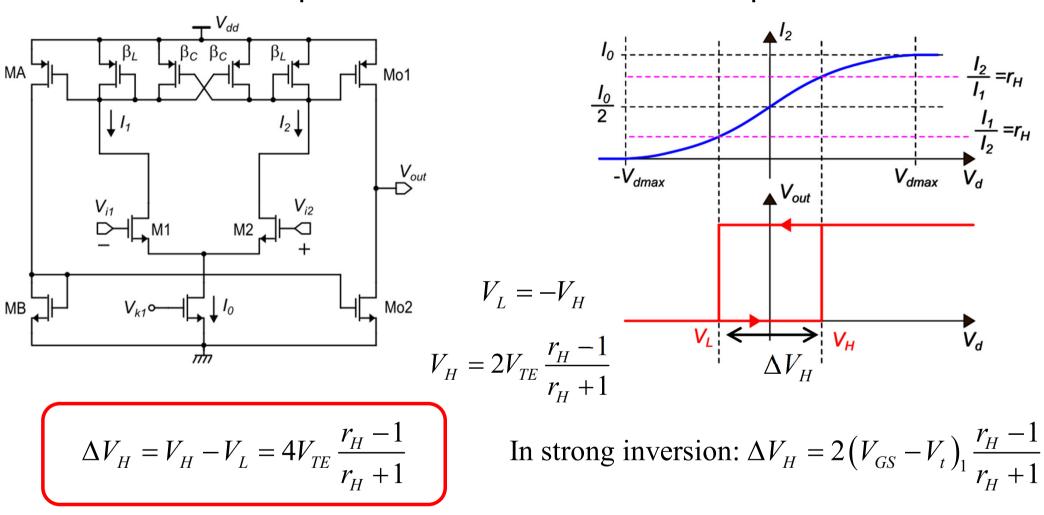

Complete characteristics of the comparator

### Minimum achievable hysteresis

$$\Delta V_{H} = V_{H} - V_{L} = 4V_{TE} \frac{r_{H} - 1}{r_{H} + 1}$$

To obtain a small hysteresis

- Make  $V_{TE1}$  as small as possible

- Make r<sub>H</sub> just slightly larger than 1

However, other requirements impose to make  $r_H$  significantly larger than 1, because:

- 1) The calculated  $|\beta A| = (r_H)^2$  is overestimated, since we have neglected the  $r_d$ 's

- Process error can make r<sub>H</sub> <1 if the margin to 1 is too small

- 3) The transition is faster with larger  $|\beta A|$

A typical robust choice:

$$r_{H} = 2 \Longrightarrow \Delta V_{H} = \frac{4}{3} V_{TE}$$

$\Delta V_{H}$  as small as **50 mV**

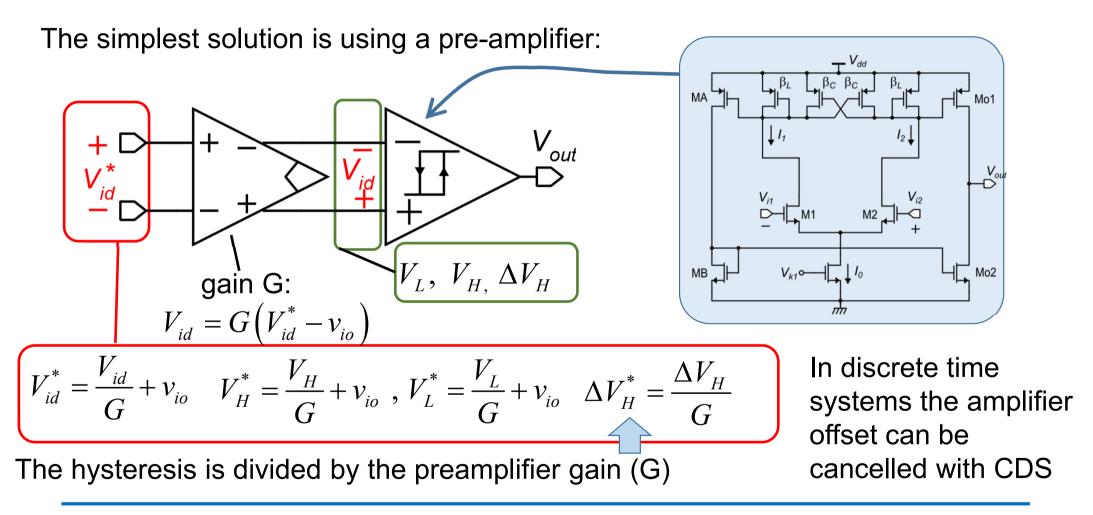

How to obtain a comparator with very low hysteresis

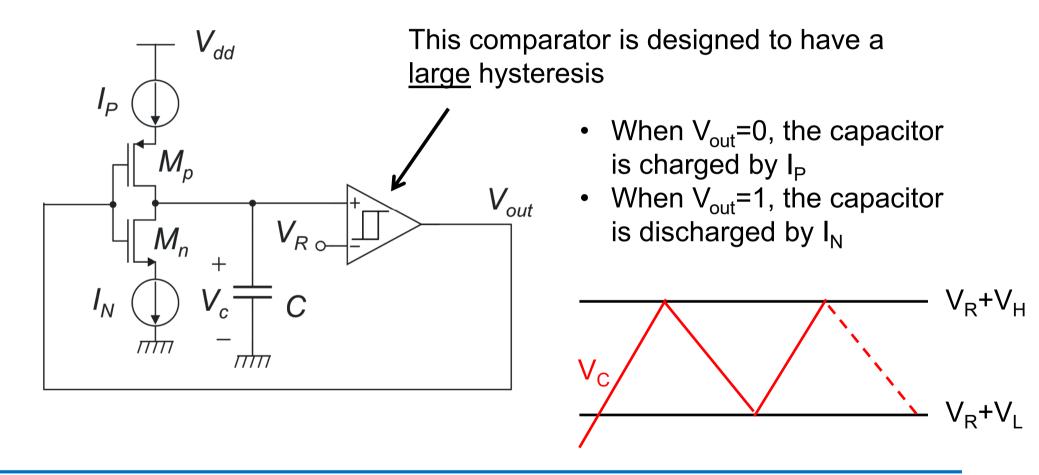

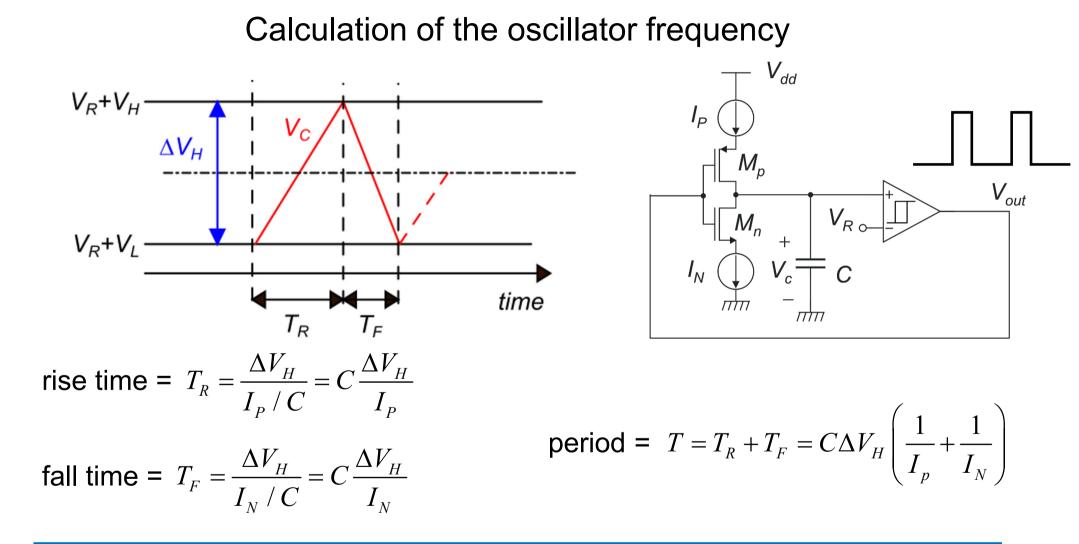

A simple low-frequency VCO based on comparator hysteresis

P. Bruschi – Design of Mixed Signal Circuits

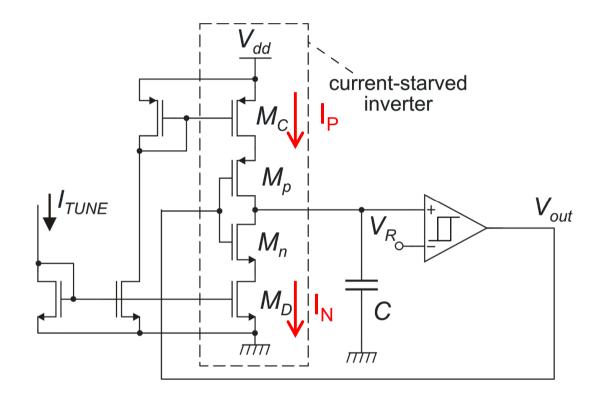

#### Implementation with "current starved" inverter

If

$$I_P = I_N = I_{tune}$$

:

$T = 2 \frac{C\Delta V_H}{I_{tune}} \quad f = \frac{I_{tune}}{2C\Delta V_H}$

The frequency is proportional to the tuning current (CCO)

Using a linear voltage to current converter it is possible to make  $I_{tune}$  to be proportional to a voltage, transforming the CCO into a VCO

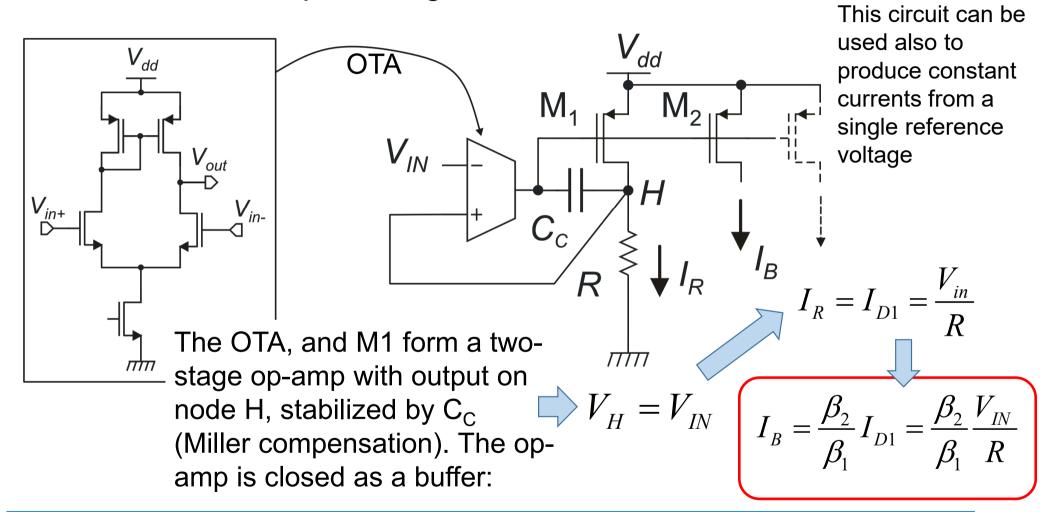

#### A simple voltage-to-current converter

P. Bruschi – Design of Mixed Signal Circuits

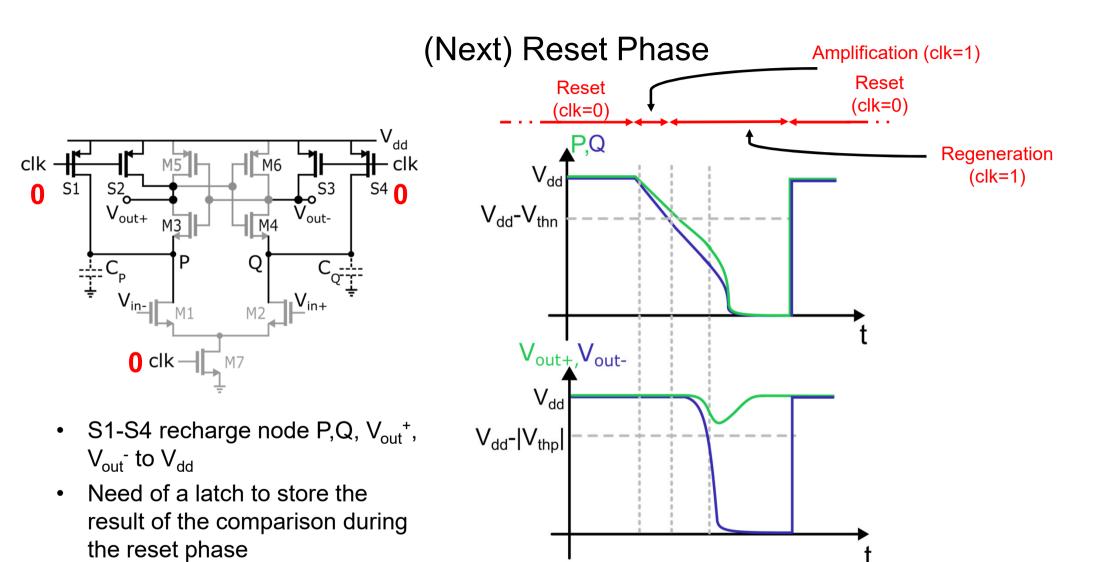

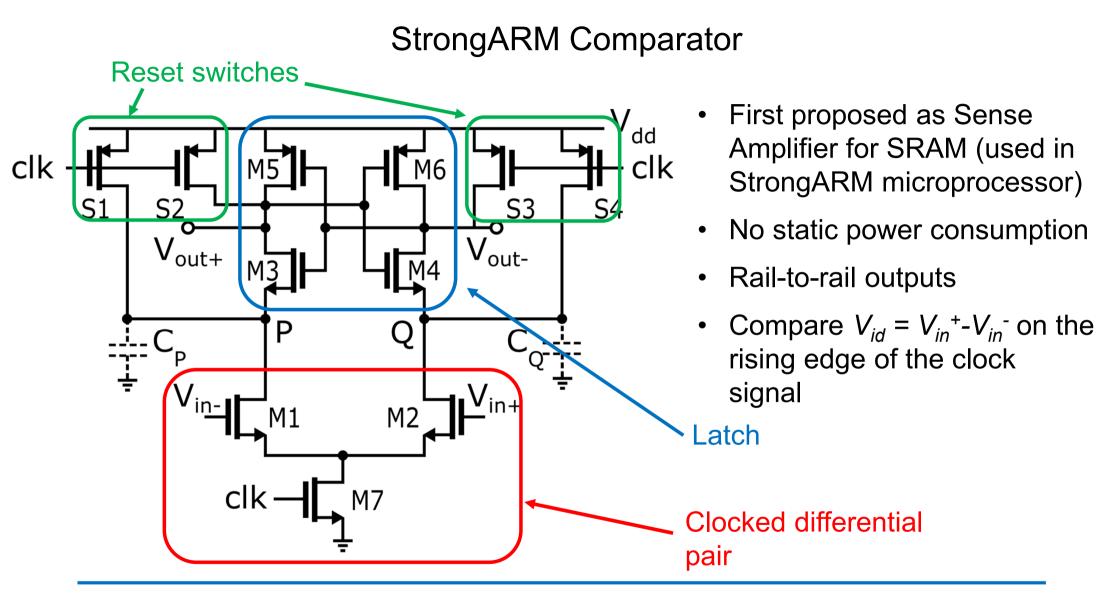

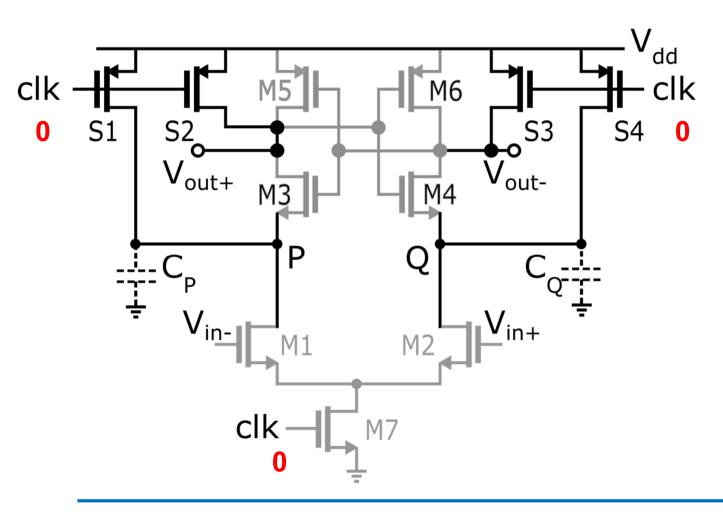

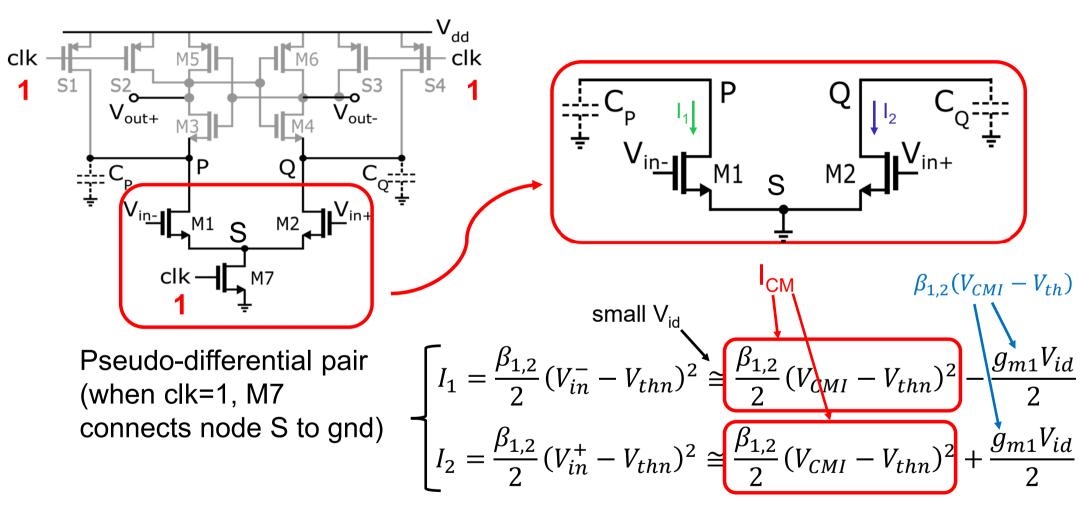

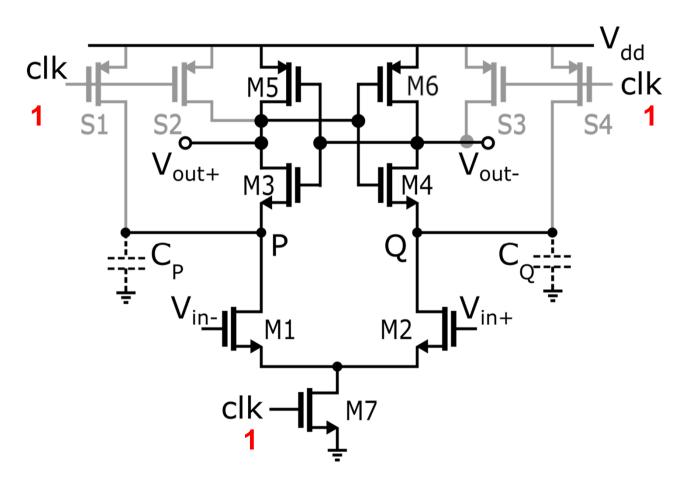

## **Reset Phase**

- Nodes P,Q, V<sub>out</sub><sup>+</sup>, V<sub>out</sub><sup>-</sup> are connected to V<sub>dd</sub> through S1-S4

- The input pair is off

- Each reset phase, the comparator loses 'memory' of the previous cycle → No hystheresis

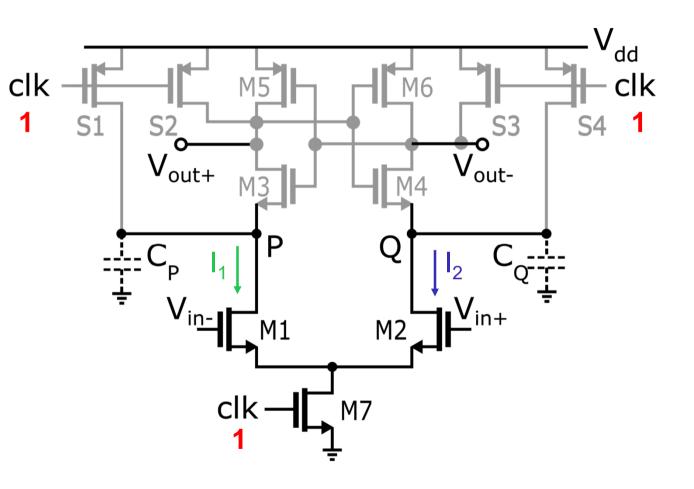

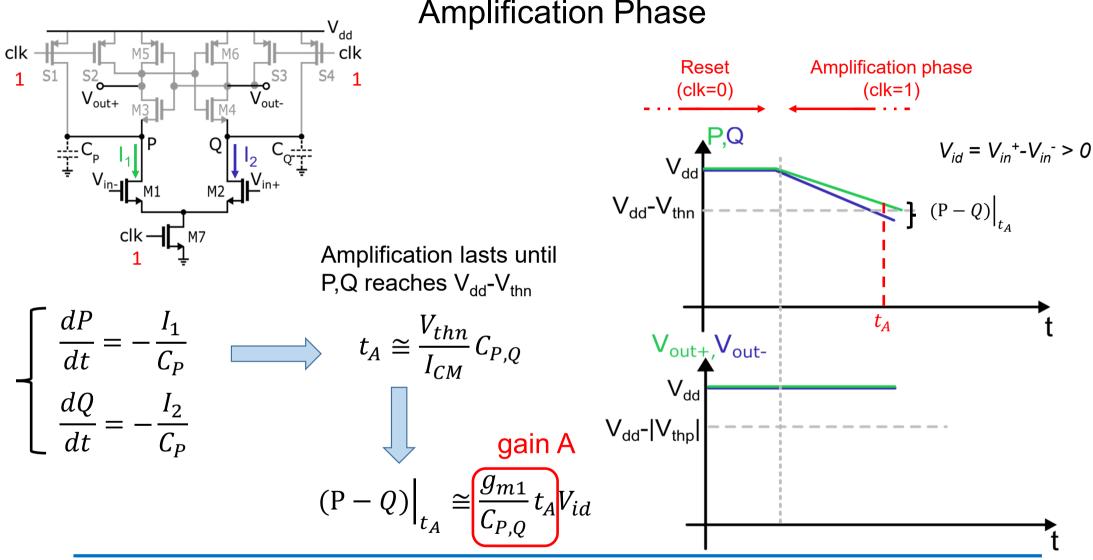

## **Amplification Phase**

- S1-S4 go off, M7 goes on

- The input pair is on

- I<sub>1</sub>, I<sub>2</sub> start discharging the parasitic capacitances C<sub>P</sub>, C<sub>Q</sub> at nodes P,Q

- Depending on V<sub>id</sub>=V<sub>in</sub><sup>+</sup>-V<sub>in</sub><sup>-</sup> node P is discharged faster/slower than node Q

**Amplification Phase**

### **Amplification Phase**

P. Bruschi – Design of Mixed Signal Circuits

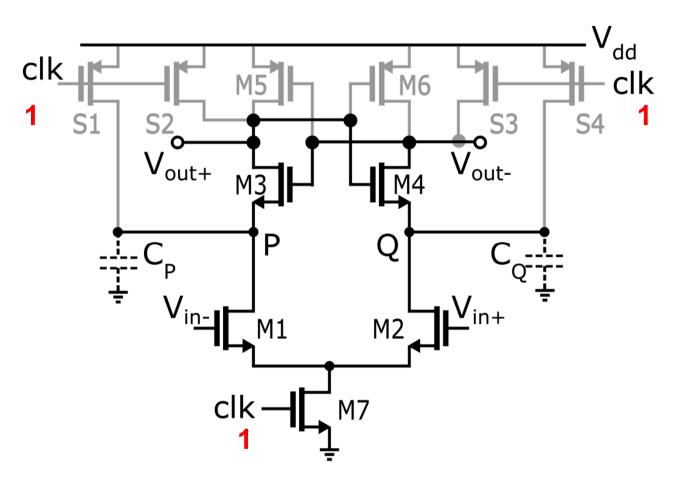

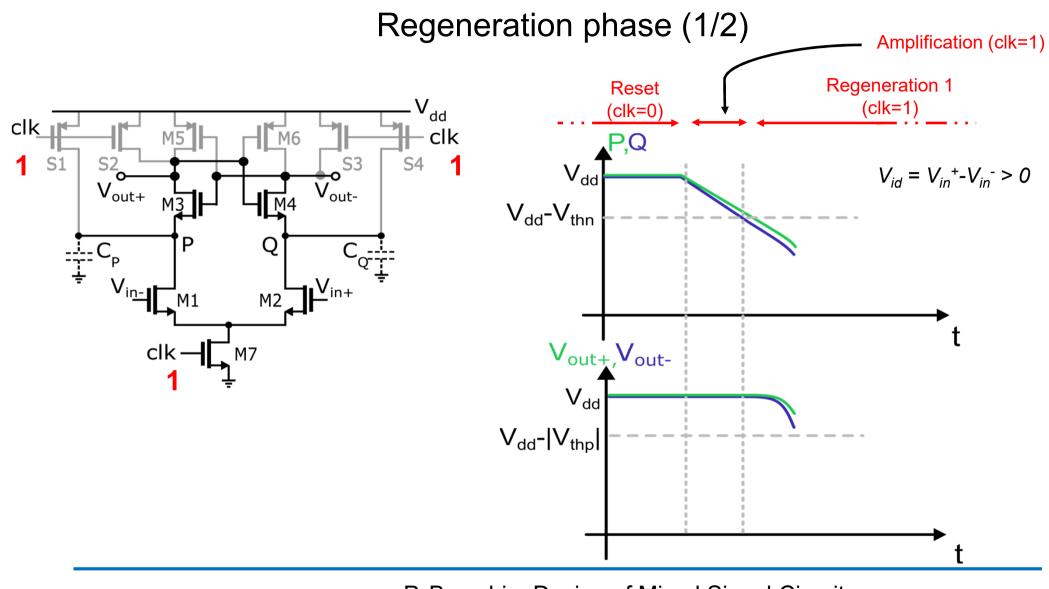

# Regeneration phase (1/2)

- When voltages at nodes P,Q go lower than V<sub>dd</sub>-V<sub>thn</sub>, M3-M4 turn on

- Cross-coupled pair M3-M4

introduces regeneration

- Nodes P,Q keep discharging and V<sub>out</sub><sup>+</sup>, V<sub>out</sub><sup>-</sup> start discharging differently according to the unbalance of P and Q

P. Bruschi – Design of Mixed Signal Circuits

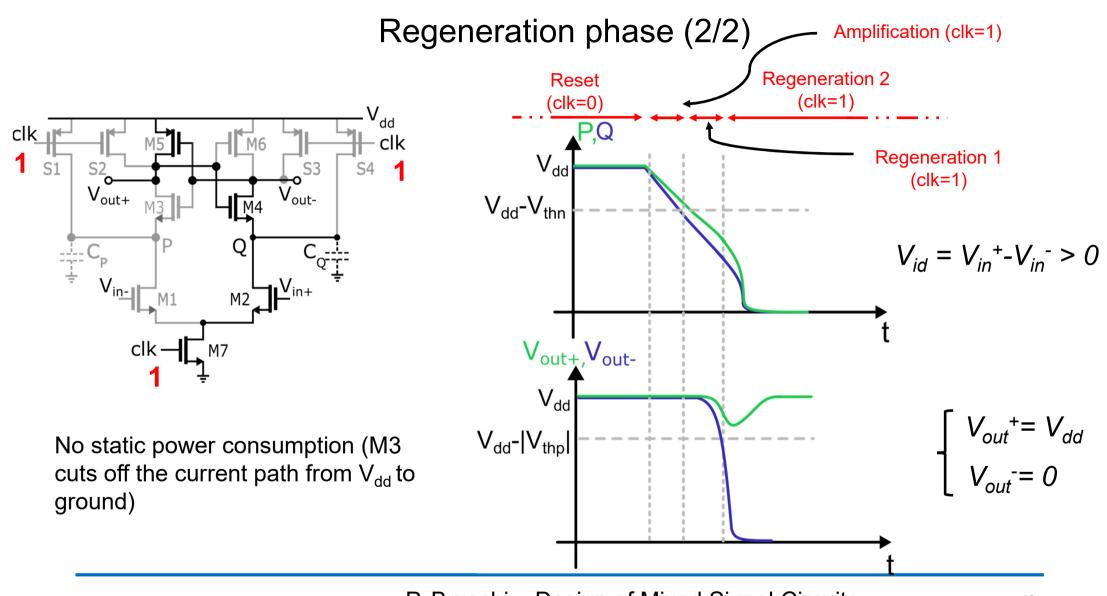

Regeneration phase (2/2)

- When V<sub>out</sub><sup>+</sup> or V<sub>out</sub><sup>-</sup> goes lower than V<sub>dd</sub>-|V<sub>thp</sub>|, one between M5 and M6 turns on

- Positive feedback of latch M3-M6 brings quickly one output to V<sub>dd</sub> and the other to ground (rail-to-rail outputs)

P. Bruschi – Design of Mixed Signal Circuits