# Mixed-Signal Design Flow and Example of SAR ADC Design

Dr. Alessandro Catania and Dr. Michele Dei

#### Mixed Signal Design Flow

Traditional mixed circuit system (e.g. interface for a MEMS sensor)

System on a chip with distribution of analog and digital units

Audio BB Video RF TV LCD Image WiFi DSP **KPD** Processor **PMU** Application Processor Comm. SIM ExM Memory PLL

Digital

Both are examples of Mixed Signal integrated circuits

#### Possible design flows

- Analog centric (or analog on top): the analog and digital units

are designed with their proper tools and integration is performed

using the analog tool.

- <u>Digital centric (or digital on top)</u>: the analog and digital units

are designed with their proper tools and integration is performed

using the (highly automated) digital tool.

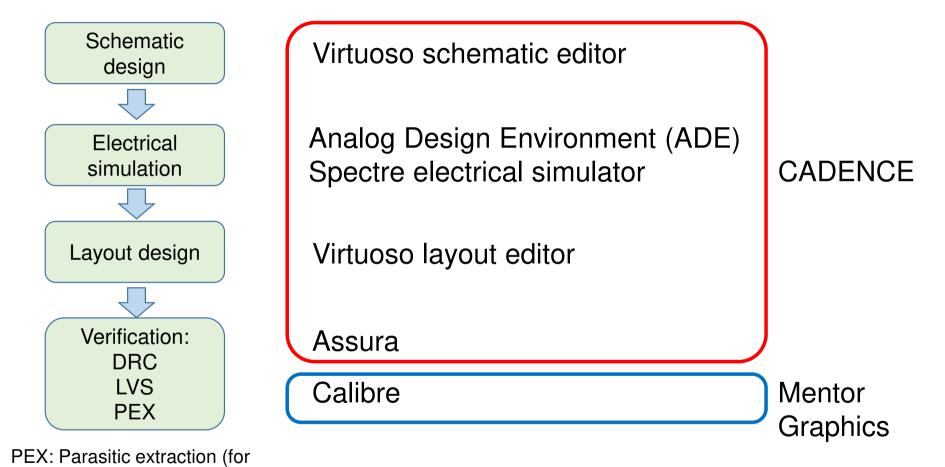

#### Analog Design Flow and examples of CAD tools

post-layout simulations)

P. Bruschi – Design of Mixed Signal Circuits

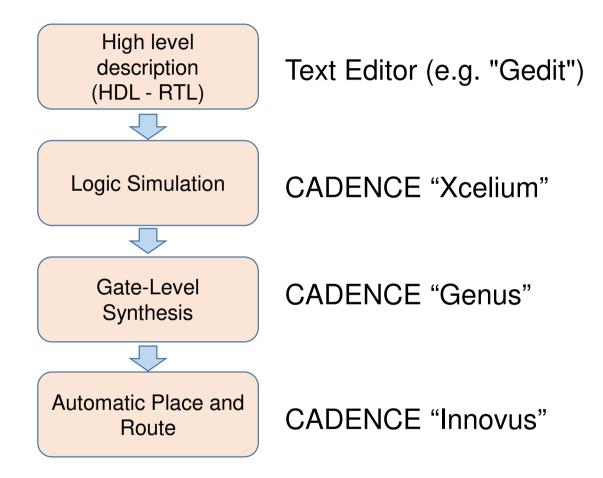

#### Digital Design Flow and CADENCE tools

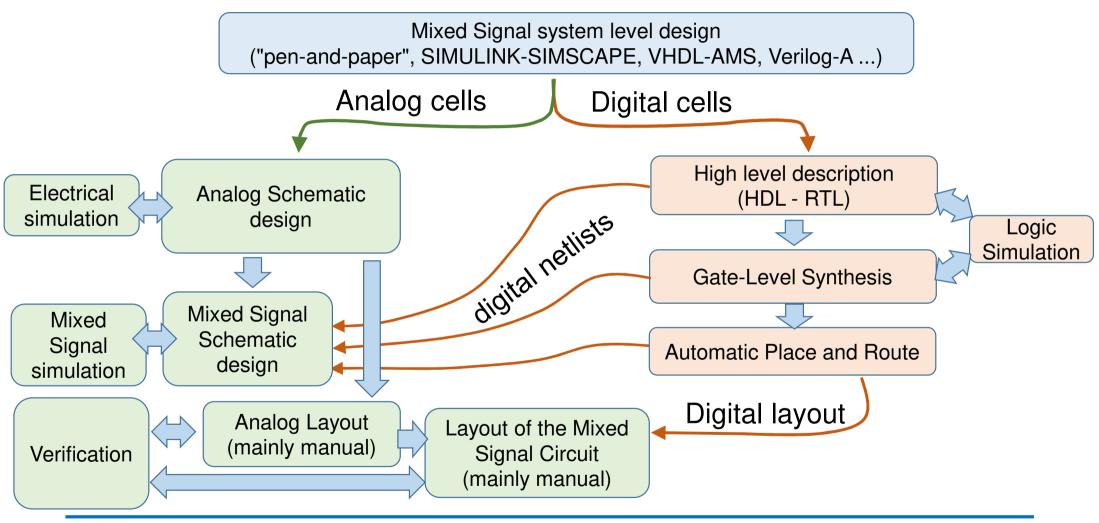

#### Mixed Signal Design Flow: Analog Centric Approach

#### An Example: Design of a SAR ADC

- High-level behavioural description of the SAR algorithm (e.g. MATLAB)

- Transistor-level design and simulations of the comparator and the DAC

- HDL description and digital simulations of the SAR control logic

- Mixed-signal simulations of the whole ADC

- Layout of the analog blocks / synthesis and place-and-route of the SAR logic

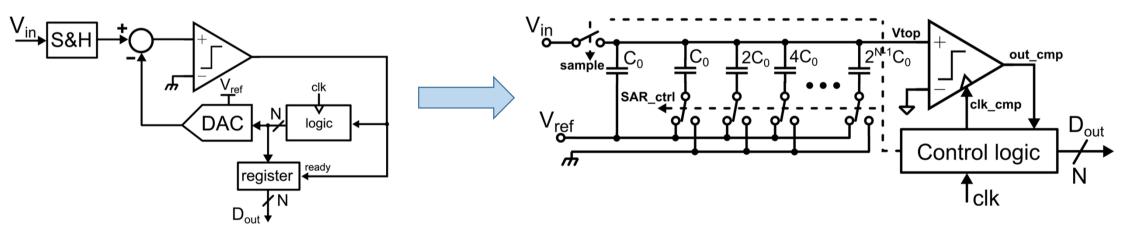

#### Successive Approximation Register ADC (6 bit)

P. Bruschi – Design of Mixed Signal Circuits

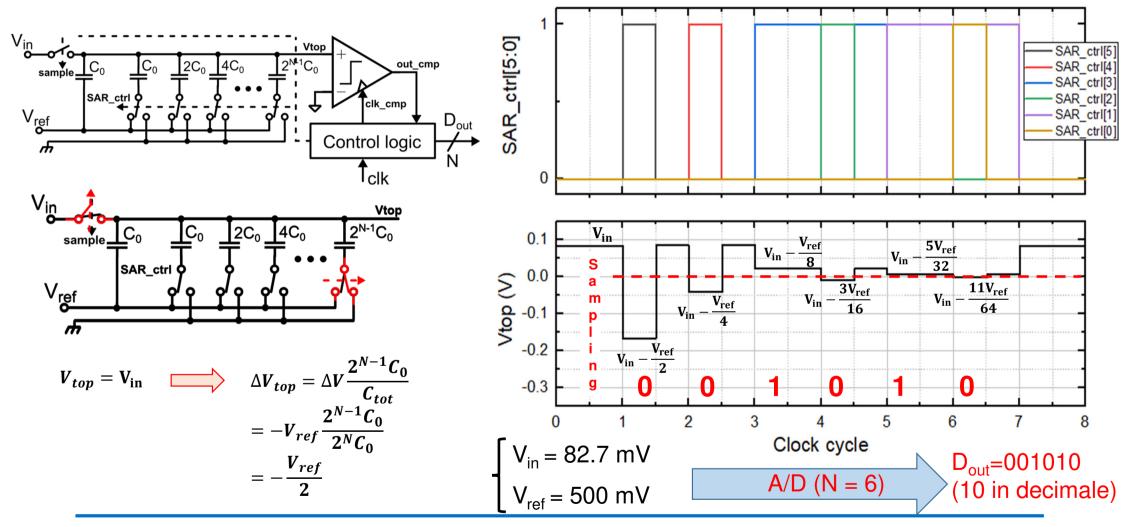

#### Behavioural description of the SAR algorithm

#### SAR algorithm:

- Signal sampling

- SAR conversion (N phases)

#### SAR phase:

- DAC update (initial guess)

- 2. Verify the comparator output

- 3. DAC correction (if needed)

P. Bruschi – Design of Mixed Signal Circuits

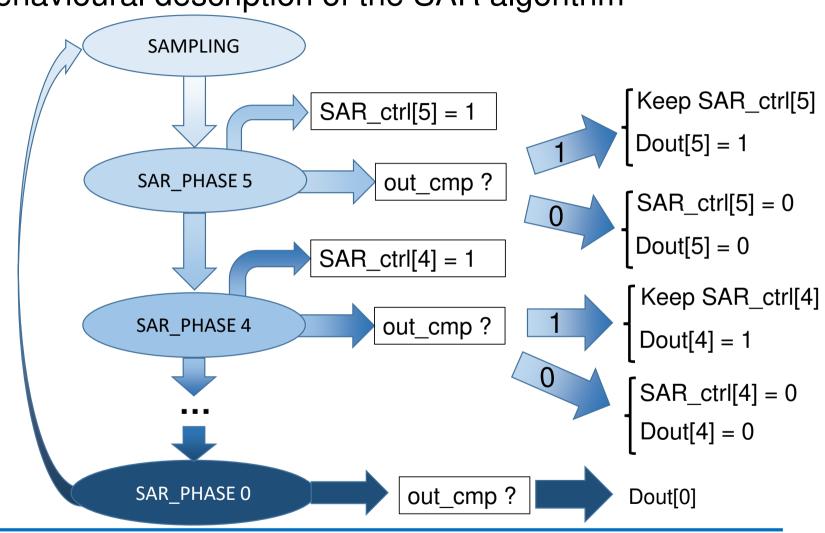

## Analog Design and Simulations (Spectre simulator)

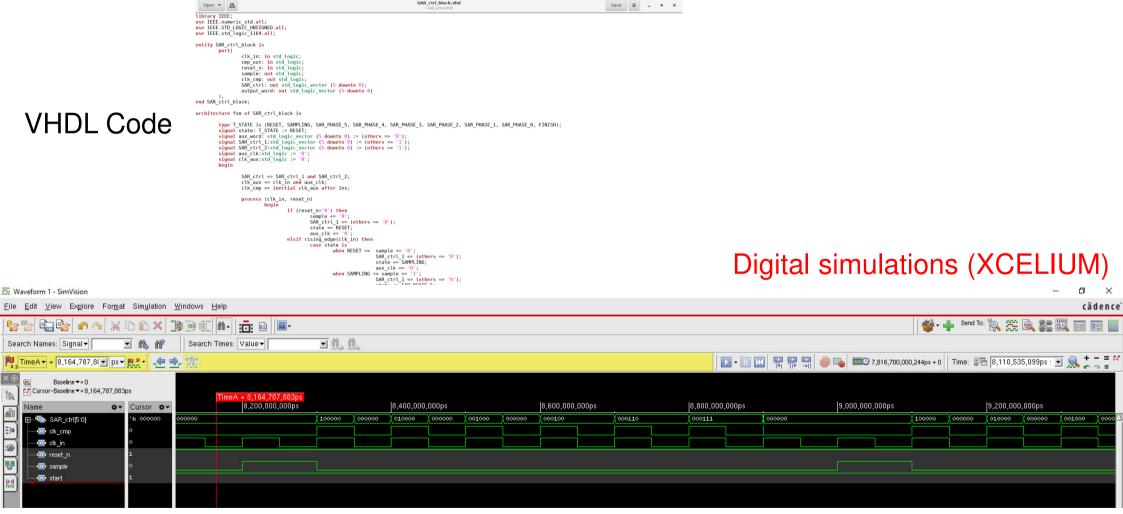

#### VHDL description of the SAR digital control block

P. Bruschi – Design of Mixed Signal Circuits

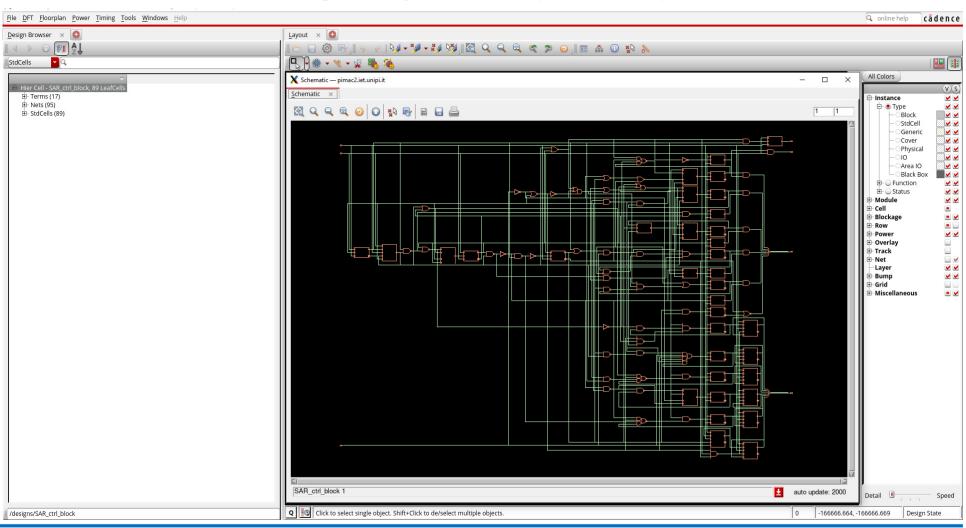

## Digital synthesis (GENUS)

P. Bruschi – Design of Mixed Signal Circuits

#### Digital synthesis (GENUS)

# RTL (Register Transfer Level) Description (GENUS input)

library IEEE;

```

use IEEE.numeric std.all:

use IEEE.STD LOGIC UNSIGNED.all:

use IEEE.std logic 1164.all;

entity SAR ctrl block is

clk in: in std logic:

cmp out: in std logic;

reset n: in std logic;

sample: out std logic;

clk cmp: out std logic;

SAR ctrl: out std logic vector (5 downto 0);

output word: out std logic vector (5 downto 0)

end SAR ctrl block;

architecture fsm of SAR ctrl block is

type T STATE is (RESET, SAMPLING, SAR PHASE 5, SAR PHASE 4, SAR PHASE 3, SAR PHASE 2, SAR PHASE 1, SAR PHASE 0, FINISH);

signal state: T STATE := RESET;

signal aux word: std logic vector (5 downto \theta) := (others => '\theta');

signal SAR ctrl 1:std logic vector (5 downto 0) := (others ⇒ '1');

signal SAR ctrl 2:std logic vector (5 downto 0) := (others ⇒ '1');

signal aux clk:std logic := '0';

signal clk aux:std logic := '0';

SAR ctrl <= SAR ctrl 1 and SAR ctrl 2;

clk aux <= clk in and aux clk;

clk cmp <= inertial clk aux after 1ns;

process (clk_in, reset_n)

if (reset n='0') then

sample \ll '0';

SAR ctrl 1 <= (others => '0');

state <= RESET;

aux clk <=

elsif rising edge(clk in) then

case state is

sample <= '0';

SAR ctrl 1 <= (others \Rightarrow '0');

state <= SAMPLING;

aux clk <= '0';

when SAMPLING => sample <= '1';

SAR ctrl 1 <= (others => '0');

```

state <= SAR PHASE 5;

# Gate Level Description (GENUS output)

```

module SAR ctrl block(clk in, cmp out, reset n, sample, clk cmp,

SAR ctrl, output word);

input clk in, cmp out, reset n;

output sample, clk cmp;

output [5:0] SAR ctrl, output word;

wire clk in, cmp out, reset n;

wire sample, clk cmp;

wire [5:0] SAR ctrl, output word;

wire [5:0] SAR ctrl 2;

wire [5:0] aux word;

wire [3:0] state;

wire [5:0] SAR ctrl 1;

wire UNCONNECTED, UNCONNECTEDO, UNCONNECTED1, UNCONNECTED2.

UNCONNECTED3, UNCONNECTED4, UNCONNECTED5, UNCONNECTED6;

wire UNCONNECTED7, UNCONNECTED8, UNCONNECTED9, UNCONNECTED10,

UNCONNECTED11, UNCONNECTED12, UNCONNECTED13, UNCONNECTED14;

wire UNCONNECTED15, UNCONNECTED16, n 0, n 1, n 2, n 3, n 5, n 6;

wire n 7, n 8, n 9, n 10, n 11, n 12, n 13, n 14;

wire n 15, n 16, n 18, n 19, n 20, n 21, n 23, n 24;

wire n_27, n_29, n_31, n_32, n_33, n_34, n_35, n_36;

wire n 37, n 38, n 39, n 40, n 41, n 42, n 43, n 44;

wire n 45, n 46, n 47, n 48, n 50, n 51, n 52, n 53;

wire n 55, n 56, n 57, n 58, n 59, n 60, n 61, n 62;

wire n 63, n 64, n 68;

DBFRBN\SAR ctrl 2 reg[2] (.RB (reset n), .CKB (clk in), .D (n 64),

.Q (SAR ctrl 2[2]), .QB (UNCONNECTED));

DBFRBN \SAR_ctrl_2_reg[4] (.RB (reset_n), .CKB (clk_in), .D (n_62),

.0 (SAR ctrl 2[41), .OB (UNCONNECTEDO));

DBFRBN \SAR ctrl 2 reg[3] (.RB (reset n), .CKB (clk in), .D (n 60),

.Q (SAR_ctrl_2[3]), .QB (UNCONNECTED1));

DBFRBN \aux word reg[4] (.RB (reset_n), .CKB (clk_in), .D (n_58), .Q

(aux word[4]), .QB (UNCONNECTED2));

DBFRBN \SAR_ctrl_2_reg[1] (.RB (reset_n), .CKB (clk in), .D (n 63),

.Q (SAR ctrl 2[1]), .QB (UNCONNECTED3));

ND3S g1595 2398(.I1 (n 56), .I2 (n 51), .I3 (n 52), .O (n 64));

DBFRBN \SAR ctrl 2 reg[5] (.RB (reset n), .CKB (clk in), .D (n 57),

.Q (SAR ctrl 2[5]), .QB (UNCONNECTED4));

OR2S g1601 5107(.I1 (n 42), .I2 (n 53), .0 (n 63));

OAI112HS g1590 6260(.A1 (n_59), .B1 (n_21), .C1 (n_50), .C2

(state[1]), .0 (n 62));

DBZRBN \output word reg[1] (.RB (reset n), .CKB (clk in), .D

(aux word[1]), .TD (output word[1]), .SEL (n 61), .Q

(output word[1]), .OB (UNCONNECTED5));

```

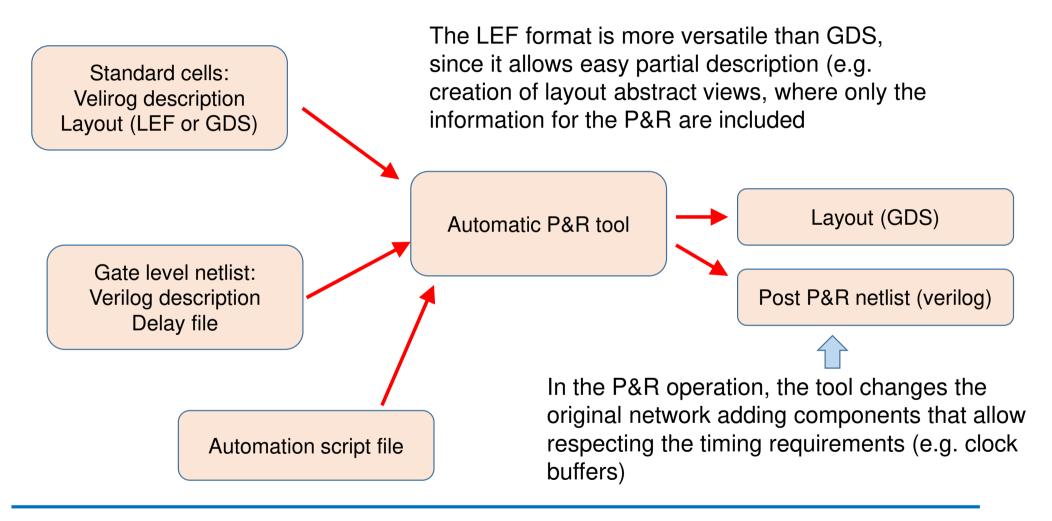

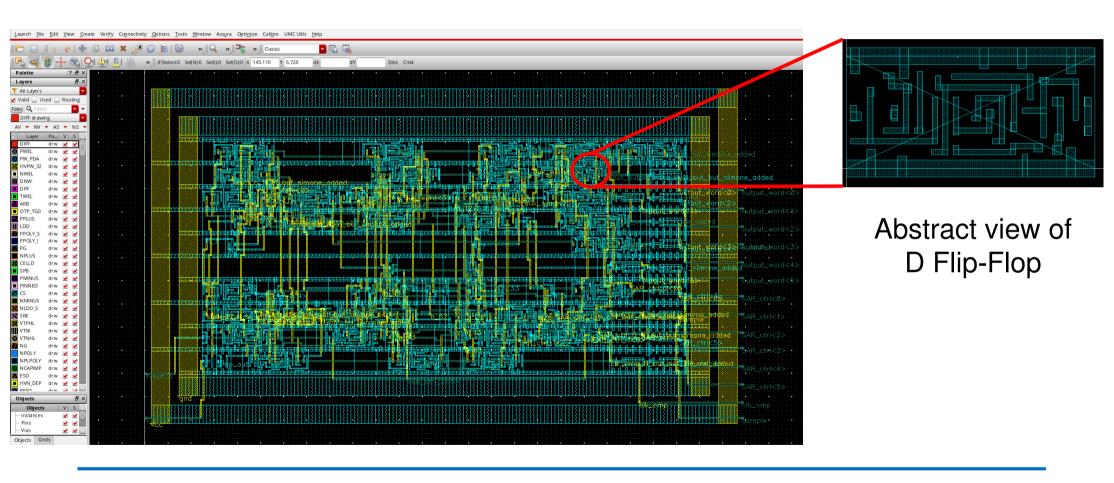

#### Automatic layout generation (Automatic Place and Route, P&R)

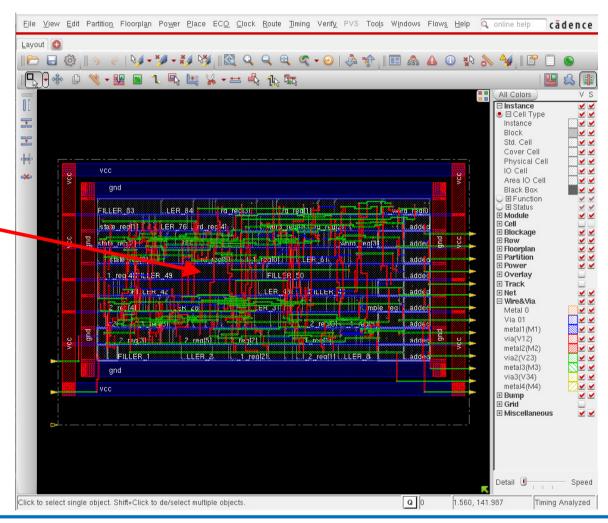

#### Automatic Place-and-Route (INNOVUS)

Empty spaces

between cells are

covered by "filler"

elements in the final

layout. Fillers

include n-wells and

other layers that

improve continuity

between cells

# Layout imported in Virtuoso

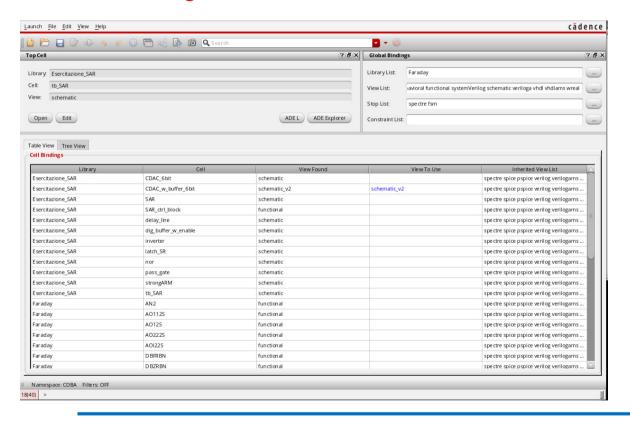

#### Mixed-Signal Simulations (ams simulator)

#### Config view of the testbench

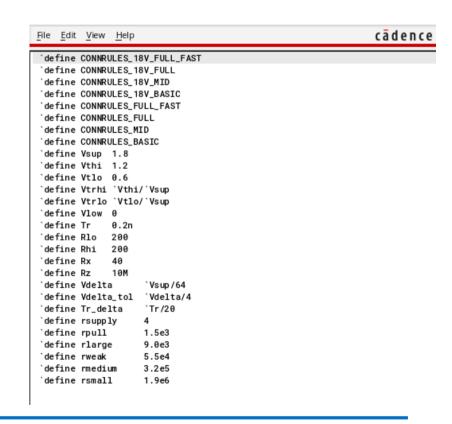

#### Connect rules

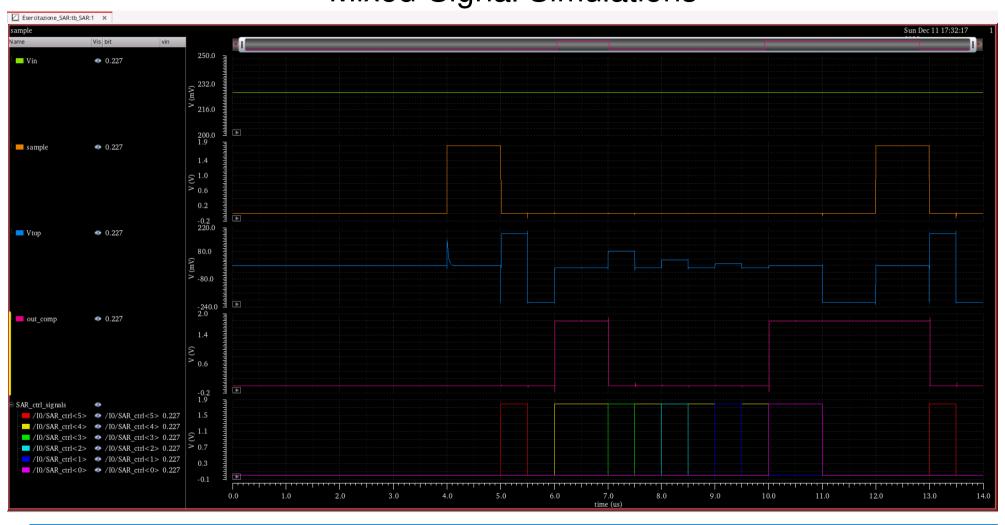

## Mixed-Signal Simulations

P. Bruschi – Design of Mixed Signal Circuits