# DAC Converters Design: Syllabus

### **General definitions**

- Applications

- Basic principles and operating electrical domains

- Performance parameters

### **Resistor-based DACs**

- R-string, R-string interpolated, and limits (DNL, INL analysis)

- R-2R ladder: binary weighting, DNL approximate analysis, configuration with a TIA.

### **Current-source (CS) based DACs**

- Unary and binary weighted CSs. DNL/INL analysis for binary scales CSs. Segmentation.

- Design for high precision: gradients due to physical processing and due to routing, solutions based on ordered element switching and calibration techniques based on current copier

### **Charge-scaling DACs**

• Charge redistribution based on parallel capacitor banks

INSIGH

# DAC Converters Design: Syllabus

### **General definitions**

- Applications

- Basic principles and operating electrical domains

- Performance parameters

### **Resistor-based DACs**

- R-string, R-string interpolated, and limits (DNL, INL analysis)

- R-2R ladder: binary weighting, DNL approximate analysis, configuration with a TIA.

### **Current-source (CS) based DACs**

- Unary and binary weighted CSs. DNL/INL analysis for binary scales CSs. Segmentation.

- Design for high precision: gradients due to physical processing and due to routing, solutions based on ordered element switching and calibration techniques based on current copier

### **Charge-scaling DACs**

• Charge redistribution based on parallel capacitor banks

**INSIGH**

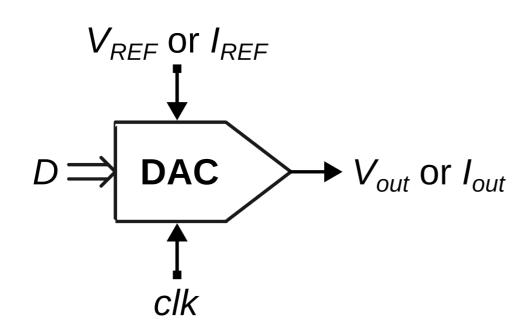

## **General definitions**

**Input:** *D*, digital code of *N* bits. If unsigned:  $[0, 2^{N}-1]$ , if two's complement:  $[-2^{N-1}, 2^{N-1} - 1]$

**Output:** analog signal (voltage or current) representing an analog equivalent of the input code, can be either single-ended or fully-differential

An analog **reference** is needed, to define the full-scale and minimum value

A clock almost always present for synchronization

Ideal voltage-output DAC:Ideal current-output DAC: $V_{out}(D) = V_{min} + \frac{V_{FS}}{2^N} \cdot D$  $I_{out}(D) = I_{min} + \frac{I_{FS}}{2^N} \cdot D$

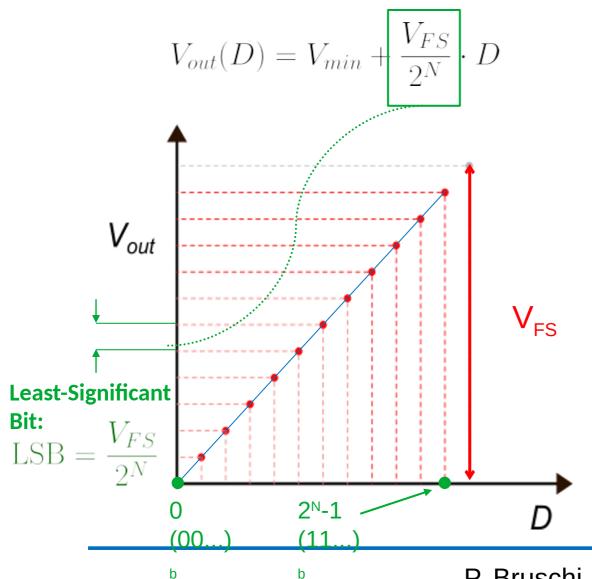

# General definitions: full-scale and LSB

### Typically in Single-Ended DACs:

- Unsigned input,

- unipolar output

- V<sub>min</sub> = 0 V (ground)

- $V_{FS} = gain * V_{REF}$

- The gain is determined by circuit implementation

### Note:

$V_{FS}$  is not available digitally, it represents the reference quantity to which  $V_{out}$  is normalized. <u>"Full-scale" is a naming convention!</u> The actual DAC output range is:  $V_{min} \leq V_{out} \leq (1 - 2^{-N})V_{FS} + V_{min}$

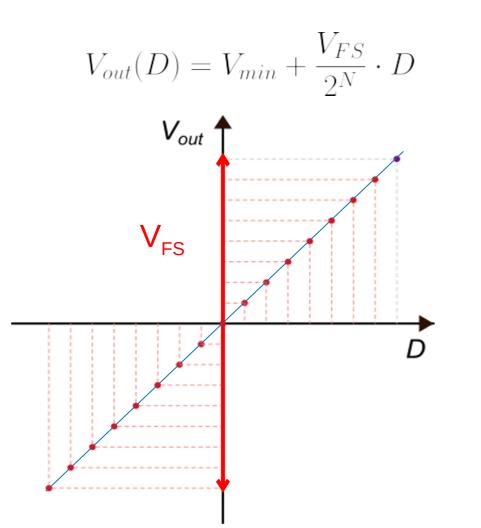

# General definitions: full-scale and LSB

### Typically in **Fully-Differential DACs**:

- Two's complement input

- Differential output

- $V_{min} = -V_{FS}/2$ , also differential valued

- Output common mode >= to V<sub>min</sub>

$$\begin{cases} V_{out,p} = V_{cmo} + \frac{V_{out}}{2} \\ V_{out,n} = V_{cmo} - \frac{V_{out}}{2} \end{cases}$$

# **DAC** Applications

ANALOG

### Digital signal reconstruction in DSP-based systems:

LED displays, Direct Digital Synthesis, Medical equipment. Often highaccuracy and high-resolution (16-20 bits) is needed

### Actuation of sensory systems

Electrochemical sensors, MEMS, antenna arrays, ultrasound actuators. Often multichannel DACs and/or High-voltage requirements (20-40 V). Compactness for low-cost devices.

### Wireless/wired communications

High-speed requirements, up to 10 GS/s. The faster, the better

#### **Embedded block for calibration or as component of an ADC** Offset nulling trimming Delta-Sigma Modulator SAR ADC Usu

Offset nulling, trimming, Delta-Sigma Modulator, SAR ADC. Usually ultra-low power requirements

# Operating electrical domains

**Fundamental functions needed in a DAC:** <u>add</u> (perform a linear combination of homogeneous quantities) and <u>select</u>

**In voltage domain:** Voltage piles up in a series of resistive elements biased at VREF, switches are controlled to tap into the desired voltage (digital potentiometer).

**In current domain:** currents adds up to a common mode (Kirchhoff law of currents). Selected currents are routed to the summing node.

**In charge domain:** pre-charged capacitors are connected together to set a final voltage resulting as (linear) combination of the individual charges

# Typical performances vs. operating mode

| Operating<br>domain | Architectures         | Accuracy                                      | Current<br>consumption<br>range | Max Speed                |

|---------------------|-----------------------|-----------------------------------------------|---------------------------------|--------------------------|

| Voltage             | Resistor string, R-2R | 8-16 bit<br>HIGH<br>RESOLUTION<br>IF TRIMMED  | 1 μA – 1 mA                     | 1 MS/s                   |

| Current             | Current sources (CS)  | 10-16 bit<br>HIGH RESOLUTION<br>IF CALIBRATED | 1 μA – 100 mA                   | 10 GS/s<br>HIGH<br>SPEED |

| Charge              | Capacitor bank        | 10-12 bit                                     | 1 nA – 10 μA<br>LOW<br>POWER    | 100 MS/s                 |

**Typical choices for different requirements: resolution, speed, power**

Higher resolution? Delta-Sigma approaches, will be discussed later on

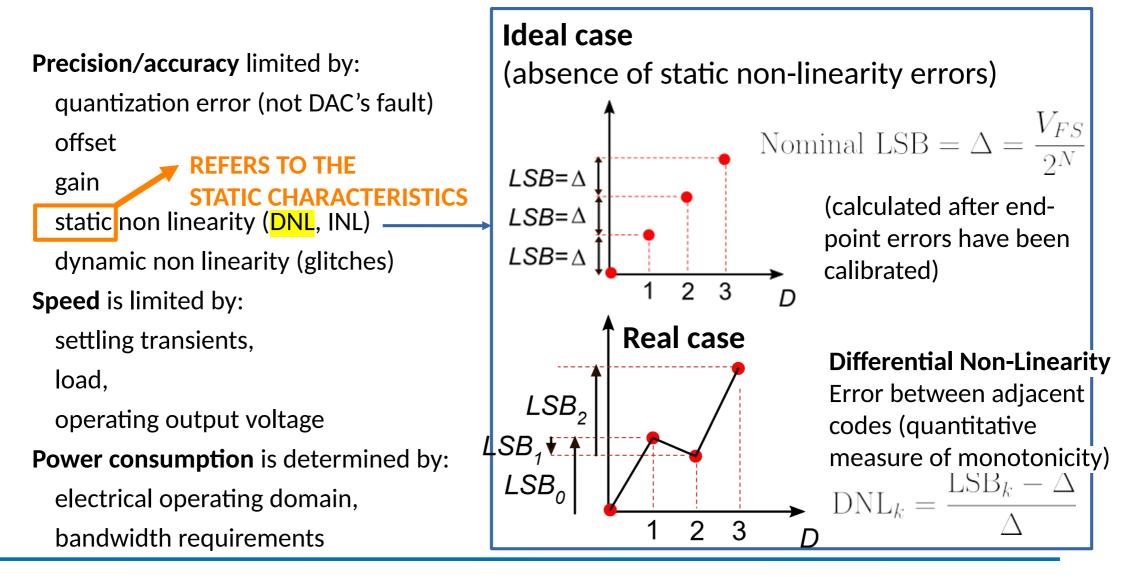

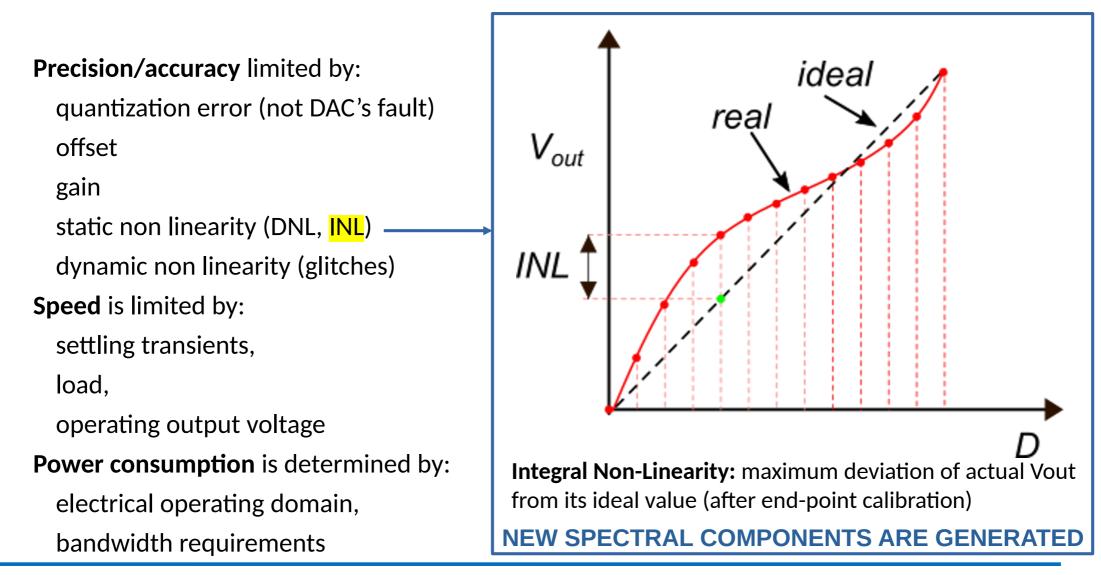

**Precision/accuracy** limited by:

quantization error (not DAC's fault) — offset

gain

static non linearity (DNL, INL)

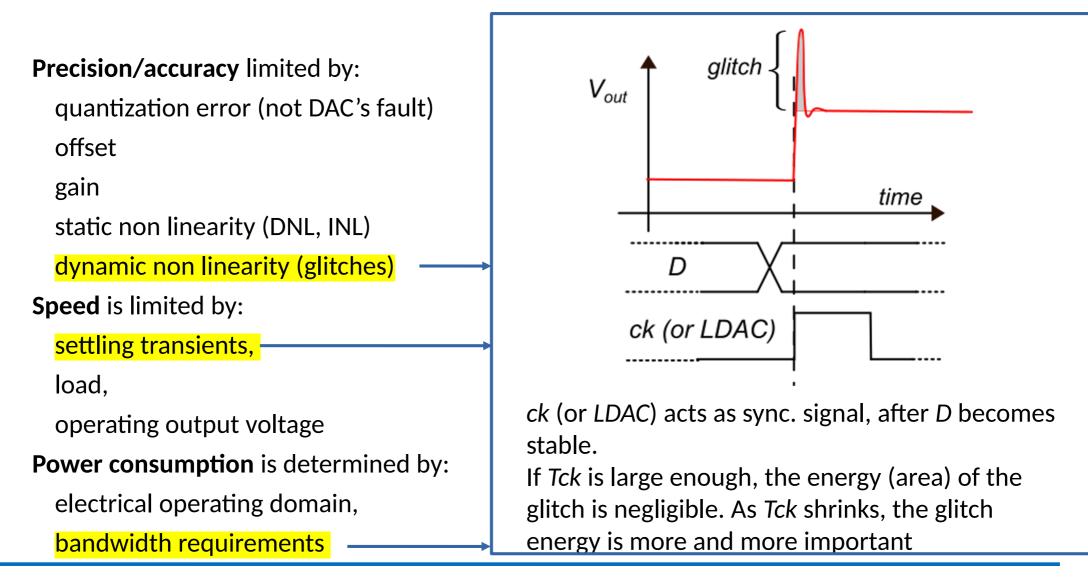

dynamic non linearity (glitches)

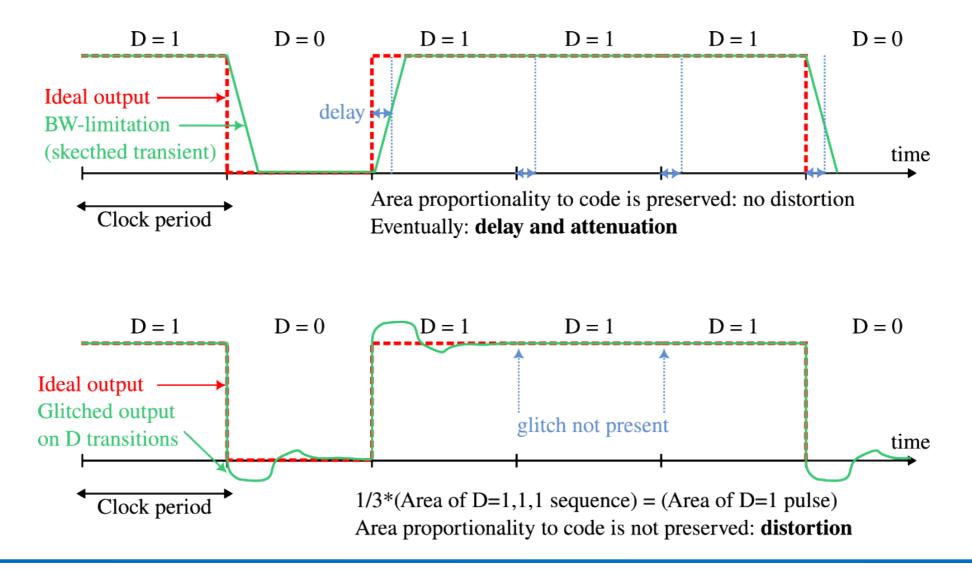

**Speed** is limited by:

settling transients,

load,

operating output voltage

**Power consumption** is determined by:

electrical operating domain,

bandwidth requirements

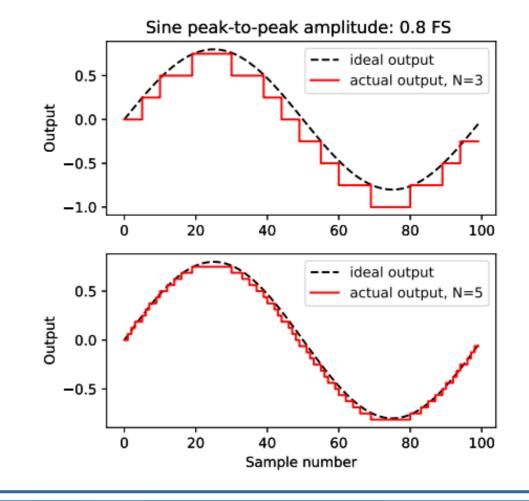

#### Ideal waveform generator:

### **Precision/accuracy** limited by:

quantization error (not DAC's fault)

#### offset

gain

static non linearity (DNL, INL)

dynamic non linearity (glitches)

**Speed** is limited by:

settling transients,

load,

operating output voltage

**Power consumption** is determined by:

electrical operating domain,

bandwidth requirements

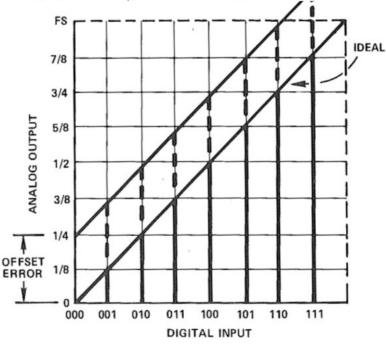

#### Offset Error

Figure 10.2 illustrates the result of offset error only. The actual transfer function is offset from the ideal by two LSBs. Any such error—either positive or negative—that affects all codes by the same amount is an *offset* error.

In most DAC testing, the offset error is measured by applying the zero-scale code (e.g. all "0"s) and measuring the output deviation from 0 volts.

#### THE DC SPECTRAL COMPONENT IS

P. Bruschi – Design of Mixed Signal Circuits

ALTERED

https://www.analog.com/en/education/education-library/analog-digital-conversion-

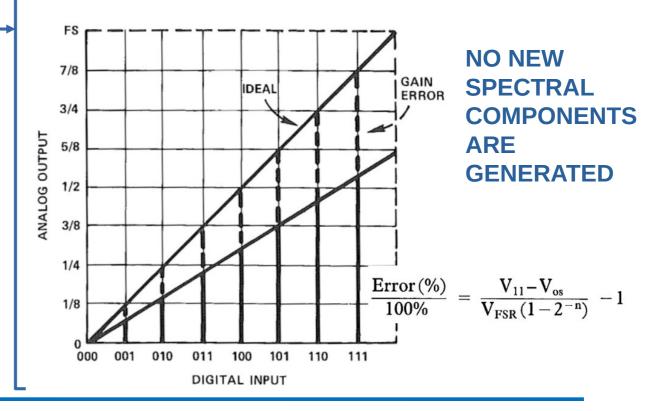

#### Gain Error

### **Precision/accuracy** limited by:

quantization error (not DAC's fault)

**END-POINT**

FRRORS

offset

gain

static non linearity (DNL, INL) dynamic non linearity (glitches)

**Speed** is limited by:

settling transients,

load,

operating output voltage

**Power consumption** is determined by:

electrical operating domain,

bandwidth requirements

Figure 10.3 shows the effect of a gain error only. The ideal transfer function has a slope defined by drawing a straight line through the two end points. The slope represents the gain of the transfer function. In real DACs, this slope can differ from the ideal, resulting in a *gain* error—which is usually expressed as a percent because it affects each code by the same percentage.

P. Bruschi – Design of Mixed Signal Circuits

https://www.analog.com/en/education/education-library/analog-digital-conversion-

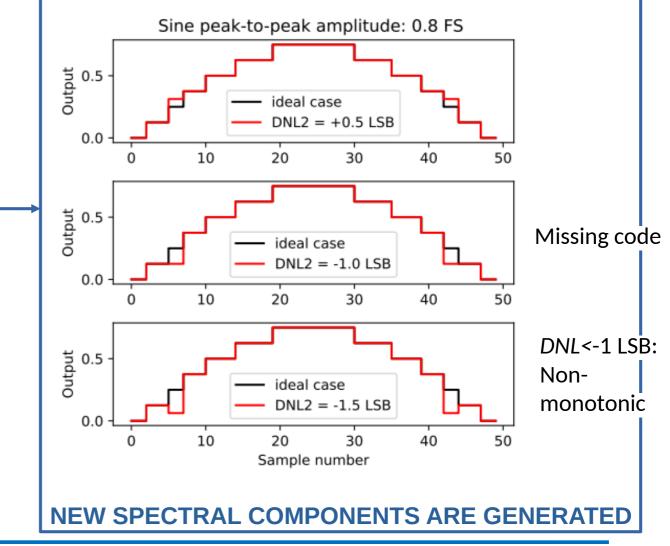

$$\mathrm{DNL}_k = \frac{\mathrm{LSB}_k - \Delta}{\Delta}$$

**Precision/accuracy** limited by:

quantization error (not DAC's fault) offset

gain

static non linearity (<mark>DNL</mark>, INL)

dynamic non linearity (glitches)

**Speed** is limited by:

settling transients,

load,

operating output voltage

**Power consumption** is determined by:

electrical operating domain,

bandwidth requirements

# DAC Converters Design: Syllabus

### **General definitions**

- Applications

- Basic principles and operating electrical domains

- Performance parameters

### Resistor-based DACs

- R-string, R-string interpolated, and limits (DNL, INL analysis)

- **R-2R ladder: binary weighting,** DNL approximate analysis, **configuration with a TIA. Current-source (CS) based DACs**

- Unary and binary weighted CSs. DNL/INL analysis for binary scales CSs. Segmentation.

- Design for high precision: gradients due to physical processing and due to routing, solutions based on ordered element switching and calibration techniques based on current copier

### **Charge-scaling DACs**

• Charge redistribution based on parallel capacitor banks

**INSIGH**

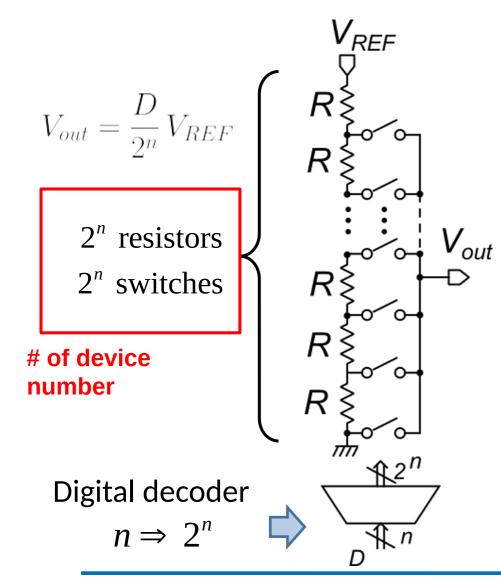

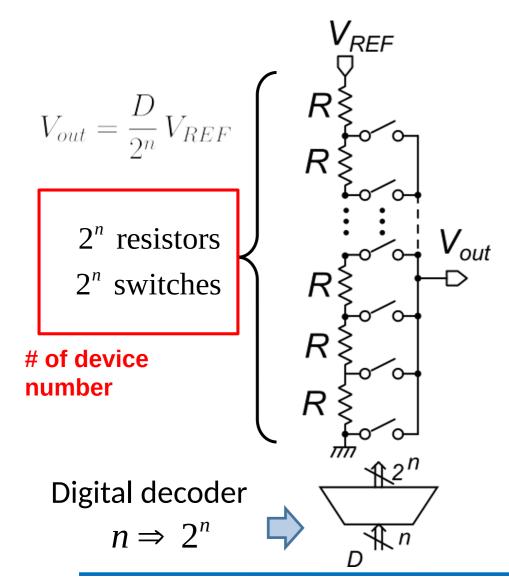

# R-String DAC

### First idea:

Lord Kelvin in the mid-1800s, implemented using resistors and relays

• The string operates as **voltage divider** at each tap:

$$V_{tap} = \frac{R_{down}}{R_{down} + R_{up}} V_{REF}$$

- The accuracy of the partition voltage do depends on how well each resistor is matched to the others, not on the absolute accuracy of each resistor.

- Resistors constructed on the same substrate, deposited and processed together: inherent matching accuracy advantage over discrete solutions.

# R-String DAC

### Operation

- For any value of code D, only one switch at a time is on, selecting one of the 2<sup>N</sup> voltage levels produced by the resistive voltage divider

- If code D turns on a certain switch, code D+1 turns on the switch placed in position up, then the output voltage can only grow

- The monotonicity is guaranteed, |DNL| < 1 LSB

- Usually followed a unity gain buffer to avoid string loading (however, opamp offset and noise are now to be considered)

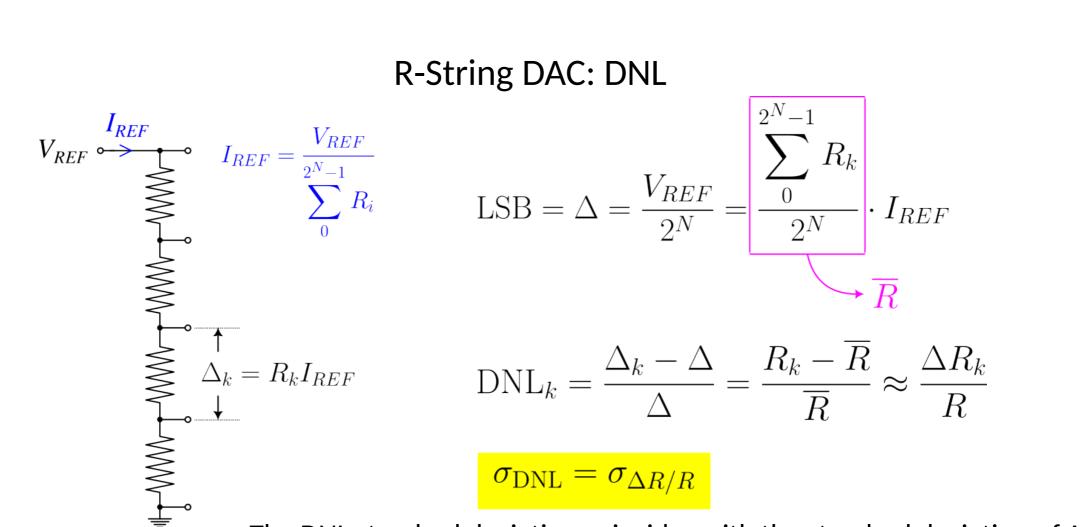

- The DNL standard deviation coincides with the standard deviation of ΔR/R (element mathing): guaranteed monotonicity

- DNL does not dependent of resolution (N)

- DNL does not depend on absolute value of R

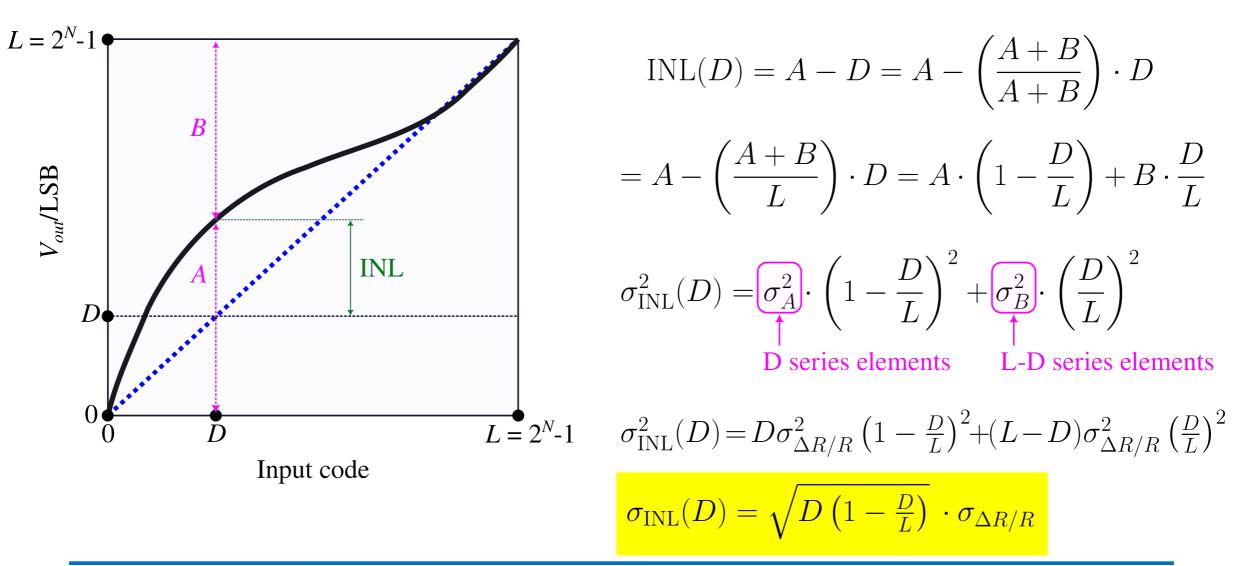

**R-String DAC: INL**

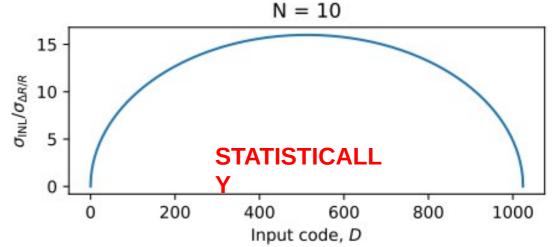

# **R-String DAC: INL**

$$\sigma_{\text{INL}}(D) = \sqrt{D\left(1 - \frac{D}{L}\right)} \cdot \sigma_{\Delta R/R}$$

The INL standard deviation is maximum at half code  $\sigma_{\text{INL,max}} = \frac{\sqrt{L}}{2} \cdot \sigma_{\Delta R/R} \approx 2^{N/2-1} \cdot \sigma_{\Delta R/R}$

The INL standard deviation depends on the DAC

**resolution: Design case:** relative std. deviation of resistors 1%, what is the maximum number of bits for INL standard deviation < 0.1 LSB?

$$N < 2 + 2\log_2 \frac{\sigma_{\text{INL,max}}}{\sigma_{\Delta R/R}} = 2 + 2\log_2 \frac{0.1}{0.01} \approx 8.6$$

Very expensive to reach resolution higher than 10 bit with R-string architecture: routing!

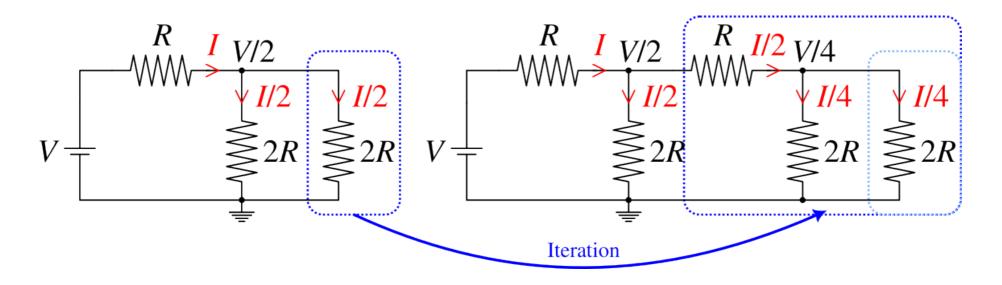

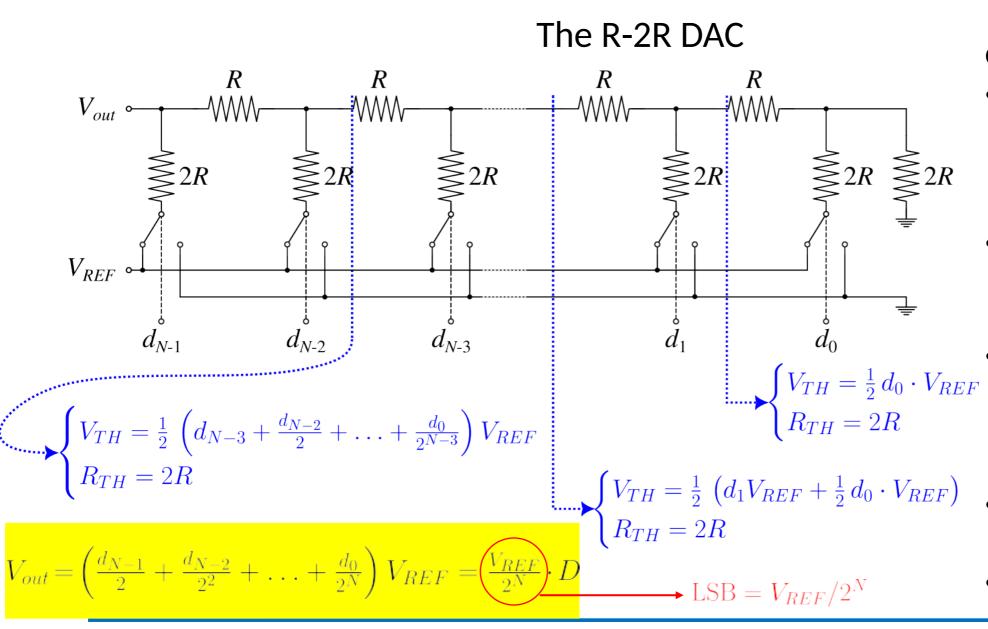

# The R-2R ladder

- The simple R-2R ladder provides a **voltage and a current scaling by 2**

- One of the 2R can be substituted instantiating another ladder, this way by iteration a **binary scaling** is obtained: <u>relaxed routing with respect to R-String</u>

- If iterated N times, the total number of unit resistors will be N×3+2 (the last 2 is due to the final termination 2R element)

### **Operation:**

- Thevenin equivalent from LSB section, moving then towards MSB

- At each section a ½ scaling is introduced (nominally)

- As in R-string the scaling depends on resistive voltage dividers

- Output voltage is binary weighted

- Current consumption

P. Bruschi – Design of Mixed Signal Circuits

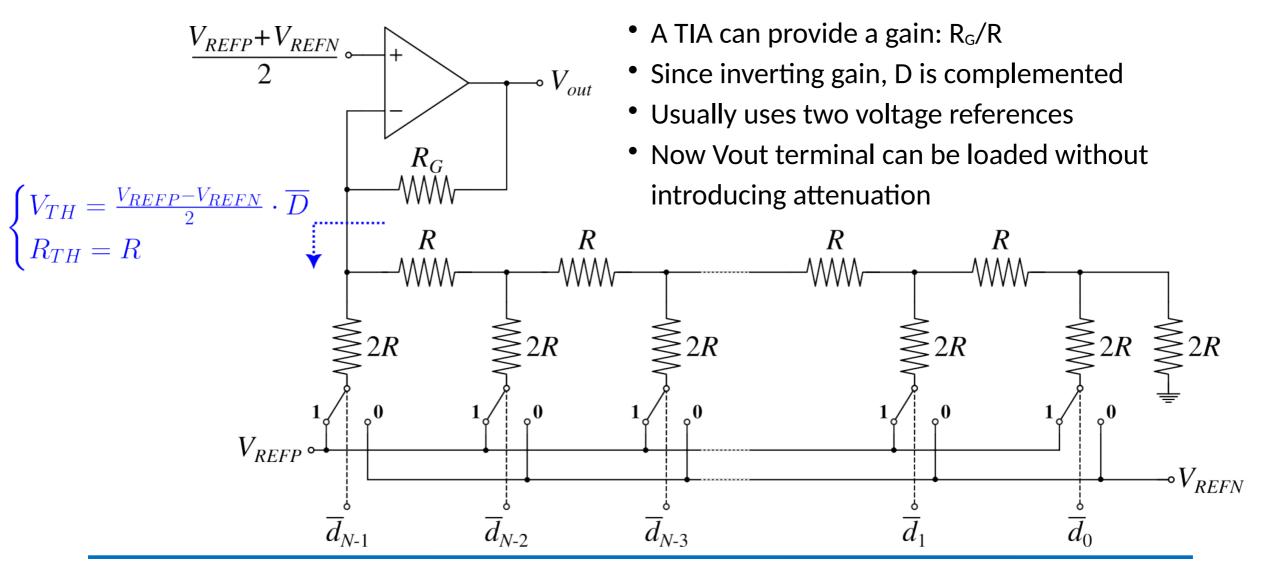

# The R-2R DAC, TIA configuration

P. Bruschi – Design of Mixed Signal Circuits

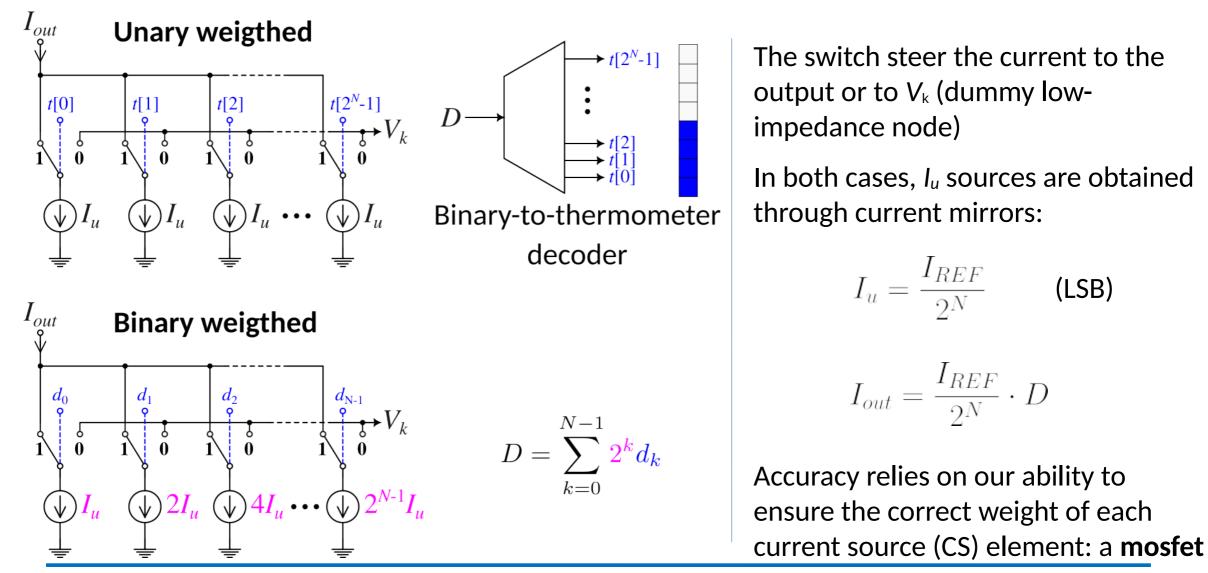

# CS DAC: Unary and Binary Weighted

# DAC Converters Design: Syllabus

### **General definitions**

- Applications

- Basic principles and operating electrical domains

- Performance parameters

### **Resistor-based DACs**

- R-string, R-string interpolated, and limits (DNL, INL analysis)

- R-2R ladder: binary weighting, DNL approximate analysis, configuration with a TIA. **Current-source (CS) based DACs**

### • Unary and binary weighted CSs. DNL/INL analysis for binary scales CSs. Segmentation.

• Design for high precision: gradients due to physical processing and due to routing, solutions based on ordered element switching and calibration techniques based on current copier

### **Charge-scaling DACs**

• Charge redistribution based on parallel capacitor banks

**INSIGH**

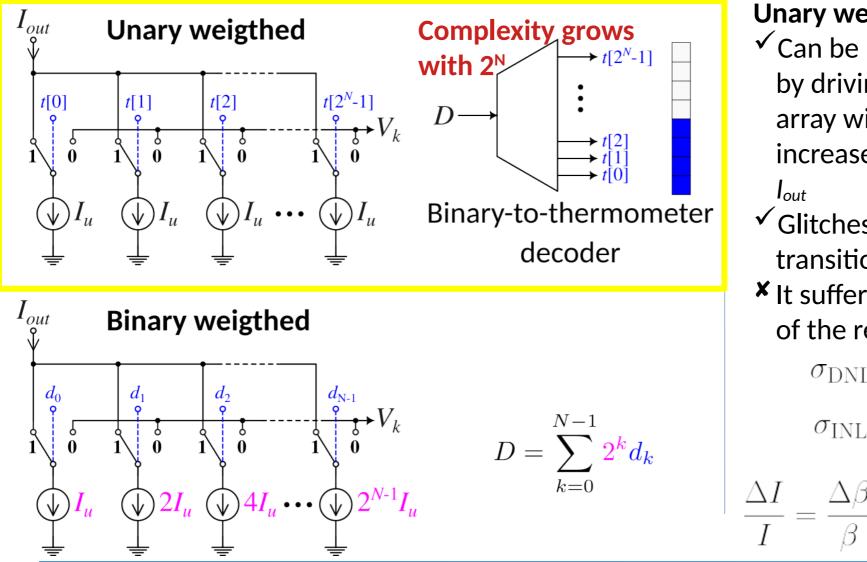

# CS DAC: Unary and Binary Weighted

**Unary weighted**

- ✓ Can be made monotonic-guaranteed by driving the  $2^{N}$  mosfets of the array with thermometric coding: D increase +1 : +1 more CS routed to

- $\checkmark$  Glitches proportional to code transition (small dynamic distortion)

- **X** It suffers from the same INL problem of the resistor string DAC:

$\sigma_{\rm DNL} = \sigma_{\Delta I/I}$

$\sigma_{\rm INL,max} = 2^{N/2-1} \cdot \sigma_{\Delta I/I}$

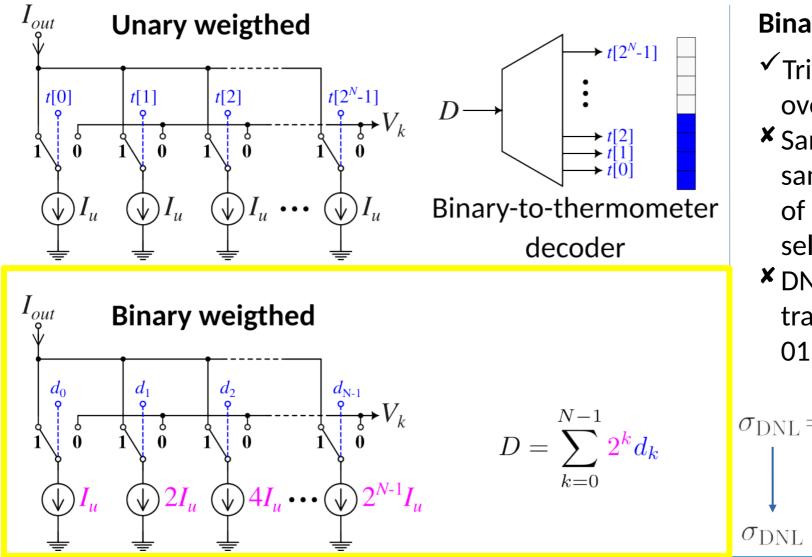

# CS DAC: Unary and Binary Weighted

### **Binary weighted**

- Trivial digital decoding (small overhead)

- ✗ Same INL as unary weighted (for the same output level, the same number of nominally identical I<sub>u</sub> sources are selected)

- ★ DNL: as in R-2R, the major code transition is the most critical:

011..→100..

$$\sigma_{\text{DNL}} = \underbrace{\left(2^{N-1} - 1\right)}_{011...} \sigma_{\Delta I/I} + \underbrace{\left(2^{N-1}\right)}_{100...} \sigma_{\Delta I/I}$$

$$\sigma_{\text{DNL}} \approx 2^{N} \sigma_{\Delta I/I} \quad \text{Critical!}$$

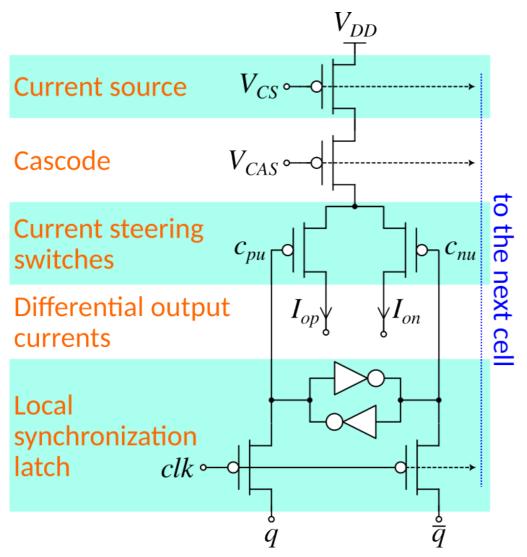

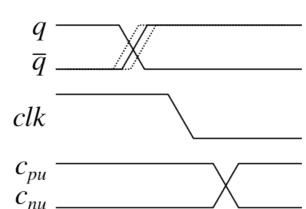

# **CS DAC: Cell Implementation**

Usually:

- Fully-differential implementation (avoids waste of current)

- **PMOS** CS for milder flicker (under area constraint)

- Local synchronization **latch** gated by global clock (very important for high-speed designs): avoids differential glitches at the output currents

Generated in a different part of the circuit, and routed eventually with different paths lengths and strays

### **CS DAC: Implementations** $R_G$ **I**outn ∎outn CS outp Array outp outp Array

If a voltage output is desired, the CS array output currents can be injected to the virtual ground of a TIA or terminated to a resistive load:

TIA solution: the virtual ground ensures , however distortion, noise of TIA is now of concern. High-power demanding choice, not compatible with high-speed requirements.

R-termination solution: output nodes undergo voltage swings, to avoid distortion, cascode (also double) are mandatory. Not compatible with low-voltage requirements.

# DAC Converters Design: Syllabus

### **General definitions**

- Applications

- Basic principles and operating electrical domains

- Performance parameters

### **Resistor-based DACs**

- R-string, R-string interpolated, and limits (DNL, INL analysis)

- R-2R ladder: binary weighting, DNL approximate analysis, configuration with a TIA.

### **Current-source (CS) based DACs**

- Unary and binary weighted CSs. DNL/INL analysis for binary scales CSs. Segmentation.

- Design for high precision: gradients due to physical processing and due to routing, solutions based on ordered element switching and calibration techniques based on current copier

Charge-scaling DACs

- Charge redistribution based on parallel capacitor banks

**INSIGH**

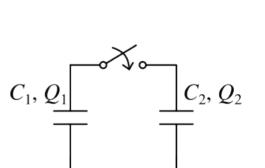

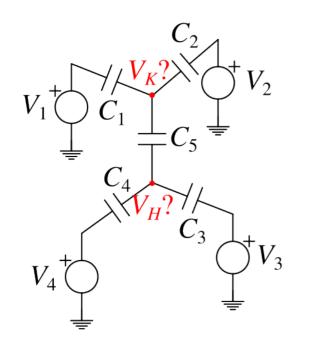

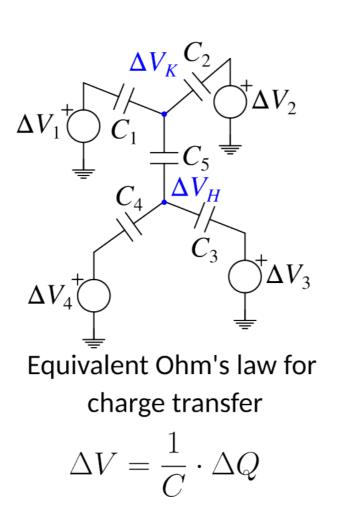

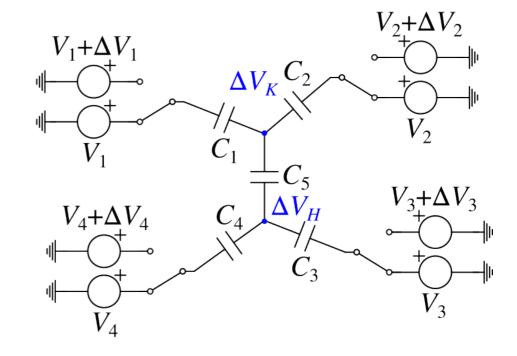

Charge redistribution: generic capacitors-only network

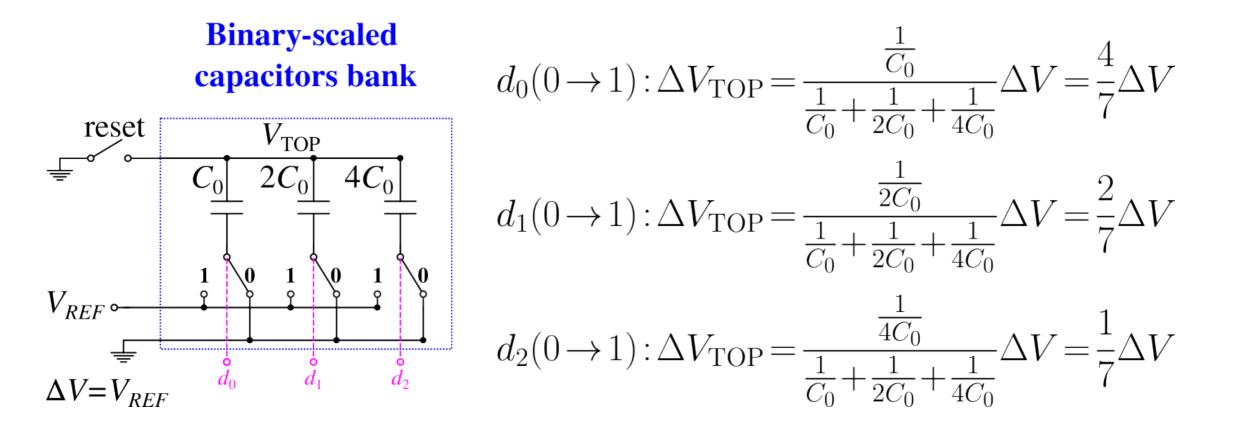

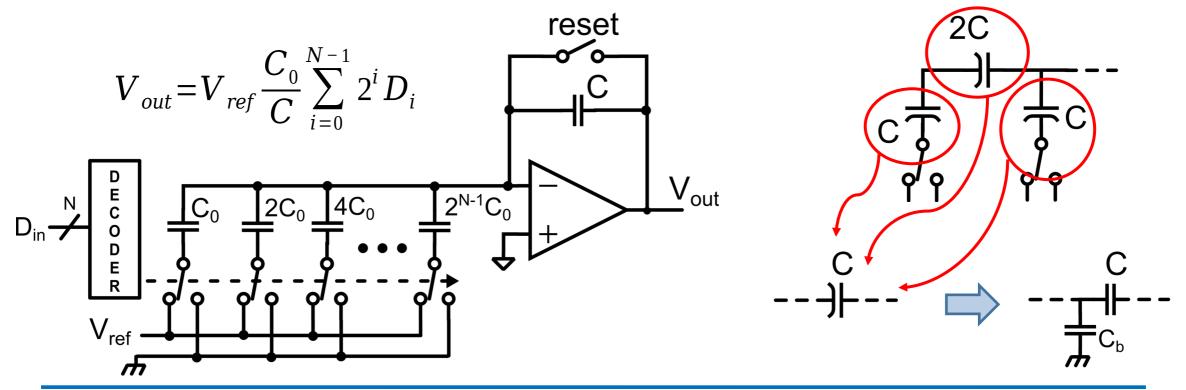

Charge redistribution: binary-scaled capacitor bank

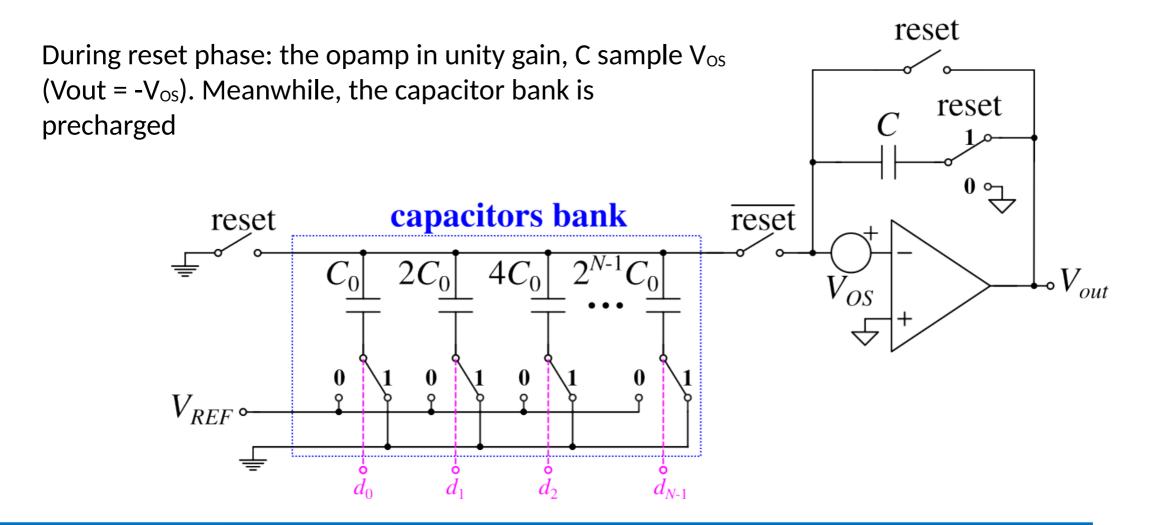

# Charge redistribution DAC

- ✓ Capacitor bank has better matching properties than resistor string

- Low-power solution (no static consumption in the capacitor bank)

- Output not always valid

- **×** Troubles with C-2C solutions due to parasitic capacitance of the bottom plate

### Charge redistribution DAC with CDS

# DAC architectures overview

|                         | Pros                                                                           | Cons                                                                                           |  |

|-------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| <b>Resistor String</b>  | Guaranteed monotonic.<br>Low power consumption                                 | Very large number of resistors                                                                 |  |

| R-2R ladder             | Reduced number of resistor of similar value                                    | Not inherently monotonic.<br>Suffers from the on-resistance of<br>the switches. Large glitches |  |

| <b>Current Steering</b> | Very fast. No need for<br>resistors. Can be designed<br>to be always monotonic | Current output.<br>Flicker Noise                                                               |  |

| Switched Capacitors     | Optimal power vs speed<br>trade-off                                            | The output may be not available<br>in the whole clock cycle.<br>Large glitches                 |  |

# DAC Converters Design: Insights

### **General definitions**

- Applications

- Basic principles and operating electrical domains

- Performance parameters

### **Resistor-based DACs**

- R-string, R-string interpolated, and limits (DNL, INL analysis)

- R-2R ladder: binary weighting, DNL approximate analysis, configuration with a TIA.

### **Current-source (CS) based DACs**

- Unary and binary weighted CSs. DNL/INL analysis for binary scales CSs. Segmentation.

- Design for high precision: gradients due to physical processing and due to routing, solutions based on ordered element switching and calibration techniques based on current copier

Charge-scaling DACs

- Charge redistribution based on parallel capacitor banks

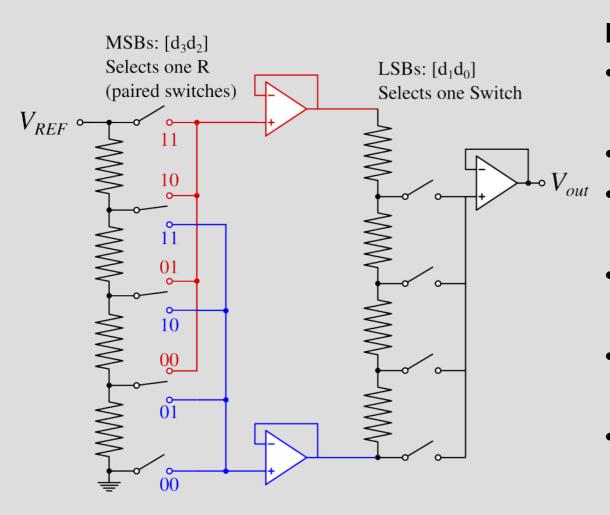

# R-String DAC (interpolated)

### **Interpolated R-string DAC: coarse + fine segments**

- The input D of N bit is divided in to an MSB segment of length M and an LSB segment of length L:

- N = M+L

- Each R in the MSB string is selected at time through the MSB segment of D

- The LSB segment is decoded to select one switch in the LSB segment string as before

- Now the number of levels are still 2<sup>N</sup>, but the number of Rs is now 2<sup>M</sup>+2<sup>L</sup>

- Monotonicity not guaranteed (due to opamp offsets). More advanced selection techniques are employed.

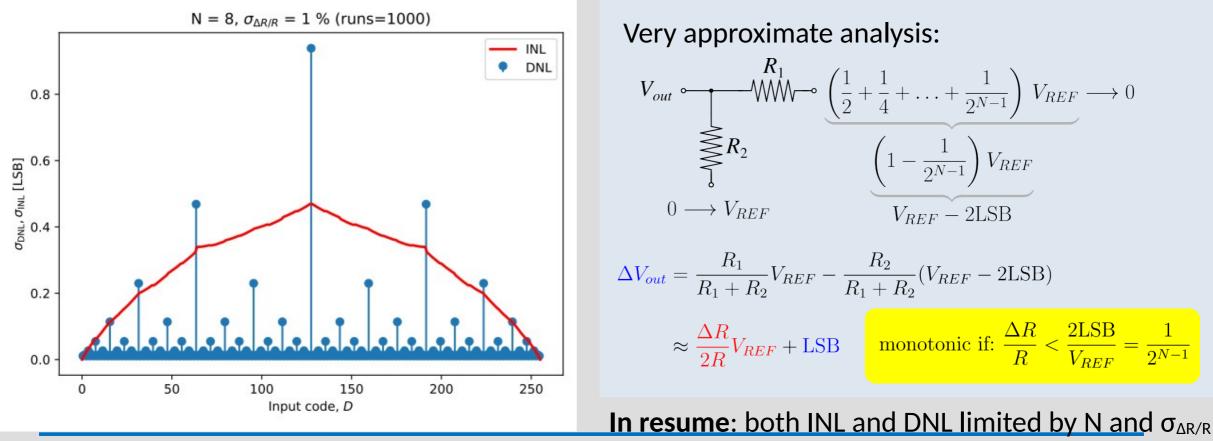

# The R-2R DAC: DNL and INL

- DNL and INL analysis is complex: usually the designer relies on Monte Carlo simulations

- The most relevant effect is on DNL, in correspondence with **major code transition**: 011...  $\rightarrow$  100...

- Empirically  $\sigma_{INL} \approx \sigma_{DNL}/2$ .

P. Bruschi – Design of Mixed Signal Circuits

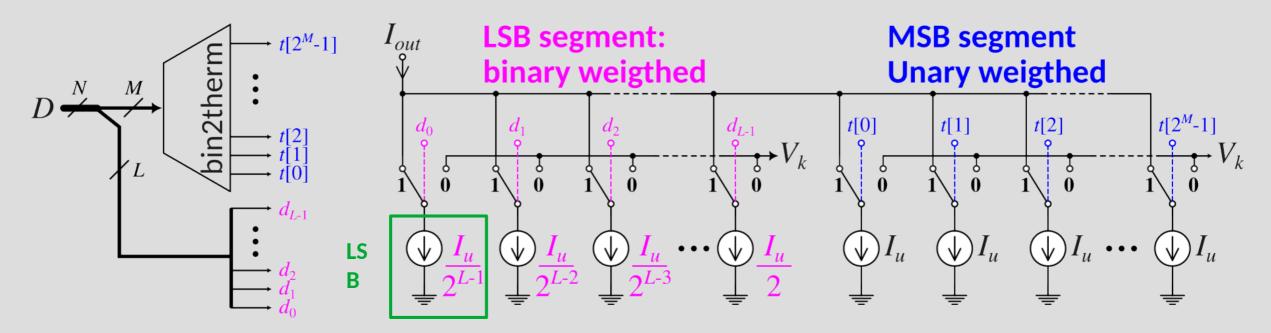

# CS DAC: Segmentation

**Objective:** strike a balance between complexity and accuracy

- N bits are segmented in M bits in the MSB segment and L bits in the LSB segment N = M + L

- INL is unaffected  $\sigma_{\text{INL,max}} = 2^{N/2-1} \cdot \sigma_{\Delta I/I}$

- DNL is dominated by the LSB segment  $\sigma_{\text{DNL}} = 2^L \sigma_{\Delta I/I}$

- The total number of switched elements depends on segmentation ratio  $2^M 1 + L$

# CS DAC: Segmentation

| $N = \underbrace{M}_{\text{MSB}} + \underbrace{L}_{\text{LSB}}$ | $\sigma_{\rm INL,max} = 2^{N/2-1} \cdot \sigma_{\Delta I/I}$ | $\sigma_{\rm DNL} = 2^L \sigma_{\Delta I/I}$ | $2^{M} - 1 + L$                   |

|-----------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------|-----------------------------------|

| Architecture                                                    | σ <sub>INL,max</sub> [σ <sub>ΔI/I</sub> ]                    | σ <sub>dnl</sub> [σ <sub>Δι/ι</sub> ]        | Number of<br>switched<br>elements |

| Unary, N = 10                                                   | 16                                                           | 1                                            | 1023                              |

| Segmented 6+4                                                   | 16                                                           | 16                                           | 67                                |

| Segmented 5+5                                                   | 16                                                           | 32                                           | 36                                |

| Segmented 4+6                                                   | 16                                                           | 64                                           | 21                                |

| Binary, N = 10                                                  | 16                                                           | 1024                                         | 10                                |

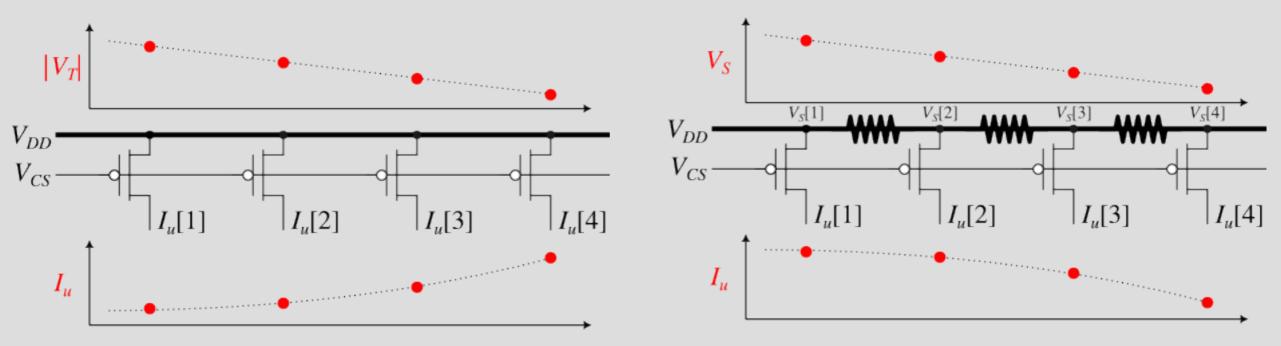

# CS DAC: typical floorplan

- Usually, linear floorplan: homologous devices (having the same functions) are put on the linear arrays for easier connection and compactness: as the number of elements grow, gradients are important

- The digital is in the lower part, separated from the quiet analog part

- Controlling signals cross the differential outputs (common-mode couplings)

- The clk line can be distributed in a treelike structure to compensate for delays

### CS DAC: gradients in large arrays

Nominally identical devices, under same bias conditions gives different currents due to: Manufacturing imperfections (e.g. threshold parameter spreading) Interconnection ohmic drops Both results in current gradients The switching order is decided by the digital logic Both results in current gradients The switching order is decided by the digital logic

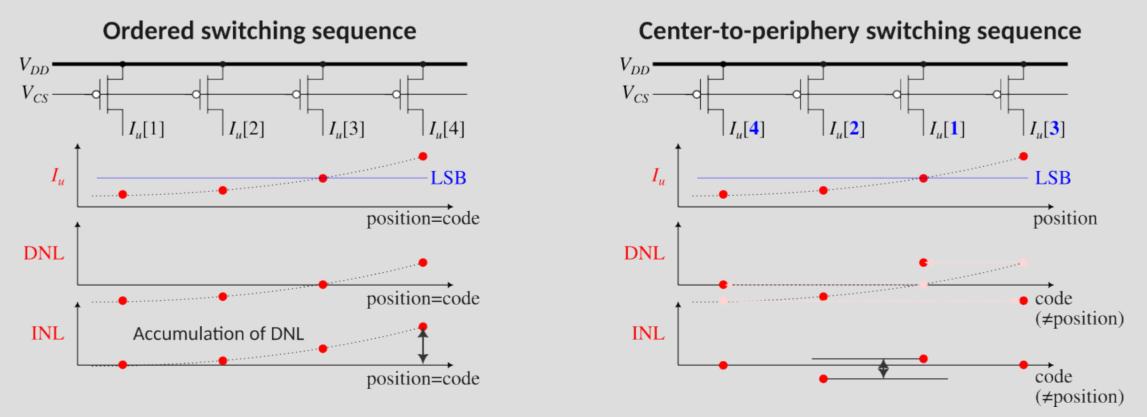

# CS DAC: switching sequence to brake the gradients

If we activate the CS in an orderly fashion: the gradient errors will accumulate  $\rightarrow$  large INL If the activation sequence starts from the center devices and hops to the outer ones, DNL is almost the same (statistically), but INL error gets tighter Resembles the **common centroid** layout technique

### CS DAC: current copier

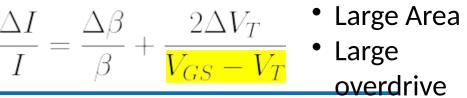

Static non linearity (INL/DNL) is main mechanism of distortion especially for medium-to-low bandwidth CS DACs. Intrinsic matching, implies (a) large cell area and (b) large V<sub>GS</sub> voltages. (a) In conflict with the need for small strays in high-speed applications;

(b) In conflict with low-voltage operation

<u>Alternatively</u>, mismatch is allowed to happen relaxing the other constraints, and it is corrected after fabrication with **dynamic calibration**

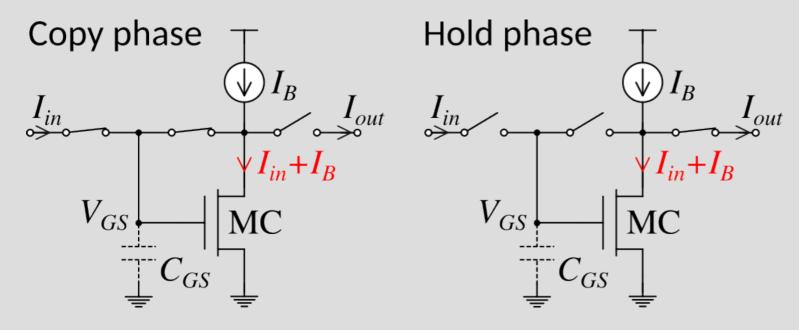

**Current copier operation:**

<u>Copy phase:</u> MC is diode connected,  $V_{GS}$ develops into the stray capacitance  $C_{GS}$ for a total current in MC of  $I_{in}+I_B$ <u>Hold phase:</u> the  $V_{GS}$  is hold by the stray CGS:  $I_{out} = I_{in}$

A current copier behaves like a virtually **mismatch-free current mirror**: same device for input and output current Beware charge injections and leakage

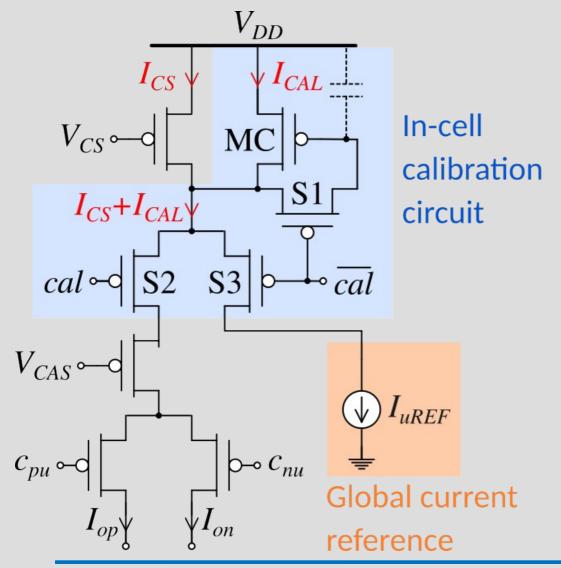

# CS DAC: calibration technique based on current copier

More switches (S1-S3) are added to the stack + a periodic calibration phase (*cal*) for each cell

MC adds a bit more current. The total cell current is  $I_{\text{CS}} + I_{\text{CAL}}$  , typically MC supplies 10-20% of the nominal current

During calibration:  $I_{CS}+I_{CAL} = I_{uREF}$

During normal operation: I<sub>CAL</sub> is kept thanks to the "analog" memory

All the unary CS are calibrated once at time in a cyclic fashion (refresh and track for changes due to temp)

The calibration runs in the **background** while the rest of the DAC operates as usual. While calibrating the element is not available for normal operation, hence we need at least one redundant element in the array