# Introducing myself

Michele Dei: michele.dei@unipi.it

Teaching during this year: ~20 hours

# Topics: Comparators, ADCs, DACs, Integrated Filters

## New here!

My hope is to maintain the high standards of this teaching

## Comparators

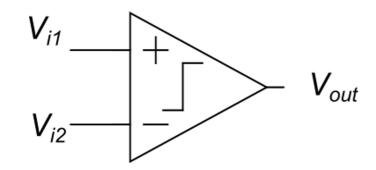

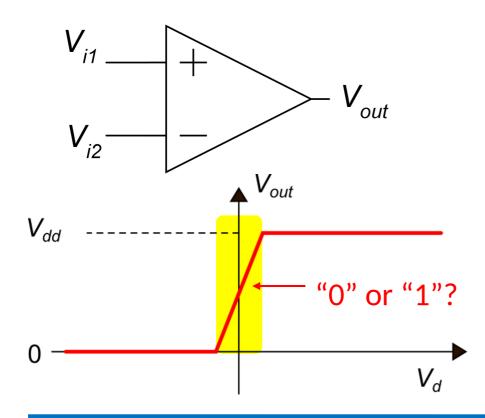

Symbol (differential input kind)

**Detect** the sign of a differential analog signal.

Sometimes S/E input case:

V<sub>i2</sub> is derived from an internal voltage reference

$$V_d = V_{i1} - V_{i2}$$

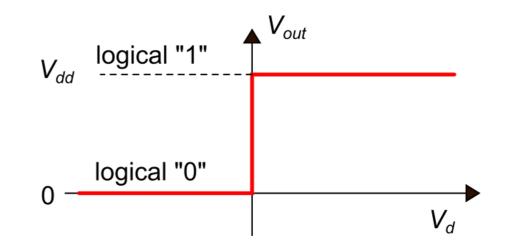

2) <u>Codify</u> the outcome in digital domain

$$V_{out} = \begin{cases} "0" \text{ if } V_d \leq 0 \\ "1" \text{ if } V_d > 0 \end{cases}$$

# Applications

## **Building block in:**

- Mixed-signal front-ends: sensors AFEs; signal-processing (ADCs, DACs)

- Signal-and-function generation

- Digital communication (symbol recognition in a noisy channel)

- Artificial neural networks (perceptron: linear binary classification)

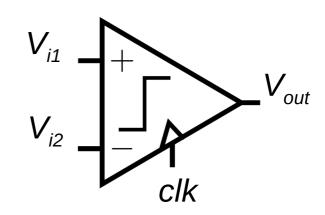

# Continuous-time vs dynamic comparator

#### Continuous-time (CT) comparator:

Used in level-crossing event-driven circuits

- **×** Static power consumption

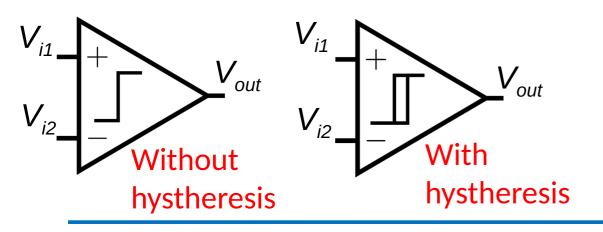

- Can be designed in order to embed hystheresis

- ✓ Output always valid

#### Dynamic comparator (or latched comparator):

Used in clock-synchronous circuits (as the comparator needs a driving clock signal)

- No static power consumption

(in basic single-stage configuration)

- No hysteresis

- ✗ Sometimes: output valid only during half clock period

# CT Comparators: amplifier-based implementations

A <u>high-gain</u> amplifier can be used as a comparator: Op-amp topologies can be used in <u>open loop</u> or even positive feedback: <u>Speed</u> is prime: no frequency compensation (no stability issues)

- \* Accuracy loss: a region exists where the logical level is undefined

- ★ In several applications this may lead to unwanted stable or metastable states (→)

# CT Comparators: amplifier-based implementations

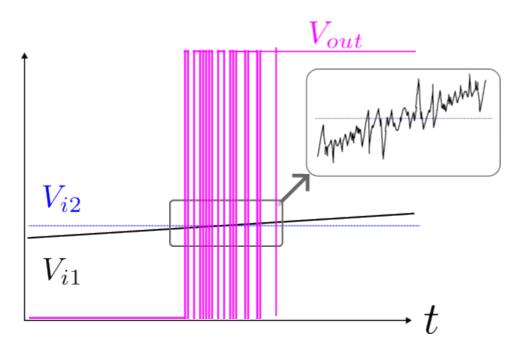

#### Transient behaviour: (RTI noise on Vi1 port)

#### **Glitches for slow varying input**

common issue to all CT comparators without hysteresis

If level crossing is used as trigger in a complex system with feed back: time uncertainty and/or stability issues

If the comparator is interfaced with a synchronous digital FSM:  $T_{hold}$ ,  $T_{setup}$  violation (need for synchronizer circuit otherwise data are loss)

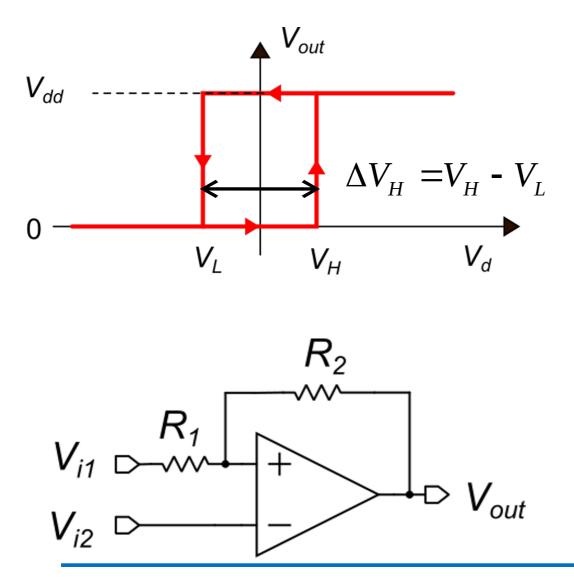

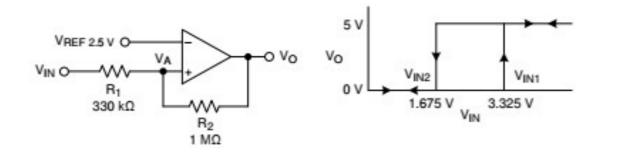

## Regenerative comparators: hysteresis

Thanks to the hysteresis, the comparator produces a **valid output** level across the whole input range. Use of positive feedback: **"vertical" edges**.

The hysteresis introduces an **uncertainty band** that reduces the accuracy but helps rejecting noise when the input differential voltage is close to zero.

Possible regenerative comparator: Op-amp-based Schmitt trigger.

#### Drawbacks

- Over-sized solution for integrated cells

- Low impedance on the non-inverting input

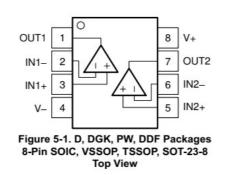

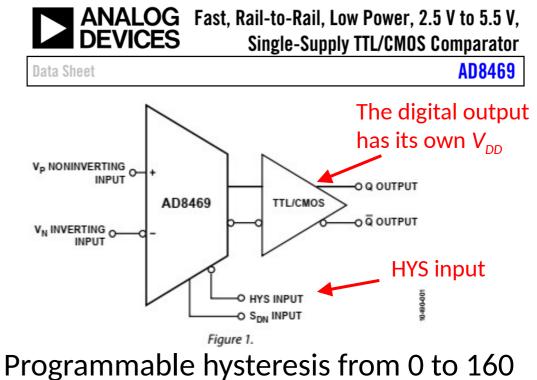

## Off-the-shelf devices

TLV9022, TLV9032, TLV9024, TLV9034 SNOSDA3B – JUNE 2020 – REVISED NOVEMBER 2020

TLV902x and TLV903x High-Precision Dual and Quad Comparators

- Rail-to-Rail input with fault-tolerance

- 100ns Typ propagation delay

#### No built-in hysteresis.

Datasheet suggests Schmitt trigger configuration

mV ( $\Delta V_H$ ) depending on current on pin

Input common-mode voltage: V<sub>EE</sub> – 0.2 V to V<sub>cc</sub> + 0.2 V Low glitch TTL-/CMOS-compatible output stage 40 ns propagation delay

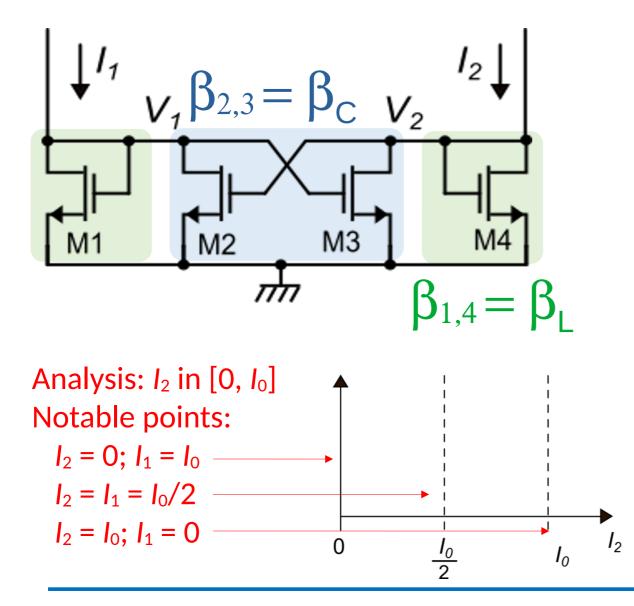

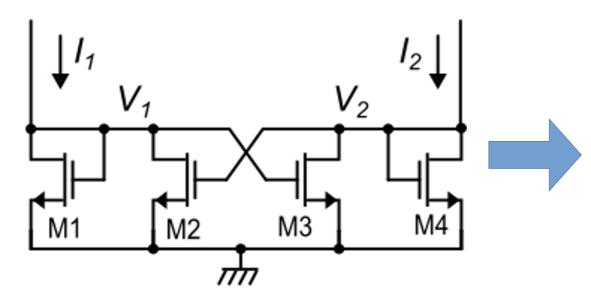

## Compact comparator cell for Systems on a Chip

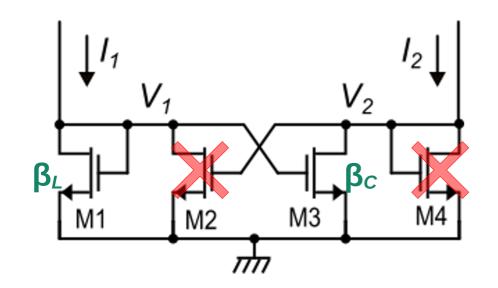

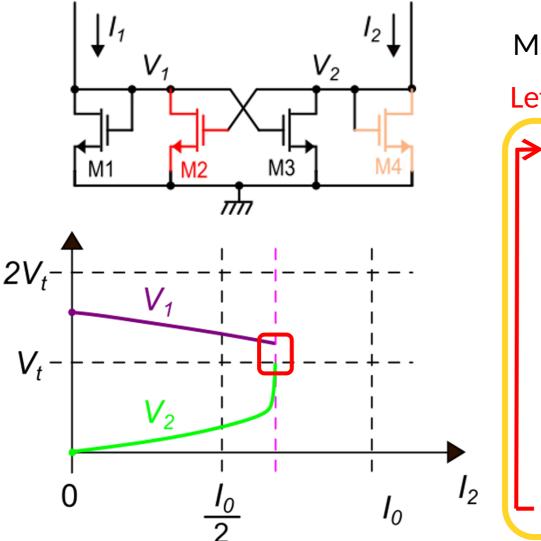

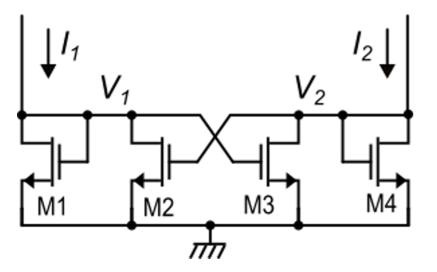

Four-transistor hysteresis cell Inputs: *I*<sub>1</sub>, *I*<sub>2</sub> Outputs: *V*<sub>1</sub>, *V*<sub>2</sub>

Formed by: Cross-coupled MOSFETs M2-M3 Load MOSFETS M1, M4

Constraint:  $I_1 + I_2 = I_0 = \text{constant}$

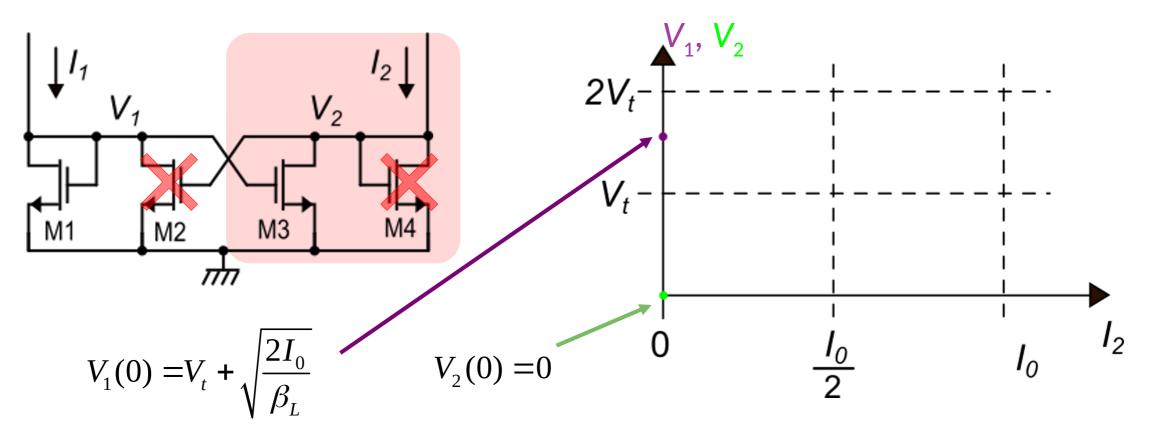

## Analysis of the four-transistor cell: starting point

Let us start from:  $I_2=0$  ( $I_1=I_0$ )  $I_2 = I_{D3} + I_{D4} = 0$ since:  $I_{D3}, I_{D4} \ge 0$   $I_{D3} = I_{D4} = 0$ Considering M4 and M2:  $V_{GS4} \leq V_t = V_{GS4} = I_{D2} = 0$  $V_1 = V_{GS1} = V_t + \sqrt{\frac{2I_1}{\beta_L}} = V_t + \sqrt{\frac{2I_0}{\beta_L}}$ Then it is M1 that carries all current  $I_1$ :  $V_{GS3} = V_{GS1} \ge V_t \quad (M3 \text{ is on})$  $V_{DS3} = V_2 = 0$  $I_{D3} = 0$

## Analysis of the four-transistor cell: starting point

**Design condition:** we size  $\beta_{L}$  in such a way that:

$V_1(0) = V_{GS1}(0) < 2V_t \implies V_{GS1}(0) - V_t < V_t$  The reason will be clear later

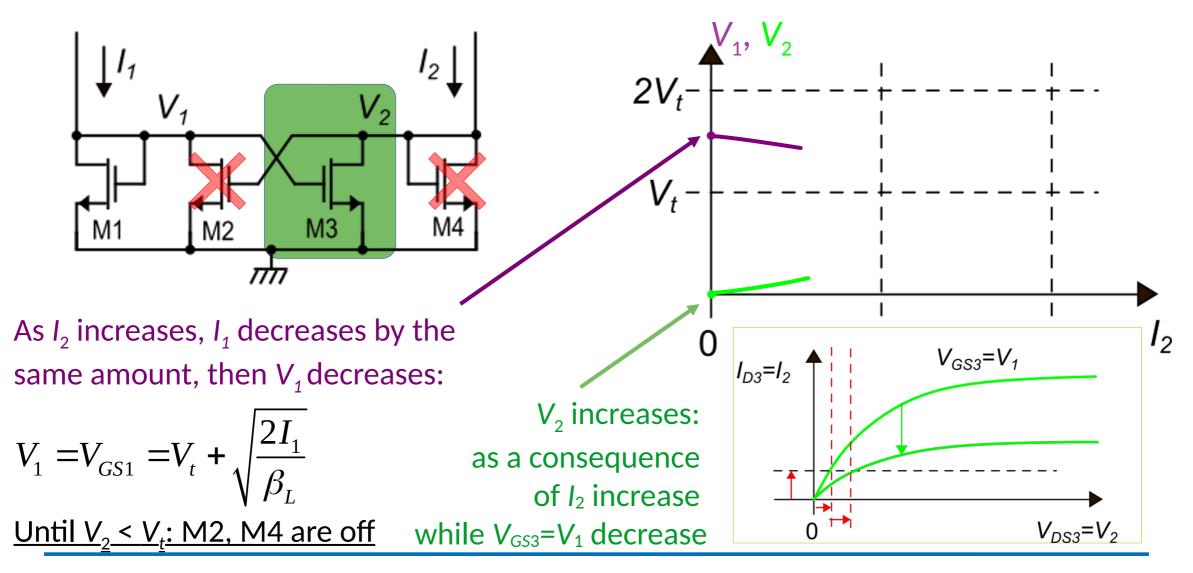

## Analysis of the four-transistor cell: increasing I<sub>2</sub>

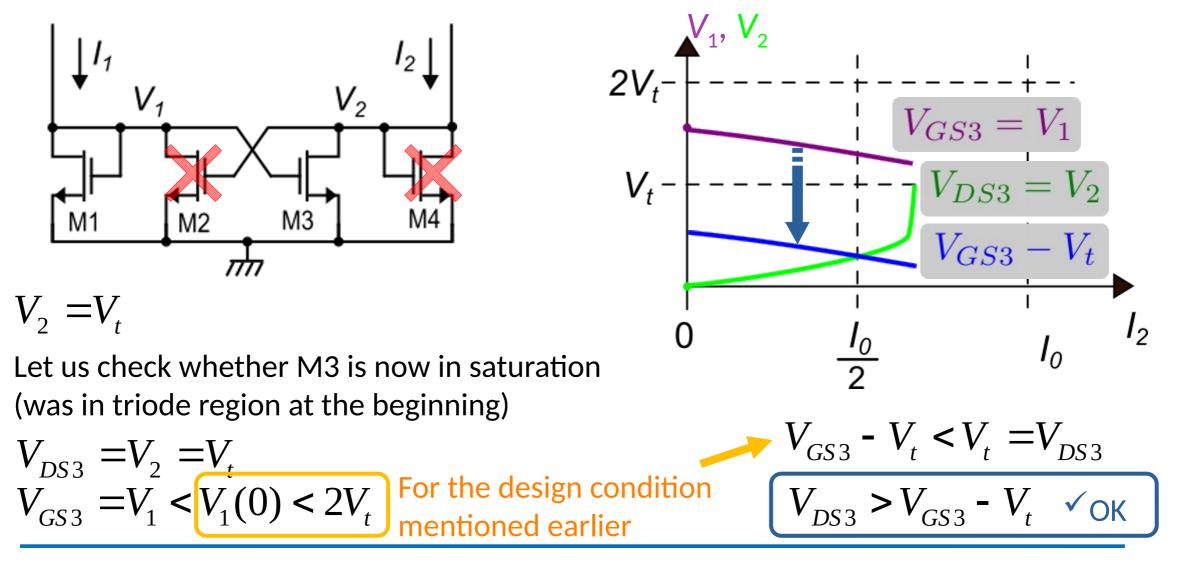

Analysis of the four-transistor cell: V<sub>2</sub> reaches V<sub>t</sub>

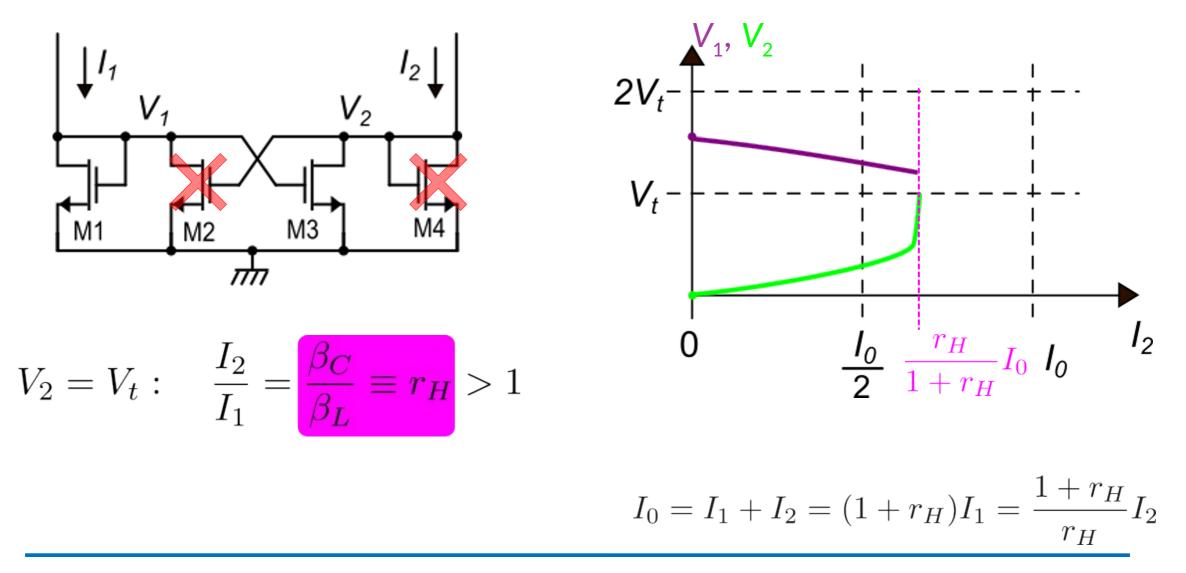

For  $V_2 = V_t$ , M2 and M4 are still off. Then (M1 and M3 have the same VGS):

$$I_1 = I_{D1} \qquad I_2 = I_{D3}$$

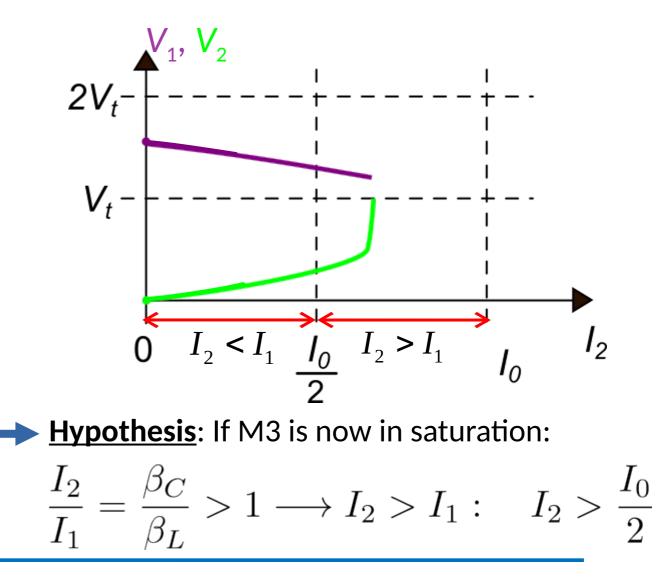

Analysis of the four-transistor cell: M3 saturation hypothesis

Analysis of the four-transistor cell: V<sub>2</sub> reaches V<sub>t</sub>

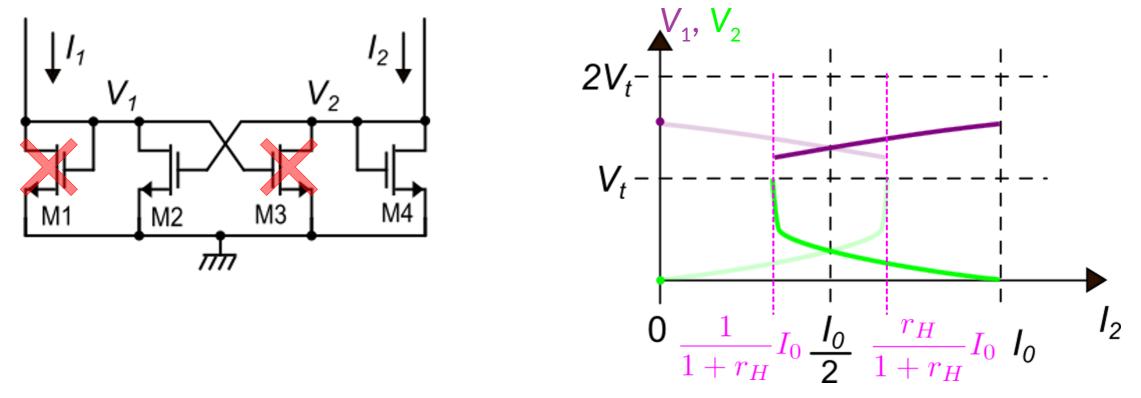

Analysis of the four-transistor cell: starting from the opposite end point

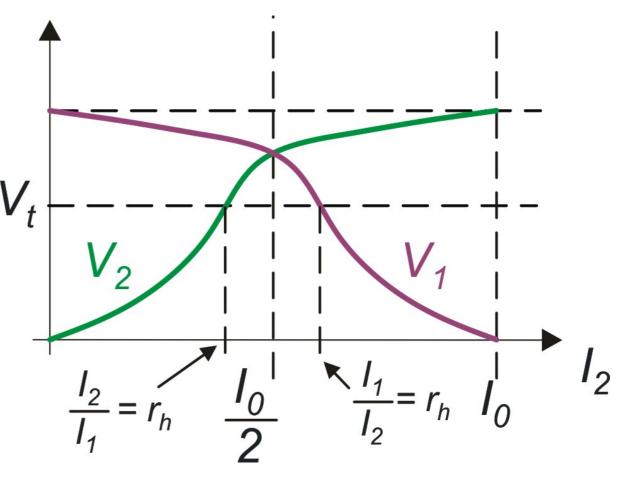

Repeating the same procedure but starting from the rightmost point ( $I_1 = 0, I_2 = I_0$ ), we obtain a <u>symmetrical behavior</u> (around  $I_0/2$ ) with  $V_1$  and  $V_2$  interchanged. Now  $V_1$  reaches  $V_t$  for  $I_1/I_2 = r_H$ .

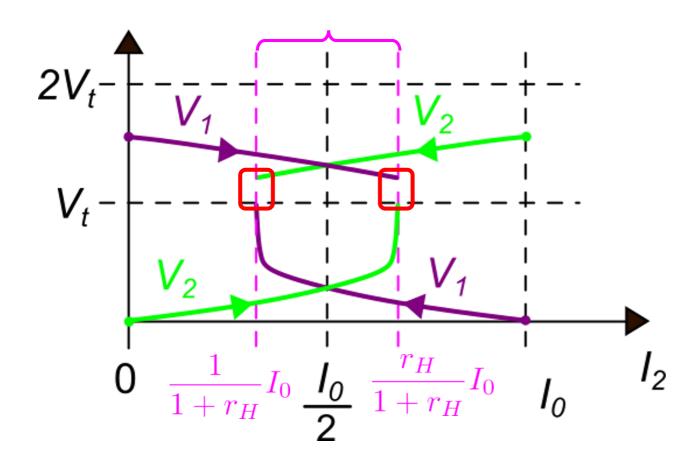

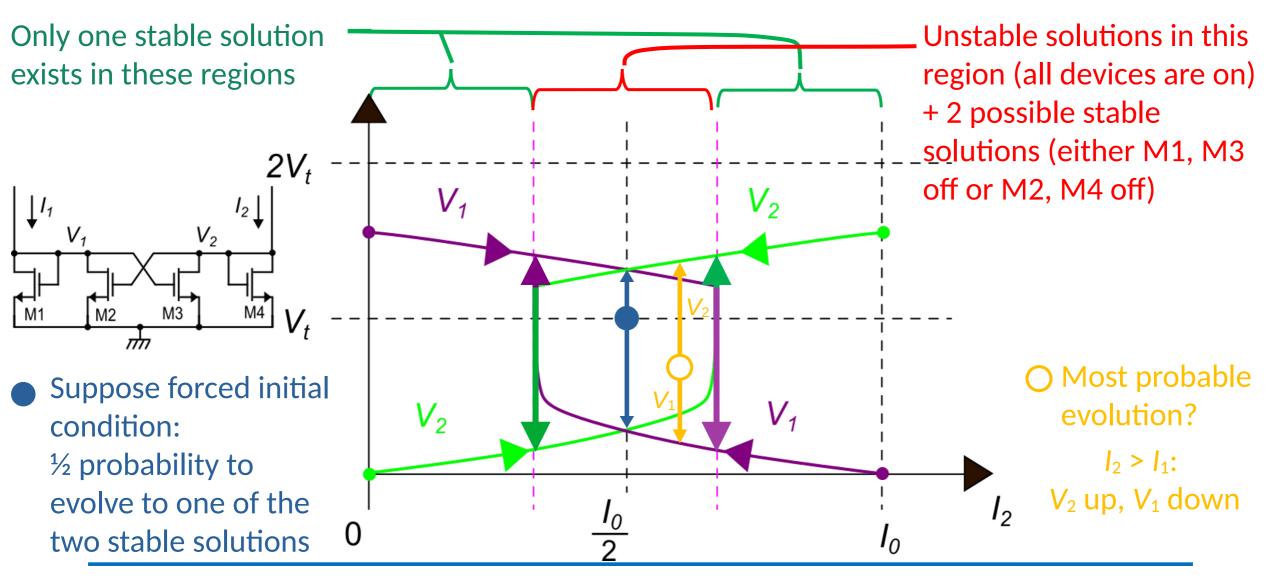

## Analysis of the four-transistor cell: combining the two behaviours

In this **region**, there are <u>two possible</u> <u>stable states</u>, depending on which extreme we started from:

This means that there is **hysteresis**

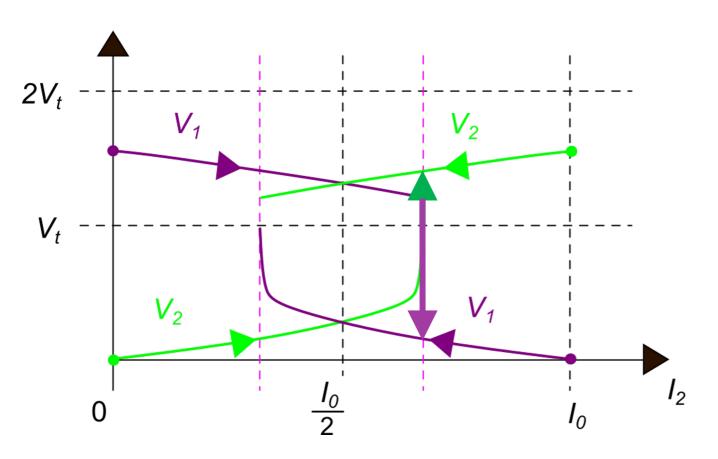

Now, we investigate what happens when the lower voltage hits the  $V_t$  line

# Analysis of the four-transistor cell: phenomena that happen when $V_2$ overcome $V_t$

M2 and M4 turn on (while M1 and M3 are still on) Let us focus on M2 **Positive feedback loop 1.** As M2 turns on, it start stealing current from M1 **2.**  $V_1$  decreases:  $V_1 = V_{GS1} = V_t + \sqrt{\frac{2I_{D1}}{\beta_1}}$ **3.**  $V_{GS3} = V_1$ , then  $I_{D3}$  reduces, increasing the current that flows into M4 **4.**  $V_2$  increases:  $V_2 = V_{GS4} = V_t + \sqrt{\frac{2I_{D4}}{\beta_r}}$

**5.**  $V_{GS2} = V_2$ , then  $I_{D2}$  increases further

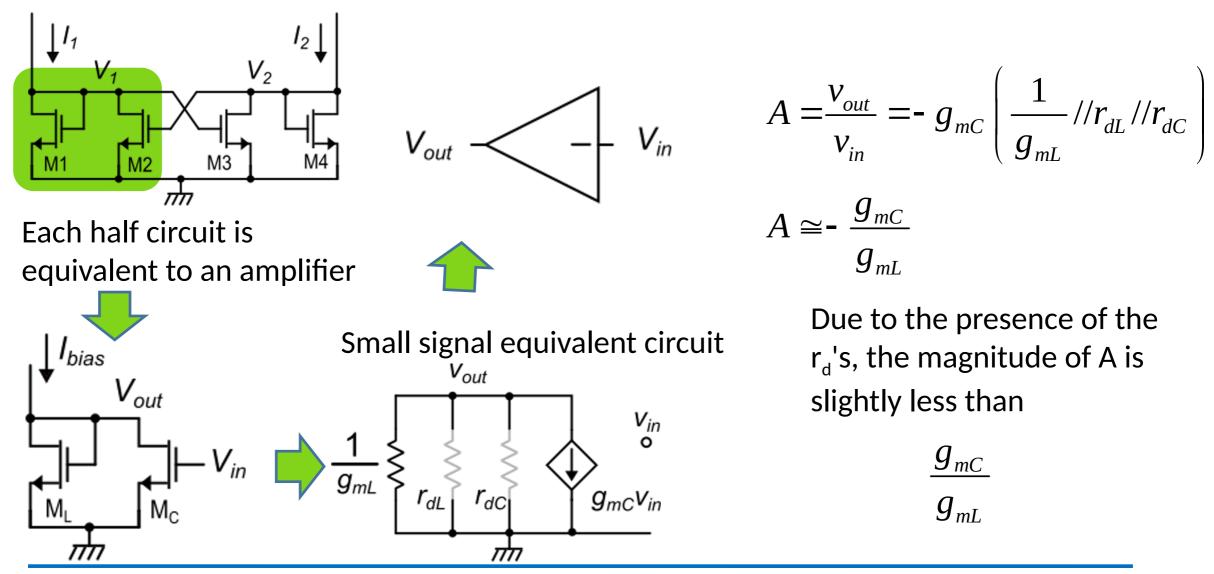

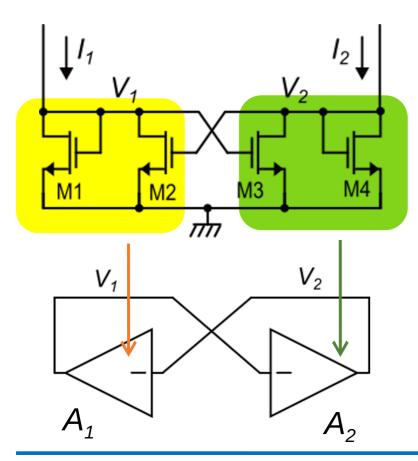

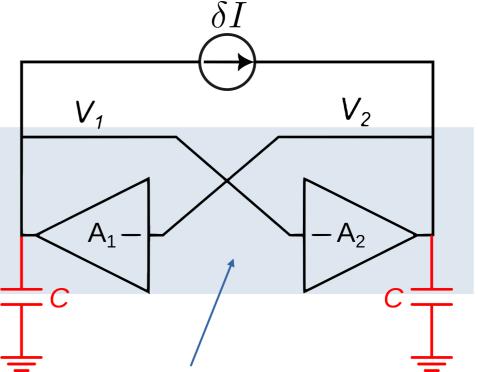

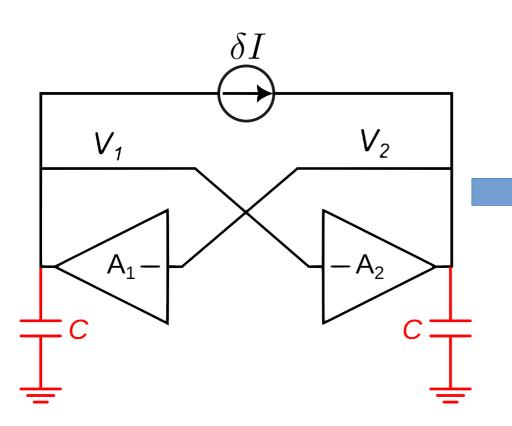

## Positive feedback loop: small-signal analysis

## Positive feedback loop: small-signal analysis

When  $V_2$  overcomes  $V_{t,}$  all MOSFETs are on:

$$A_{1} = -\frac{g_{m2}}{g_{m1}}; A_{2} = -\frac{g_{m3}}{g_{m4}}$$

$$\beta A = A_{1}A_{2} > 0 \quad \text{Positive feedback}$$

$$g_{m1} = \beta_{L} (V_{GS1} - V_{t}), g_{m2} = \beta_{C} (V_{GS2} - V_{t})$$

$$g_{m3} = \beta_{C} (V_{GS3} - V_{t}), g_{m4} = \beta_{L} (V_{GS4} - V_{t})$$

$$V_{GS1} = V_{GS3} = V_{1}, V_{GS2} = V_{GS4} = V_{2}$$

$$\beta A = \frac{\beta_{C} (V_{2} - V_{t})}{\beta_{L} (V_{1} - V_{t})} \cdot \frac{\beta_{C} (V_{1} - V_{t})}{\beta_{L} (V_{2} - V_{t})} = \left(\frac{\beta_{C}}{\beta_{L}}\right)^{2}$$

Positive feedback loop: regeneration

$$\frac{\beta_C}{\beta_L} = r_H > 1 \implies |\beta A| > 1 \text{ (DC instability)}$$

Therefore, a stable condition cannot exist if all MOSFETs are on.

#### **Important condition**

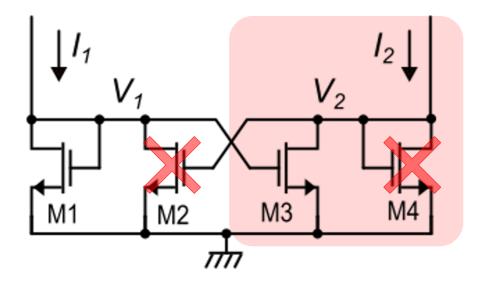

$V_1$  and  $V_2$  cannot be greater than  $V_t$  <u>at same time</u> in a stable condition Then, when M1 is on, M4 is off and *vice versa*  Positive feedback loop: non-regenerative case (no hysteresis)

$$\frac{\beta_{C}}{\beta_{L}} = r_{H} < 1$$

$$|\beta A| = \left(\frac{\beta_{C}}{\beta_{L}}\right)^{2} < 1$$

In this case, the positive feedback is unable to cause an abrupt transition:

Hysteresis is not present

This configuration is never used (should be regarded as a design error)

## Positive feedback loop: the "click"

Proceeding from the left, when  $V_2$ overcomes the  $V_t$  line, the positive feedback makes the voltage evolve autonomously

The new stable solution is the one we already found proceeding back from the right: the regeneration stops when loop gain is no longer > 1

# Positive feedback loop: stable characteristics and unstable solution

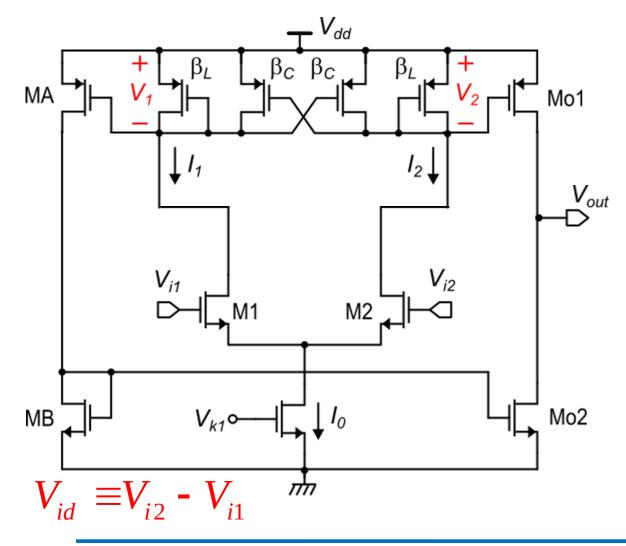

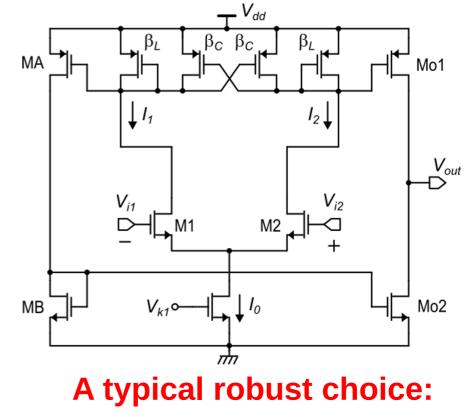

## A simple comparator based on the 4-transistor hysteresis cell

We start with a p-version of the hysteresis cell

Currents  $I_1$  and  $I_2$  are derived from the input voltage  $V_{id} = V_{i2} - V_{i1}$  by means of a differential pair

Only one at a time between  $V_1$  and  $V_2$  is greater than the p-mos threshold voltage.

If  $V_1 > |V_{tp}|$ ,  $V_2 < |V_{tp}|$  MA, MB and Mo2 are on, while Mo1 is off:  $V_{out} = 0$

If  $V_2 > |V_{tp}|$ ,  $V_1 < |V_{tp}|$ , only Mo1 is on:  $V_{out} = V_d$

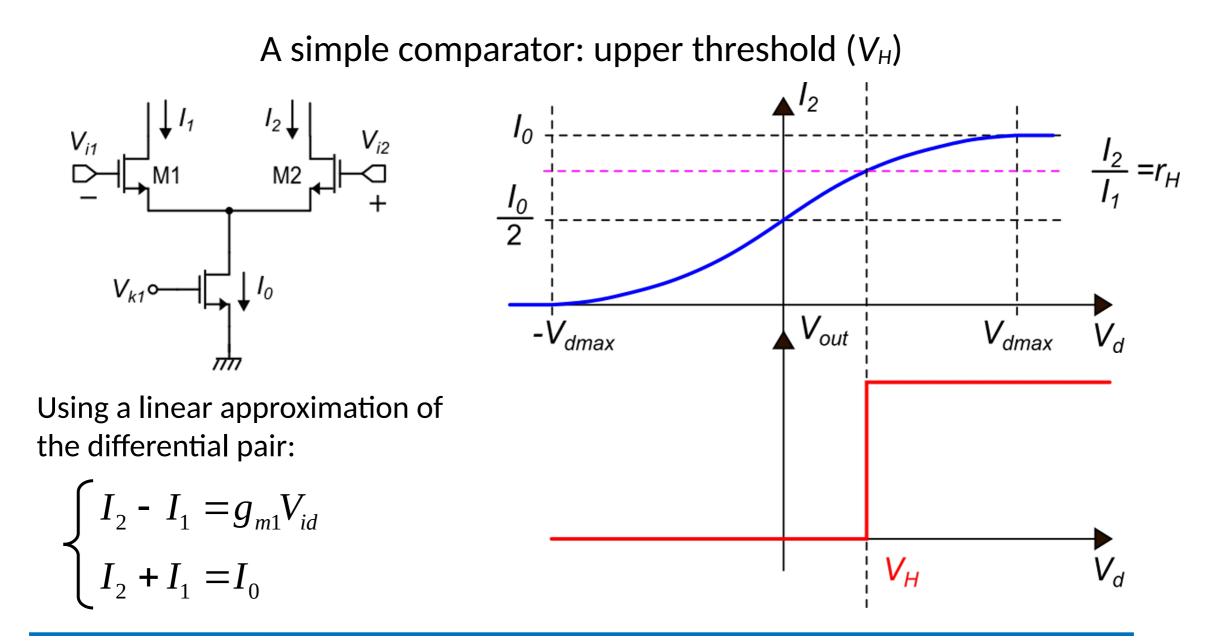

## A simple comparator: upper threshold (V<sub>H</sub>)

$$\begin{cases} I_{2} - I_{1} = g_{m1}V_{H} \\ I_{2} + I_{1} = I_{0} \\ \frac{I_{2}}{I_{1}} = r_{H} \end{cases} \quad I_{2} - I_{1} = I_{1}(r_{H} - 1) = g_{m1}V_{H} \\ I_{2} + I_{1} = I_{1}(r_{H} + 1) = I_{0} \end{cases}$$

Dividing the upper equation by the lower one:

$$\frac{r_{H} - 1}{r_{H} + 1} = \frac{g_{m1}}{I_{0}} V_{H}$$

In quiescent conditions:  $I_0 = 2I_{D1-Q} = 2V_{TE1}g_{m1}$

$$\frac{r_{H} - 1}{r_{H} + 1} = \frac{1}{2V_{TE1}} V_{H} \qquad V_{H} = 2V_{TE1} \frac{r_{H} - 1}{r_{H} + 1}$$

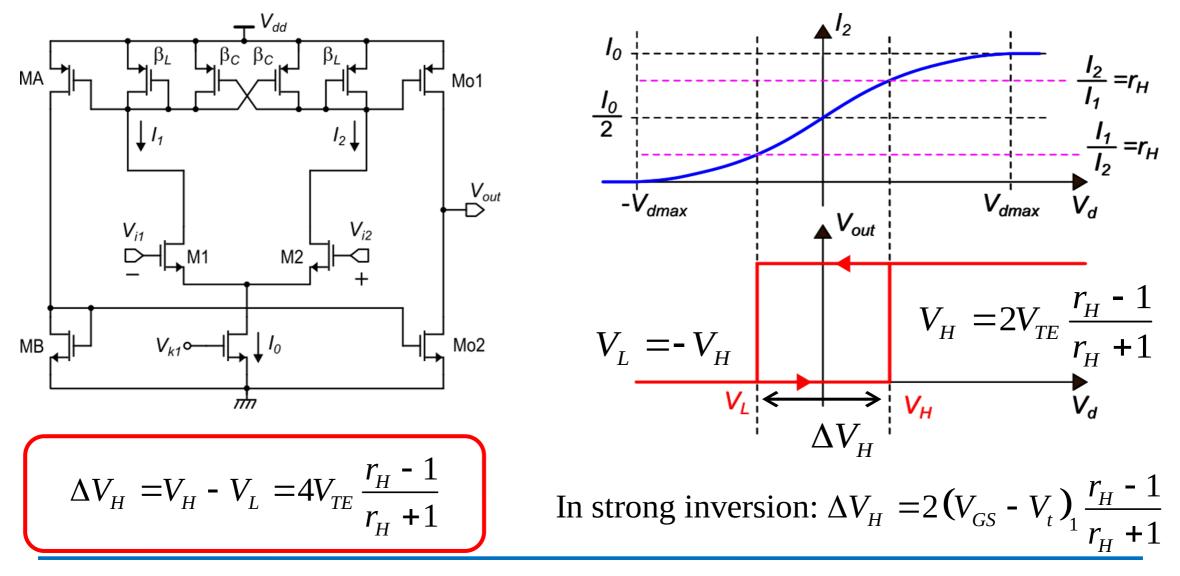

#### A simple comparator: complete characteristics

## A simple comparator: minimum achievable hysteresis

$$\Delta V_{H} = V_{H} - V_{L} = 4V_{TE} \frac{r_{H} - 1}{r_{H} + 1}$$

## To obtain a small hysteresis

- Make  $V_{TE1}$  as small as possible

- Make  $r_{H}$  just slightly larger than 1

<u>However</u>, other requirements impose to make  $r_{\rm H}$  significantly larger than 1, because:

- 1) The calculated  $|\beta A| = (r_{\mu})^2$  is overestimated, since we have neglected the  $r_d$ 's

- 2) Process error can make  $r_{H} < 1$  if the margin to 1 is too small

- 3) The transition is faster with larger  $|\beta A|$

$$r_{H} = 2 \Rightarrow \Delta V_{H} = \frac{4}{3} V_{TE}$$

$\Delta V_{H}$  as small as **50 mV**

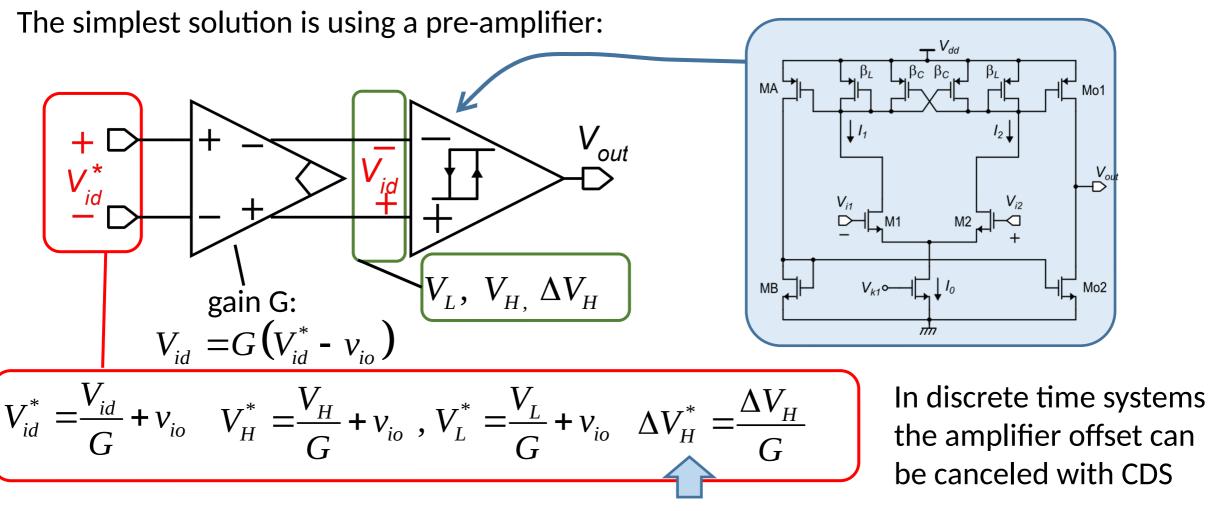

# A simple comparator: low hysteresis using a preamplifier

The hysteresis is divided by the preamplifier gain (G)

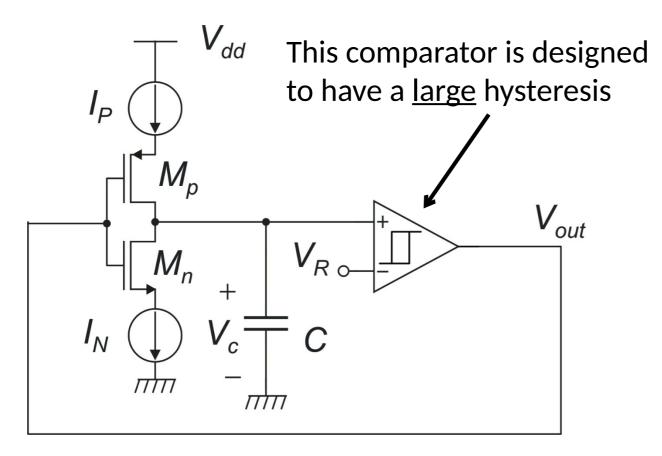

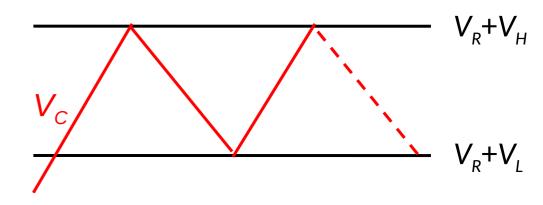

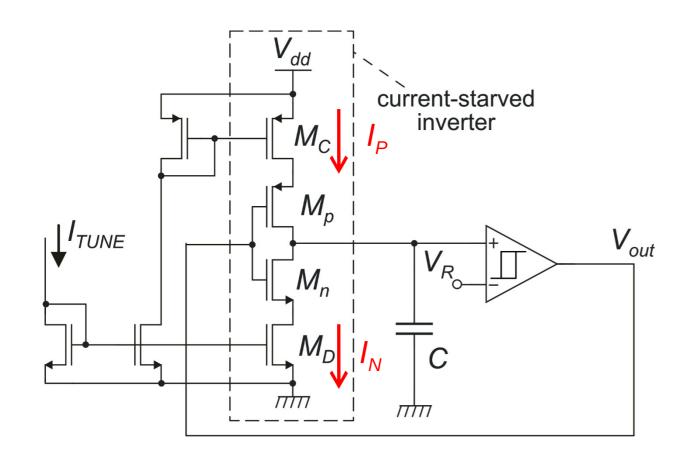

# A simple VCO for low-frequency applications

First step: place the comparator in a feedback loop with a currentcontrolled charging-discharging mechanism

- When  $V_{out}$ =0, the capacitor is charged by  $I_P$

- When  $V_{out}$ =1, the capacitor is discharged by  $I_N$

#### A simple low-frequency VCO: oscillator frequency

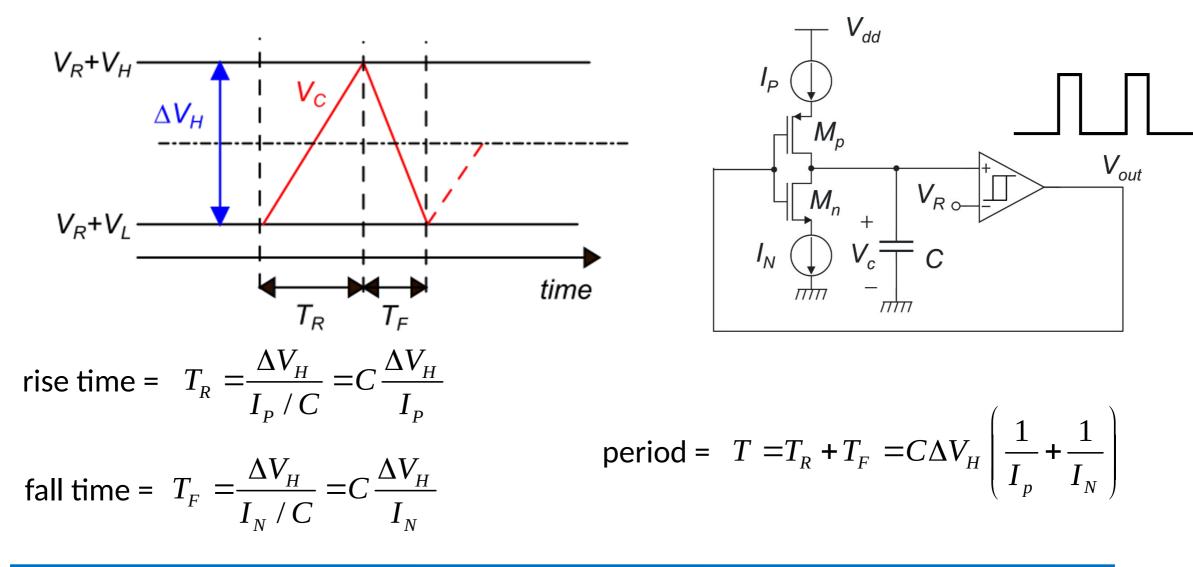

## A simple low-frequency VCO: Implementation with "current starved" inverter

If  $I_P = I_N = I_{tune}$ :

$$T = 2\frac{C\Delta V_{H}}{I_{tune}} \quad f = \frac{I_{tune}}{2C\Delta V_{H}}$$

The frequency is proportional to the tuning current (**CCO**)

Using a linear voltage to current converter it is possible to make  $I_{tune}$ to be proportional to a voltage, transforming the CCO into a VCO

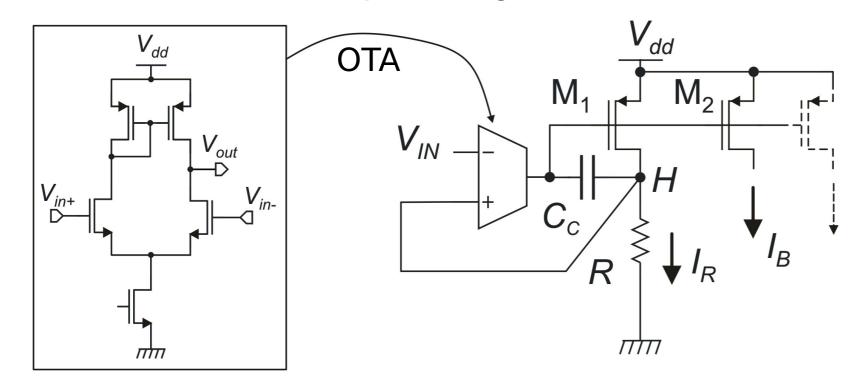

#### A simple voltage-to-current converter

This circuit can be used also to produce constant currents from a single reference voltage

The OTA, and M1 form a two-stage op-amp with output on node H, stabilized by  $C_c$  (Miller compensation). The op-amp is closed as a buffer:  $V_H = V_{IN} \implies I_R = I_{D1} = \frac{V_{in}}{R} \implies I_B = \frac{\beta_2}{\beta_1} I_{D1} = \frac{\beta_2}{\beta_1} \frac{V_{IN}}{R}$

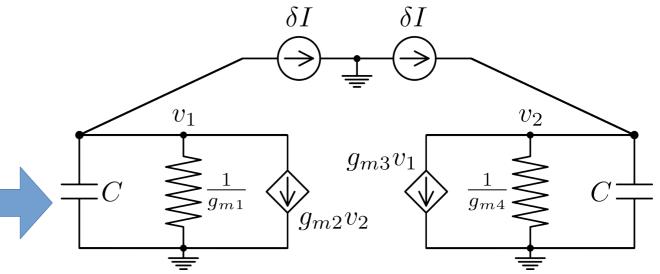

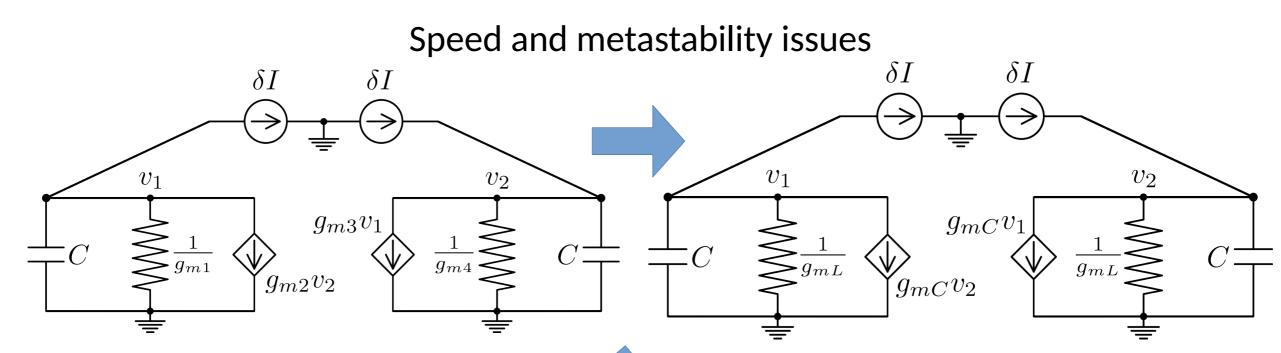

Speed and metastability issues

**Metastability**: the comparator does not provide a clear logical output level in a given amount of time  $\delta T$

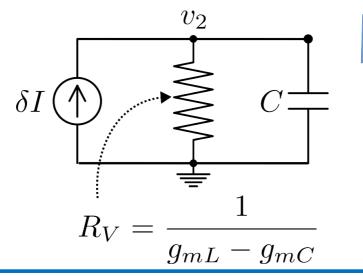

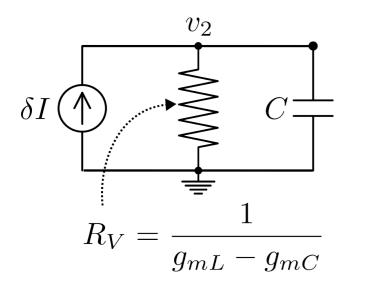

Small signal equivalent circuit of half cell: + inertial component (C)

$R_V$ : negative signed for regenerative positive feedback

## Speed and metastability issues

Approximations around the "click" points:  $g_{m1} \approx g_{m4} \approx g_{mL}$

$g_{m2} \approx g_{m3} \approx g_{mC}$

Not rigorous but useful for understanding purposes: the circuit is non-linear anyway.

Accurate results only through electrical simulations P. Bruschi – Design of Mixed Signal Circuits <sup>36</sup>

Under this approximation, the circuit is completely symmetric:  $v_1 \approx -v_2$

We can study only half circuit, for simplicity

# Speed and metastability issues

Transient response characterized by growing exponential response: e<sup>at</sup>

$$a = \frac{1}{|R_V|C} = \frac{g_{mL}}{C} \left| 1 - \frac{g_{mC}}{g_{mL}} \right| \approx \frac{g_{mL}}{C} \left| 1 - \sqrt{\beta A} \right|$$

Hence, the higher  $\beta A$ , the faster is the response (as mentioned previously).

Designing low-hysteresis comparator by pushing βA close to 1 is a **BAD IDEA**: <u>not only</u> process sensitivity may lead to lack of hysteresis, <u>but also</u> the comparator would result very slow:

The pre-amp solution with is always used in such cases

# Syllabus

**Design of integrated comparators**

# Done (today's class):

- 1) Ideal behaviour

- 2) Applications

- 3) Taxonomy

- 4) The 4T-hysteretic cell for SoC

- 5) Simple comparator based on the 4T-hysteretic cell

- 6) Low-frequency relaxation oscillator based on simple VCO

- 7) Notes on speed and metastability (optional material)

# To do (next class):

- 8) Dynamic comparator example: the StrongARM case

- 9) Other comparator structures from literature (optional material)