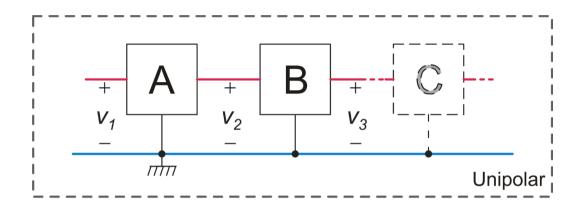

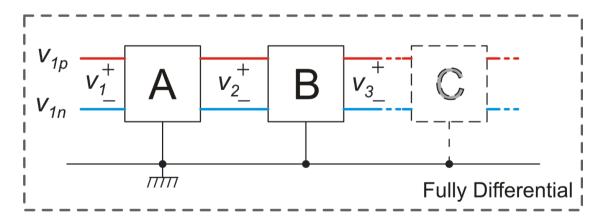

## Fully differential and unipolar (single-ended) circuits

Each signal is carried by a **single wire**. Signals (v1, v2, ...) are voltages differences between the wires and a common node (usually gnd).

Each signal is carried by <u>a wire</u> <u>pair.</u> Signals (v1, v2 ...) are the voltage difference between the wires that form the pairs.

#### Fully differential systems: motivations

Advantages of fully differential circuit with respect to unipolar circuits

- Lower sensitivity to interference

- Wider output range

- Better linearity

#### **Drawbacks**

- Greater complexity (e.g. the feedback networks are formed by twice the components as in the unipolar case).

- Require stabilization of common mode voltages.

#### Interference coupling mechanisms

- Ground currents (non-uniform gnd)

- Vdd variations

- Capacitive coupling

- Substrate noise

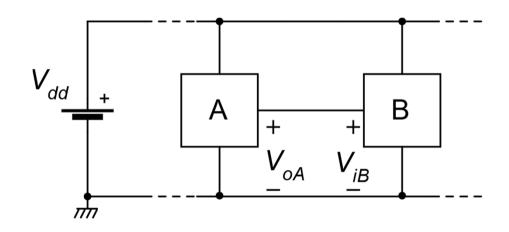

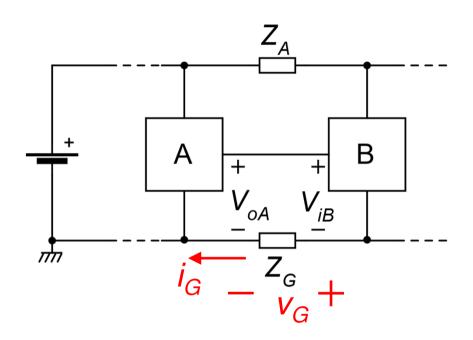

#### Ground currents: ideal case

All interconnections have null series impedance. Gnd and Vdd can be considered as single nodes.

$$V_{iB} = V_{oA}$$

#### Ground currents: real case

Physical interconnections have non-zero resistance and non-zero inductance

Gnd and Vdd conductors carry considerable currents since they distribute power to all blocks.

Current  $i_G$  flowing in the ground conductor creates a difference  $v_G$  between the two local grounds in the vicinity of blocks A and B.

$$v_G = Z_G i_G \qquad v_{iB} = v_{oA} - v_G$$

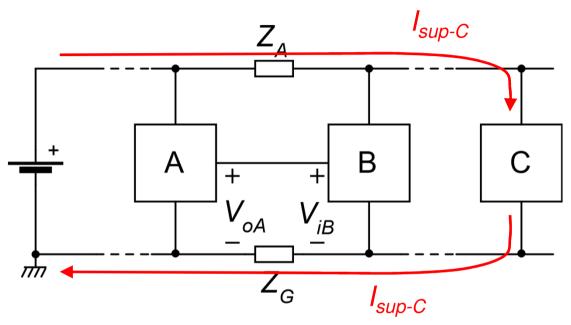

#### Critical cases

If block C is a digital circuit synchronized by a fast clock, its supply current  $I_{sup-C}$ , contains spectral components up to very high frequencies.

The resulting interference on the analog circuits can be difficult to reject since high frequency components can fold-back to low frequencies through sampling (ADCs, SC circuits) or non-linearities.

#### Origin of the $Z_G$ impedance.

#### Integrated circuits

- Interconnect lines (tens of Ohm if gnd routing is not performed properly)

- Vias (typically 0.1 Ohm / via)

- Inductance is generally negligible up to several GHz

#### Printed Circuit Boards (PCBs)

- Interconnect resistances are generally the tens of  $m\Omega$  range

- Inductances can be significant

#### Board-to-Board interconnections (connecting wires)

- Inductance is generally dominant

- Contact resistance in connectors can be important

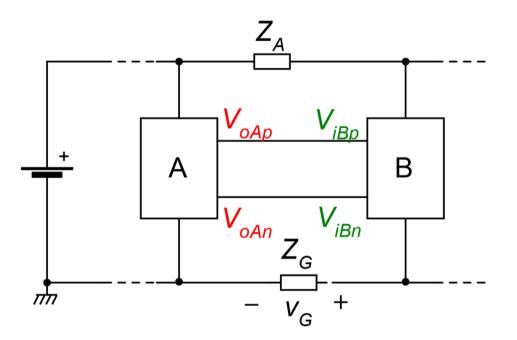

#### Immunity of differential architectures to non-uniform gnd potential

The wires that carry the signals do not experience significant voltage drops, since the currents that pass through them is generally negligible.

$$v_{iBd} = v_{iBp} - v_{iBn}$$

$$\begin{cases} v_{iBp} = v_{oAp} - v_{G} \\ v_{iBn} = v_{oAn} - v_{G} \end{cases}$$

Block B Diff. input

Differential components (signals)

$$v_{iBd} = v_{oAd}$$

Common mode components

$$v_{iBc} = v_{oAc} - v_G$$

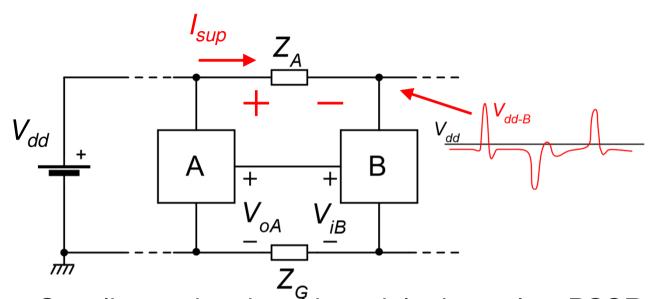

#### $V_{dd}$ variations

The cause of  $V_{dd}$  variation is the same that produces the *gnd* non-uniformity. The effect on the signal is smaller, since  $V_{dd}$  is not commonly used as a reference for block-to-block signal transmission.

Coupling to the signal is mainly due to low PSSR. Single ended blocks have a PSSR that decreases steeply at high frequencies.

Note that the  $V_{dd}$  variation experienced by block B can be caused by the supply current of blocks A and B themselves. This initial  $V_{dd}$  variation can cause an additional supply current variation which, in turn, cause another  $V_{dd}$  variation, and so on. This effect may result in an **unstable feedback loop**.

#### Just a look to datasheets

....

#### **OPERATING CHARACTERISTICS**

The OPA377 family of amplifiers has parameters that are fully specified from 2.2V to 5.5V (±1.1V to ±2.75V). Many of the specifications apply from –40°C to +125°C. Parameters that can exhibit significant variance with regard to operating voltage or temperature are presented in the Typical Characteristics.

#### **GENERAL LAYOUT GUIDELINES**

For best operational performance of the device, good printed circuit board (PCB) layout practices are required. Low-loss,  $0.1\mu F$  bypass capacitors must be connected between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable to single-supply applications.

$R_2$   $10k\Omega$   $C_1$  100nF  $V_{IN}$   $V_{CM} = 2.5V$

100 nF

Impulsive and high frequency currents (zero mean) are provided by the capacitor and do not run through the interconnections

#### BASIC AMPLIFIER CONFIGURATIONS

This practice can be also applied inside integrated circuits, but the small values of on-chip capacitors make it effective only for very high frequency components and comes at the expense of large area occupation.

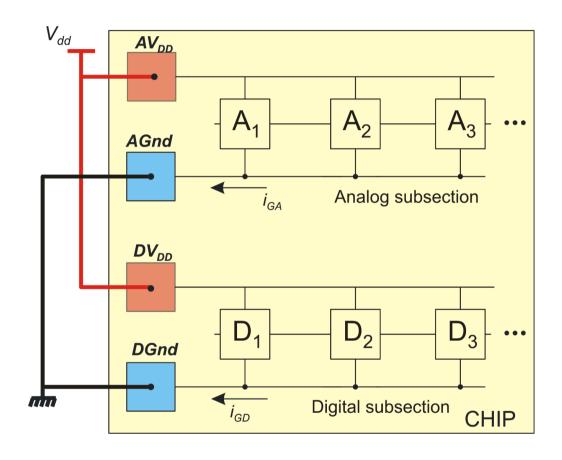

#### Optimal ground and Vdd distribution in mixed signal ICs.

Sensitive cells, such as analog blocks and noisy circuits, such as digital subunits should be provided of separate gnd and Vdd power buses. The AGnd (analog gnd) and DGnd (digital gnd) will be connected in a single point, as close as possible to the gnd pad. Even better, they may have separate pads and the connection is made on the PCB.

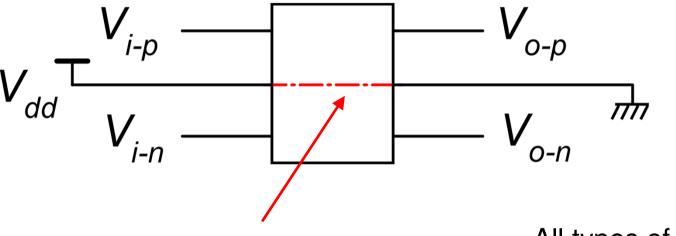

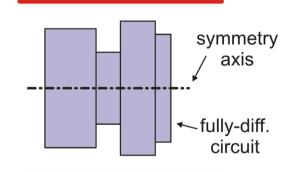

#### PSSR and CMRR characteristics of fully differential blocks

Symmetry axis

Symmetrical stimuli

- Gnd potential variations

- Vdd variations

- Common mode signals

- Global process errors

All types of symmetrical stimuli cannot produce any effect on the differential output voltage if the circuit is perfectly symmetric.

A reduced amount of leakage from symmetrical stimuli and differential quantities can be due to the unavoidable asymmetries caused by (1) process errors and (2) presence of large differential components due to large input signals.

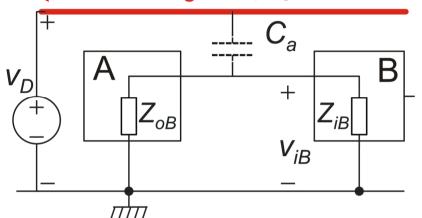

#### Interference capacitive coupling

interfering line (e.g. a clock line)

$$Z_{a} = \frac{1}{j\omega C_{a}} \qquad \text{if } |Z_{a}| >> |Z_{oA} / / Z_{iB}|$$

$$V_{iB} = V_{D} \frac{Z_{oA} / / Z_{iB}}{Z_{oA} / / Z_{iB} + Z_{a}} \cong V_{D} \frac{Z_{oA} / / Z_{iB}}{Z_{a}}$$

It is possible to exploit the symmetry of a fully-differential block to get same interference signals on the two wires that form the input and output ports. To obtain this a symmetrical layout and environment is essential.

#### interfering line

interfering line (duplicated)

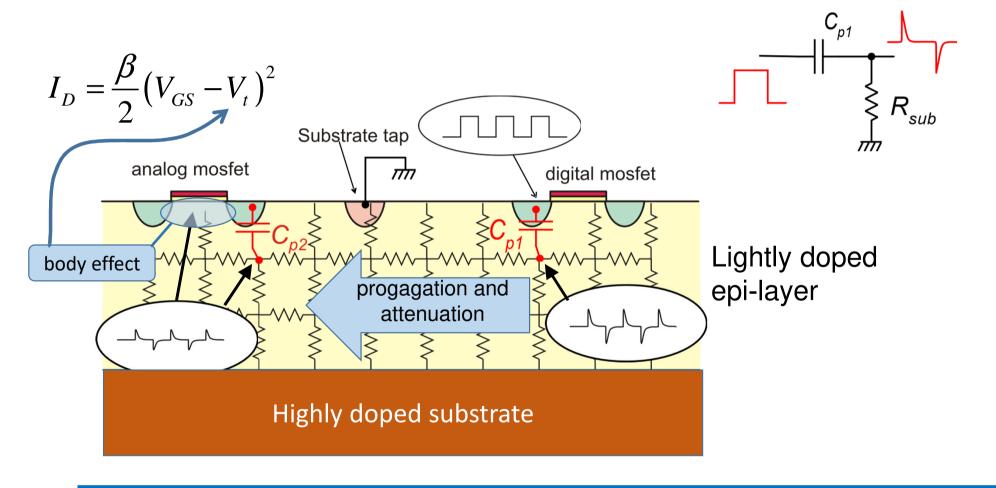

#### The substrate noise

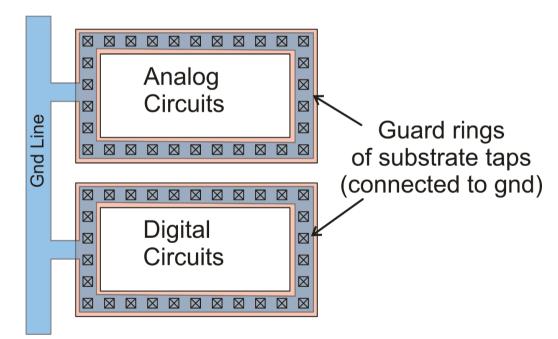

#### Approaches to reduce substrate noise

- Separate as much as possible the digital and analog circuit

- Use guard rings of substrate taps to reduce propagation

If the sensitive circuits (e.g. analog circuits) and the interference source (i.e. digital circuits) are sufficiently far apart, then substrate noise can be considered uniform over the area of the sensitive circuit.

In <u>fully-differential architectures</u>, it acts as a common mode interference and is rejected

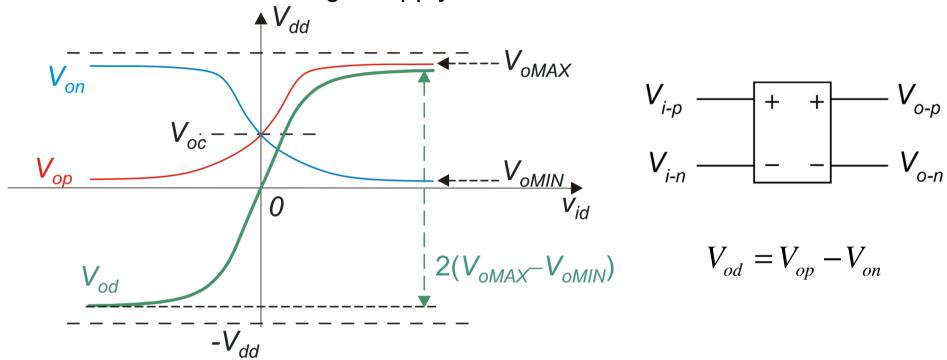

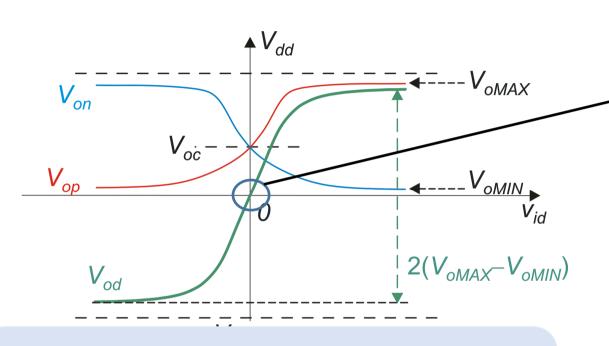

#### Other advantages of fully-differential circuits: double output range

Let us consider a single supply case

Each single output ( $V_{on}$ ,  $V_{op}$ ) has a range  $\Delta V_{o-se} = V_{oMAX} - V_{oMNIN}$

The differentia output  $(V_{op}-V_{op})$  has a range  $\Delta V_{o-fd}=2(V_{oMAX}-V_{oMNIN})$

#### Other advantages of fully-differential circuits: increased linearity

The single outputs (Von, Vop), in principle, have no symmetries, then all terms are generally present in the Taylor polynomial

$$V_{od}\left(-V_{in}\right) = -V_{od}\left(V_{in}\right)$$

V<sub>od</sub> has the odd symmetry, then its Taylor polynomial calculated from the origin has no even terms

Greater linearity, lower harmonic distortion (no even harmonics)

# Fully differential circuits: the need for a stabilized output common mode voltage

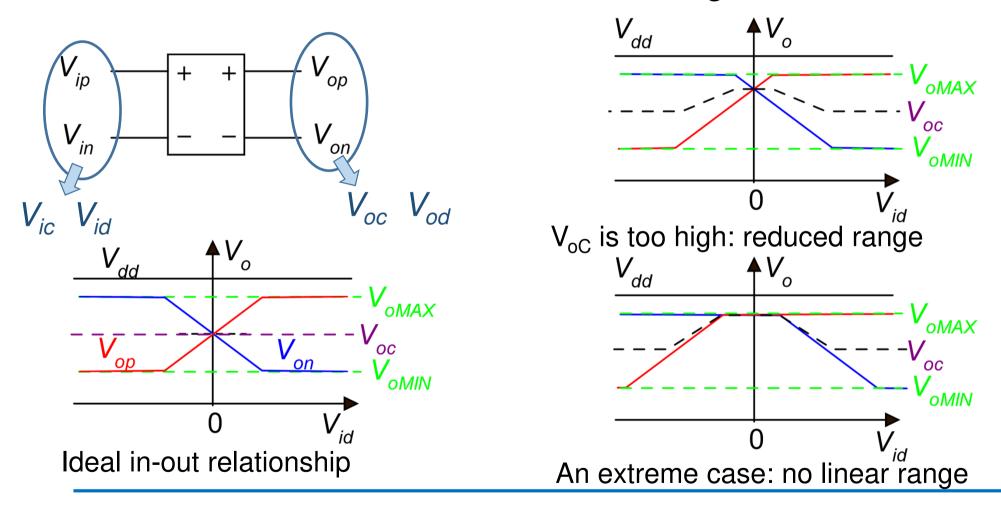

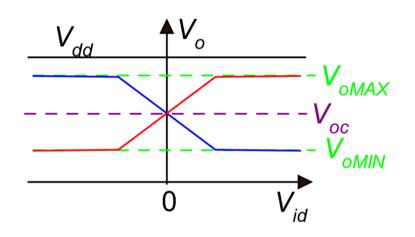

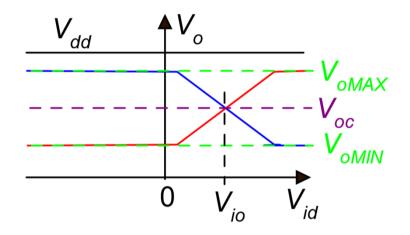

## Input output characteristics in a fully-differential circuit: the correct feasible case

Ideal: zero input offset voltage (not possible, due to process errors) Possible: there is an offset voltage, but the linearity range is still maximum

In the majority of fully-differential cells, the output common mode voltage should be stabilized and fixed to a convenient value.

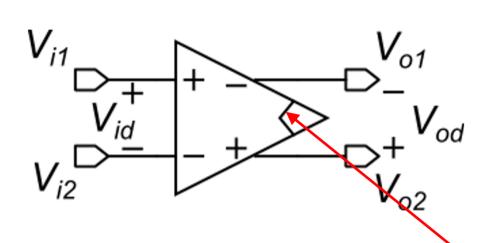

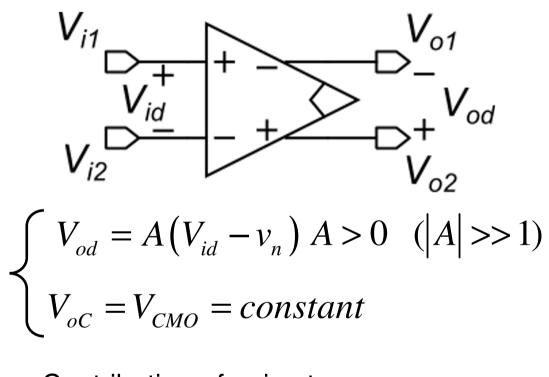

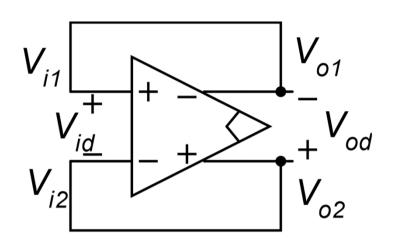

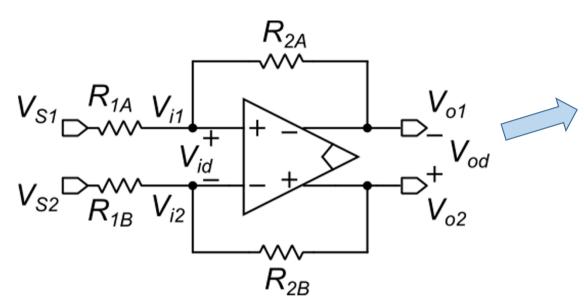

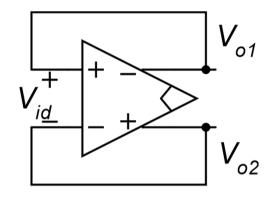

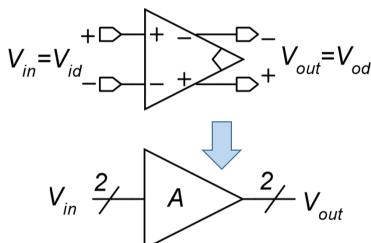

#### The fully-differential operational amplifier: definitions

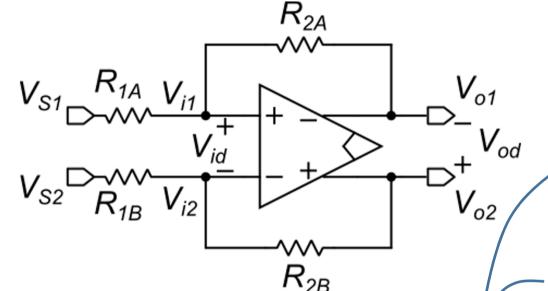

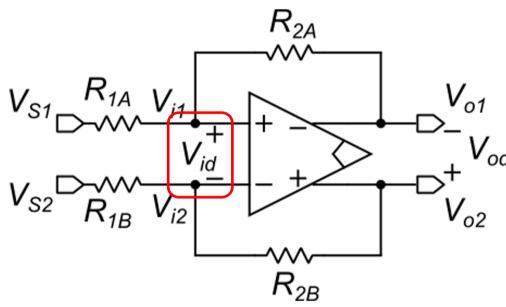

$$\begin{cases} V_{id} = V_{i1} - V_{i2} \\ V_{od} = V_{o2} - V_{o1} \end{cases}$$

$$\begin{cases} V_{id} = V_{i1} - V_{i2} \\ V_{od} = V_{o2} - V_{o1} \end{cases} \qquad \begin{cases} V_{ic} = \frac{V_{i1} + V_{i2}}{2} \\ V_{oc} = \frac{V_{o2} + V_{o1}}{2} \end{cases}$$

The inverting output is placed on the same side of the noninverting input to simplify drawing of closed loop configurations

This symbol means that the amplifier includes a common mode stabilization circuit

### The fully-differential operational amplifier: properties

Closed loop configuration:  $V_{id}$

Contribution of noise to the input differential voltage in closed loop

$$V_{id} \cong v_n' \equiv \frac{\beta A}{\beta A - 1} v_n \implies$$

Filtered version of the input noise voltage

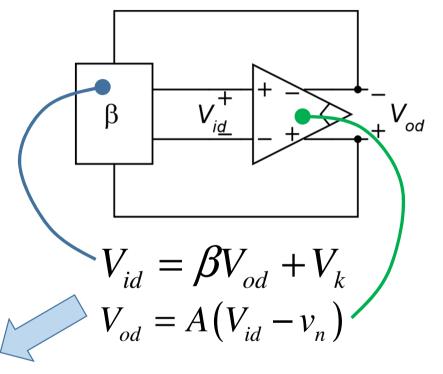

## The "unity-gain" configuration

This is improper because there is no available port to insert a signal.

However, this configuration is particularly useful in switched-capacitor circuits.

$$V_{id} = -V_{od}$$

$\beta = -1$

$$V_{id} \cong V_n \qquad V_{od} \cong -V_n$$

$$V_{ic} = V_{oc} = V_{CMO}$$

$$V_{i1} = V_{CMO} + \frac{v_n}{2}; \quad V_{i2} = V_{CMO} - \frac{v_n}{2}$$

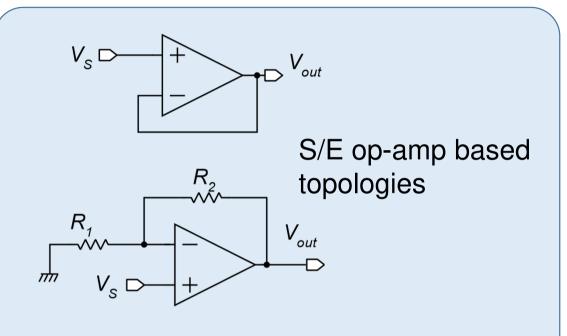

In fully-differential architecture, speaking of inverting and non-inverting topologies is meaningless, since a sign change can be obtained by simply swapping the wires

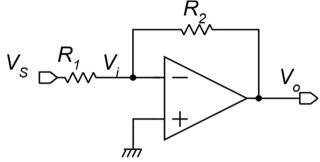

Analogous S/E configuration: inverting amplifier.

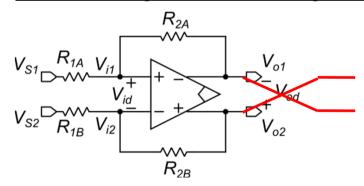

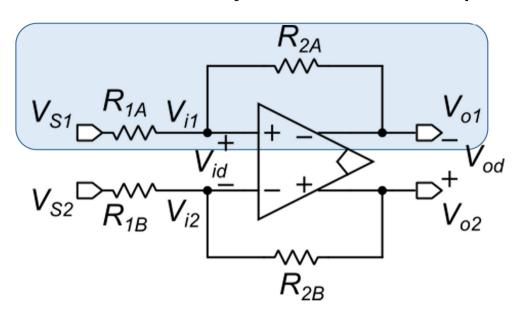

# The fully-diff. version needs twice the passive components

$$V_{S1}$$

$+$

$V_{i1}$

$+$

$V_{o1}$

$$V_{i1} = V_{o1}\beta_1 + V_{S1}(1 - \beta_1)$$

$$V_{i2} = V_{o2}\beta_2 + V_{S2}(1 - \beta_2)$$

$$\beta_1 = \frac{R_{1A}}{R_{1A} + R_{2A}}$$

$$\beta_2 = \frac{R_{1B}}{R_{1B} + R_{2B}}$$

$$V_{i1} = V_{o} \left[ \frac{R_{1A}}{R_{1A} + R_{2A}} \right] + V_{S1} \left[ \frac{R_{2A}}{R_{1A} + R_{2A}} \right]$$

$$\beta_{1} \qquad 1 - \beta_{1}$$

$\beta_1 = \frac{R_{1A}}{R_{1A} + R_{2A}}$   $\beta_2 = \frac{R_{1B}}{R_{1B} + R_{2B}}$

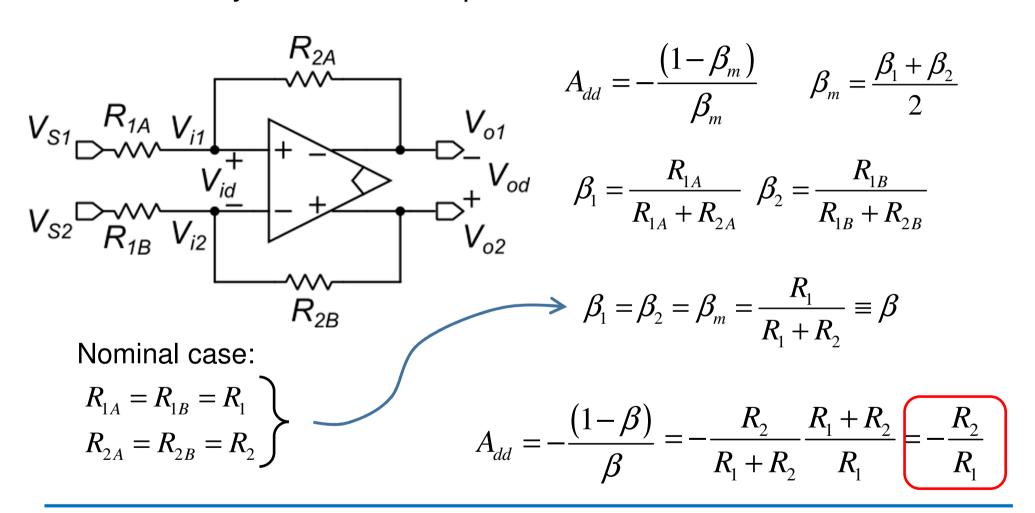

Nominally  $\beta_1 = \beta_2$ , but unavoidable process errors (local errors) make them different

It is convenient to split the two coefficients as a mean value and a difference:

$$\beta_1 = \beta_m + \frac{\Delta \beta}{2}; \quad \beta_2 = \beta_m - \frac{\Delta \beta}{2}$$

$$\begin{cases} V_{i1} = V_{o1}\beta_{1} + V_{S1}(1 - \beta_{1}) \\ V_{i2} = V_{o2}\beta_{2} + V_{S2}(1 - \beta_{2}) \end{cases}$$

$$\begin{cases} V_{i1} = V_{o1}\left(\beta_{m} + \frac{\Delta\beta}{2}\right) + V_{S1}\left(1 - \beta_{m} - \frac{\Delta\beta}{2}\right) \\ V_{i2} = V_{o2}\left(\beta_{m} - \frac{\Delta\beta}{2}\right) + V_{S2}\left(1 - \beta_{m} + \frac{\Delta\beta}{2}\right) \end{cases}$$

Differential mode analysis

$$\begin{cases} V_{i1} = V_{o1} \left( \beta_{m} + \frac{\Delta \beta}{2} \right) + V_{SI} \left( 1 - \beta_{m} - \frac{\Delta \beta}{2} \right) - \\ V_{i2} = V_{o2} \left( \beta_{m} - \frac{\Delta \beta}{2} \right) + V_{S2} \left( 1 - \beta_{m} + \frac{\Delta \beta}{2} \right) + \\ V_{i2} - V_{i1} = \left( V_{o2} - V_{o1} \right) \beta_{m} - \left( \frac{V_{o1} + V_{o2}}{2} \right) \Delta \beta + \left( V_{S2} - V_{S1} \right) \left( 1 - \beta_{m} \right) + \frac{V_{S1} + V_{S2}}{2} \Delta \beta \end{cases}$$

$$V_{i2} - V_{i1} = V_{od} \beta_{m} - V_{oc} \Delta \beta + V_{Sd} \left( 1 - \beta_{m} \right) + V_{Sc} \Delta \beta$$

$-V_{id} \cong -V_n$

$$-v_{n} = V_{od}\beta_{m} - V_{oc}\Delta\beta + V_{Sd}(1 - \beta_{m}) + V_{Sc}\Delta\beta \qquad v_{od-noise} = -\frac{v_{n}}{\beta_{m}}$$

$$-V_{od}\beta_{m} = +v_{n} + V_{Sd}(1 - \beta_{m}) + (V_{Sc} - V_{oc})\Delta\beta \qquad v_{od-noise} = -\frac{v_{n}}{\beta_{m}}$$

$$V_{od} = -\frac{v_{n}}{\beta_{m}} - V_{Sd}\frac{(1 - \beta_{m})}{\beta_{m}} - (V_{Sc} - V_{oc})\frac{\Delta\beta}{\beta_{m}} \qquad A_{dd} = -\frac{(1 - \beta_{m})}{\beta_{m}}$$

$$V_{Sd} \xrightarrow{A_{cd}} V_{od} \qquad A_{cd} = -\frac{\Delta\beta}{\beta_{m}} \quad \text{relative matching error}$$

$$V_{Sc} \longrightarrow V_{oc} = V_{CMO} \qquad CMRR = \left| \frac{A_{dd}}{A_{cd}} \right| = |A_{dd}| \cdot \left| \frac{\Delta\beta}{\beta_{m}} \right|^{-1}$$

We do not know the input common mode voltage

$$V_{ic} = \beta V_{CMO} + (1 - \beta) v_{Sc}$$

$$\begin{cases} v_{i1} = v_{o1} \left(\beta_m + \frac{\Delta \beta}{2}\right) + v_{S1} \left(1 - \beta_m - \frac{\Delta \beta}{2}\right) \times \frac{1}{2} \\ v_{i2} = v_{o2} \left(\beta_m - \frac{\Delta \beta}{2}\right) + v_{S2} \left(1 - \beta_m + \frac{\Delta \beta}{2}\right) \times \frac{1}{2} \end{cases}$$

Generally, determination of the common mode voltage does not require high accuracy. We can use the nominal case.

$$\begin{cases} \beta_m = \beta \\ \Delta \beta = 0 \end{cases}$$

We have to check that for all possible values of  $V_{SC}$ , the input common mode voltage does not exceed the amplifier input CM range

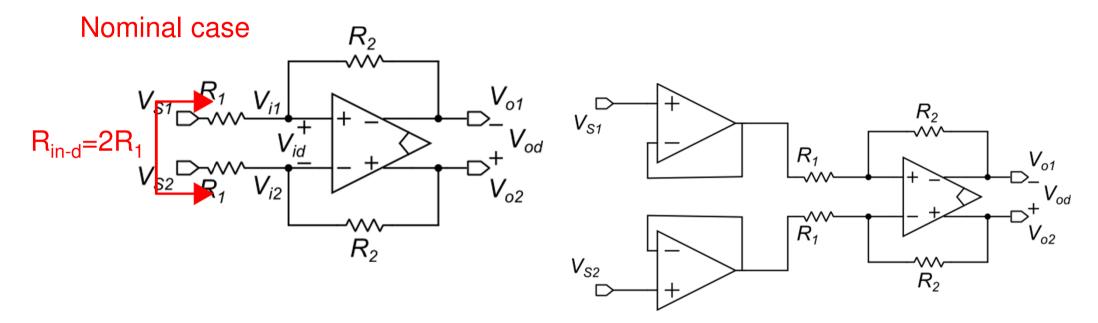

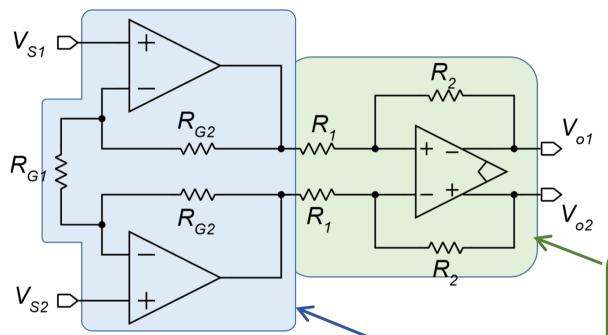

### 3-op-amp fully-differential instrumentation amplifier

This circuit alone cannot be used as an instrumentation amplifier since it has too low an input resistance We could use input buffers built with single-ended operational amplifiers. But there is a more versatile option ...

### 3-op-amp fully-differential instrumentation amplifier

$$V_{o1}$$

$A_{dd-tot} = -\left(1 + 2\frac{R_{G2}}{R_{G1}}\right)\frac{R_2}{R_1}$

$A_{dd1} = 1 + 2\frac{R_{G2}}{R_{G1}}$   $A_{cc1} = 1$  First stage: is identical to the first stage of the single-ended in-amp

Second stage: reject the input common mode voltage and produces a stabilized output common mode voltage.

Often its gain is set to 1

#### Versatility <u>limits</u> of the fully-differential operational amplifier

These are topologies that present a <u>high input resistance</u>. They cannot be implemented in the fully differential domain using an FD op-amp.

For example, the fully-differential unity-gain configuration, differently from its S/E counterpart, cannot work as a buffer. There is not an input port available for the signal.

#### Versatility <u>limits</u> of the fully-differential operational amplifier

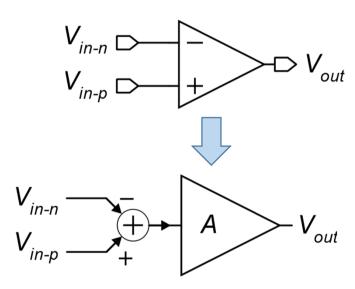

Single ended op-amp (electrical symbol)

Functional representation

Fully-differential op-amp (electrical symbol)

Functional representation: in fully differential architectures every wire pair is a single signal

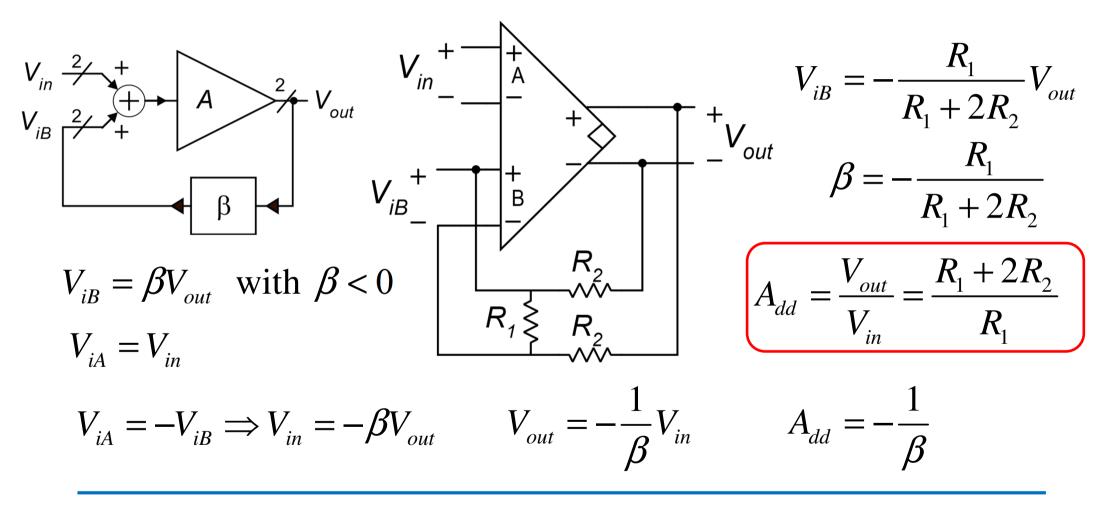

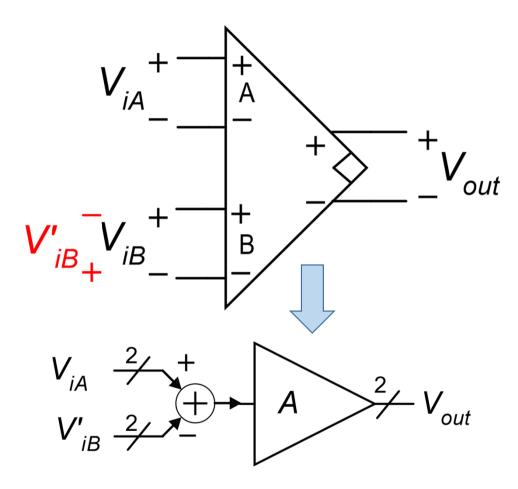

#### The DDA: Difference Differential Amplifier

$$V_{out} = A(V_A + V_B)$$

$$V_{out} = A(V_{iA} - V'_{iB})$$

$$\frac{V_{out}}{A} = (V_{iA} - V'_{iB})$$

In a closed loop configuration, if the circuit is stable and the amplifier is in its linearity range (A>>1):

$$V_{iA} \cong V'_{iB} = -V_{iB}$$

This is the equivalent of the virtual short circuit in DDAs. Note that, individually  $V_{iA}$  and  $V_{iB}$  can be large

### DDA-based instrumentation amplifier