# Single-Ended operational amplifiers

Typical requirements

- Voltage amplifiers

- Very large DC gain

- Stability over a wide range of negative feedback conditions.

- High input impedance on both inputs

- Differential input

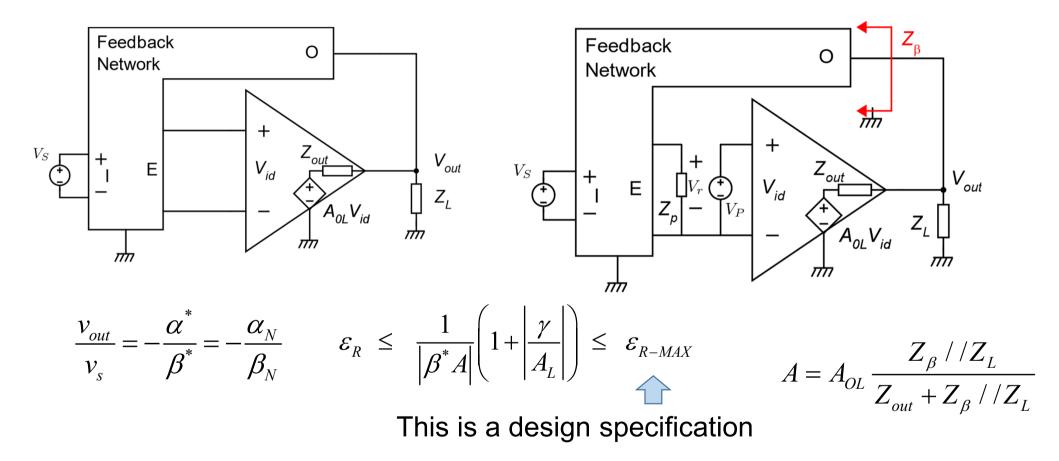

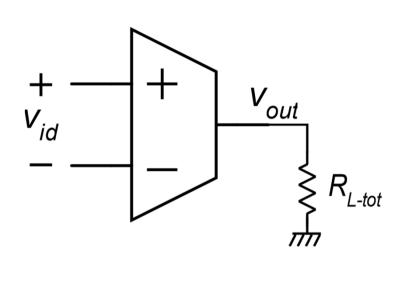

# Typical op-amp-based negative feedback loop

Requirement on the output impedance

$$\frac{1}{\left|\beta^*A\right|} \left(1 + \left|\frac{\gamma}{A_L}\right|\right) \le \varepsilon_{R-MAX} \qquad A = A_{OL} \frac{Z_{\beta} / Z_L}{Z_{out} + Z_{\beta} / Z_L}$$

$Z_{out}$  should be low enough to guarantee that A is large enough to maintain the relative error below the maximum value allowed in all the expected load conditions

load :

$$Z_{\beta} / Z_{L}$$

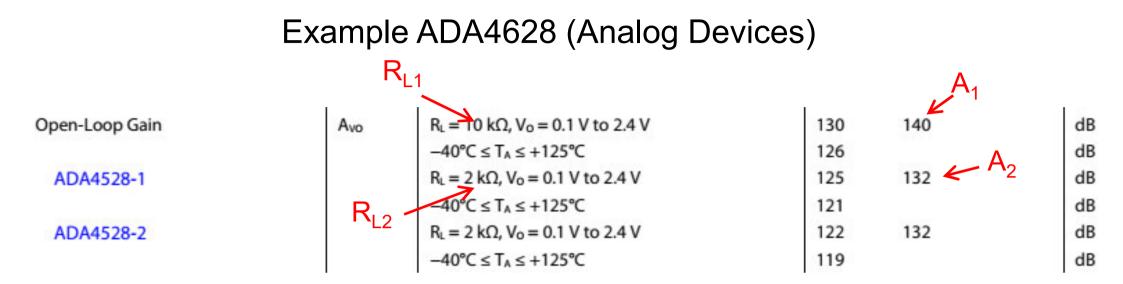

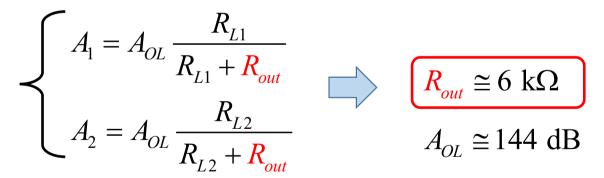

Passing from  $R_L$ =10k $\Omega$  to  $R_L$ =2 k $\Omega$  the amplifier loses around 8 dB of gain

**Output stages - specifications**

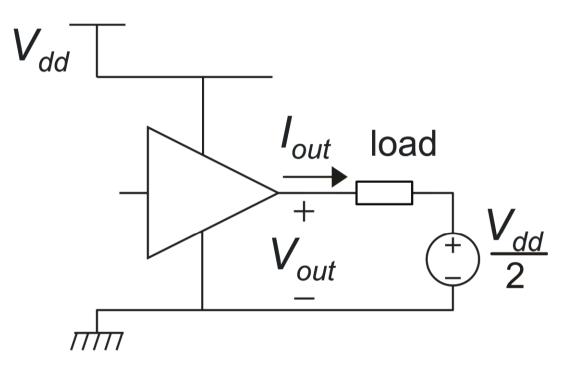

# Single supply case

Single power supply

In a single supply voltage circuit, the load cannot be connected to *gnd* (or  $V_{dd}$ ) if we want a to impose both positive and negative voltages across it.

To achieve this result, the load should be applied across the amplifier output port and a proper constant voltage, typically equal to  $V_{dd}/2$ .

This voltage must be generated by a proper cell, starting from  $V_{dd}$ .

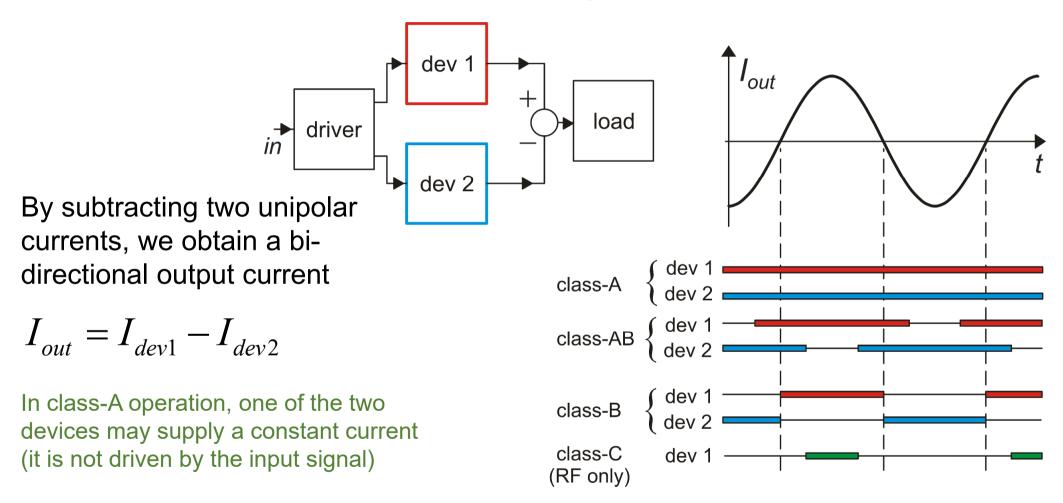

#### Output stage classes

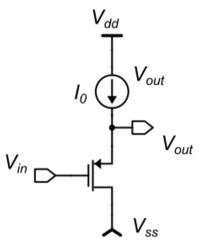

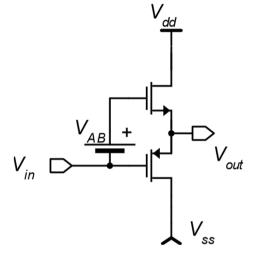

# Recap of source follower output stages

n-type source follower:

$$\Delta V_H = V_{GS}$$

Loses a  $V_{GS}$  from  $V_{dd}$

p-type source follower:

$$\Delta V_L = \left| V_{GS} \right|$$

Loses a  $V_{GS}$  from  $V_{SS}$

$$\Delta V_H = V_{GS}$$

$$\Delta V_L = \left| V_{GS} \right|$$

Class-AB source follower: loses a  $V_{GS}$  from both rails

Source follower stages are not compatible with a wide swing output range

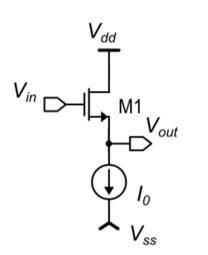

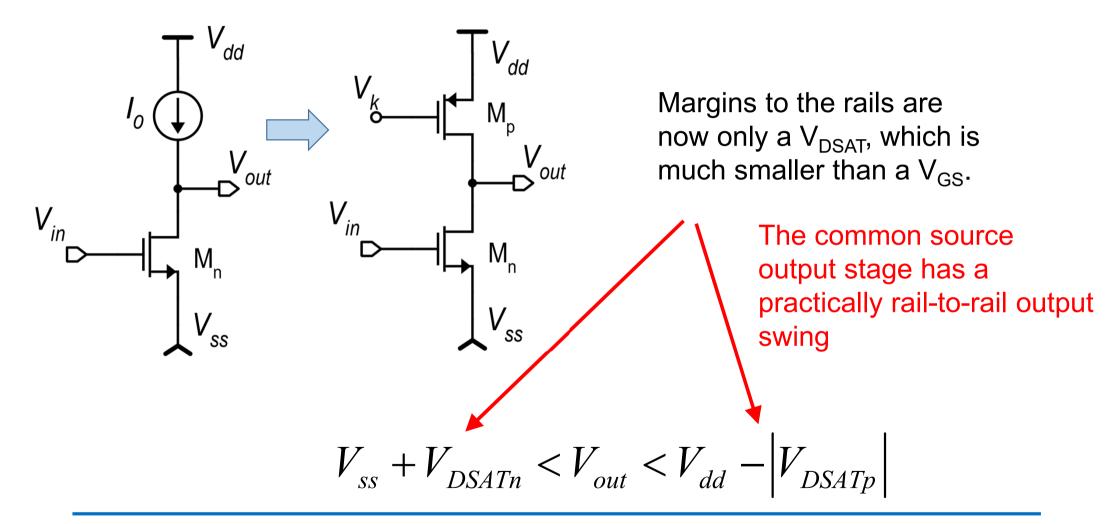

#### Common source output stages: class-A case

#### Other info on the class-A common source

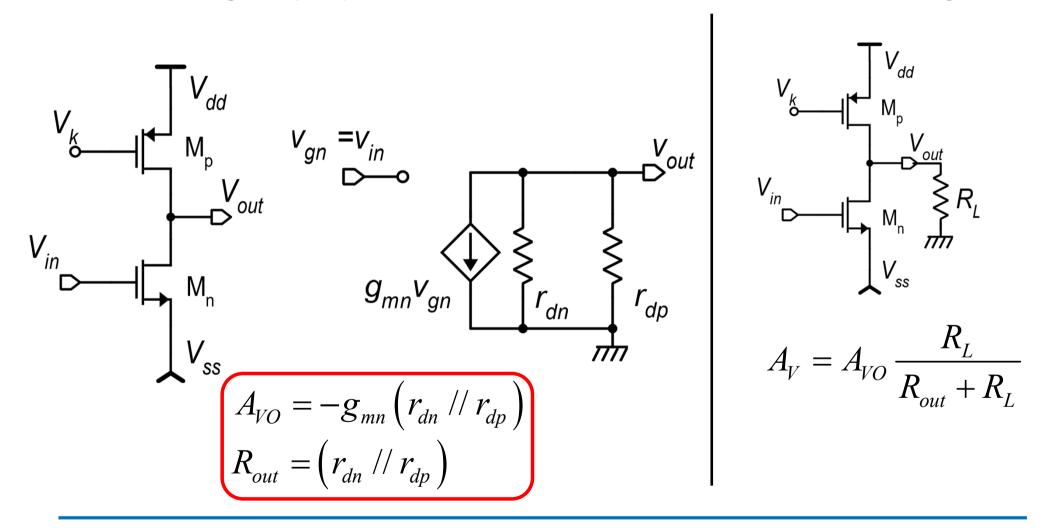

### Small signal properties of the class-A common source stage

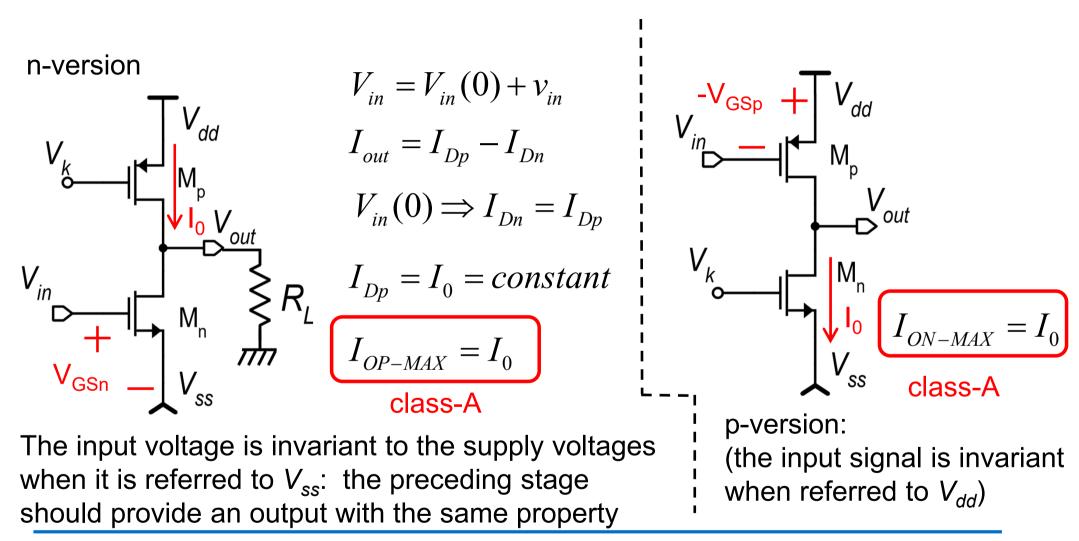

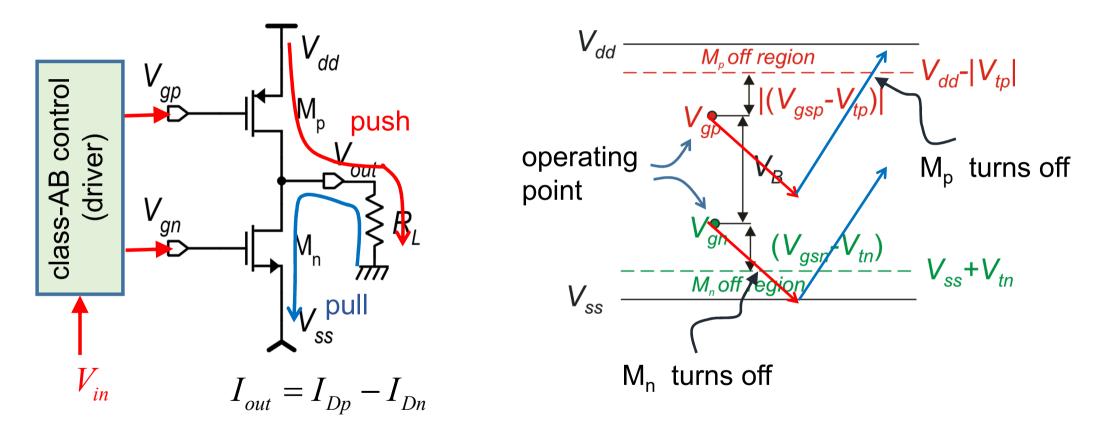

#### Class-AB common source: principle of operation

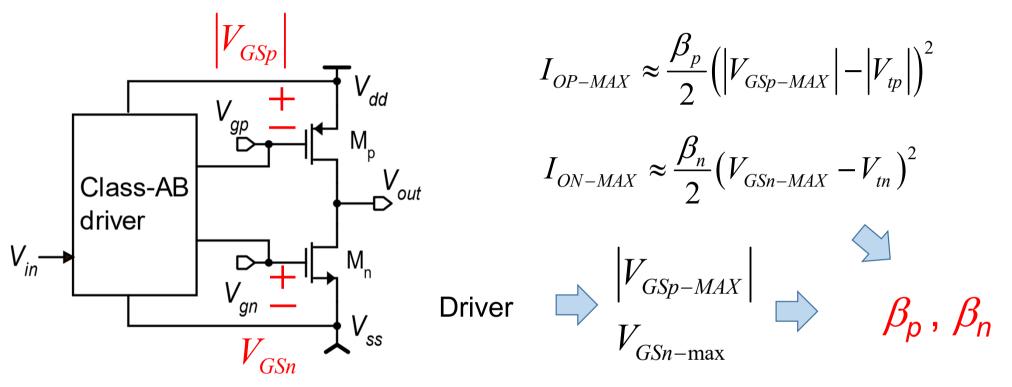

Class-AB common-source output stages: maximum output currents

Different topologies are available for the class-AB driver. They differ for the maximum  $V_{GS}$  that can be delivered to  $M_p$  and  $M_n$  and for the minimum supply voltage

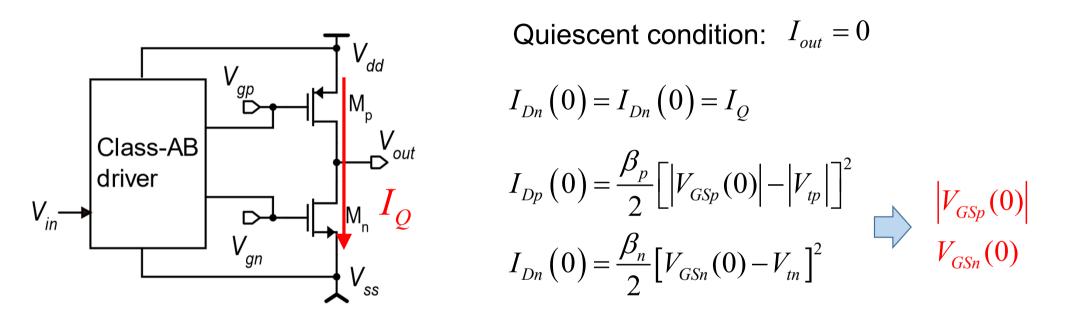

#### Class-AB common-source output stages: quiescent current

The driver must be able to set the quiescent current with a good accuracy, since  $I_Q$  sets the <u>operating point power</u> <u>consumption</u> and the <u>small signal performances</u> of the stage

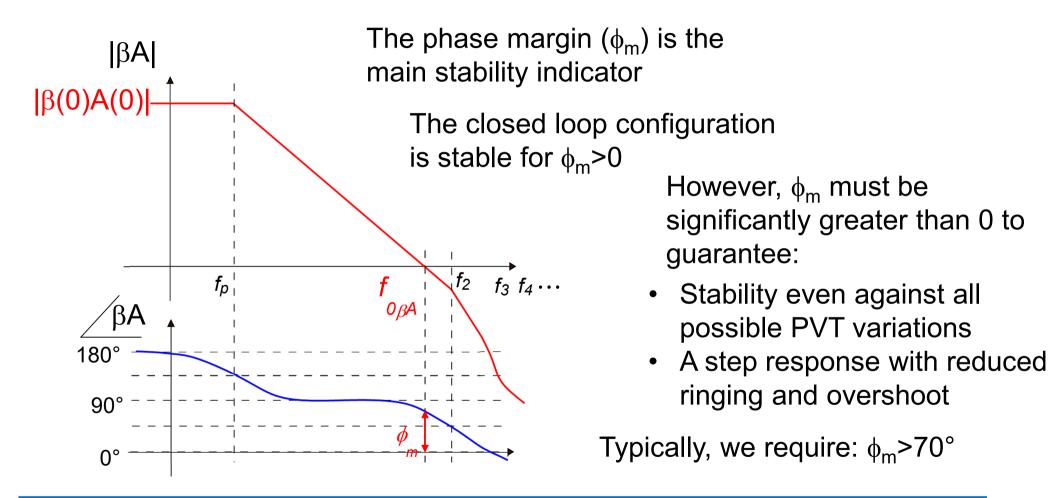

Frequency response requirements: closed loop gain ( $\beta A$ )

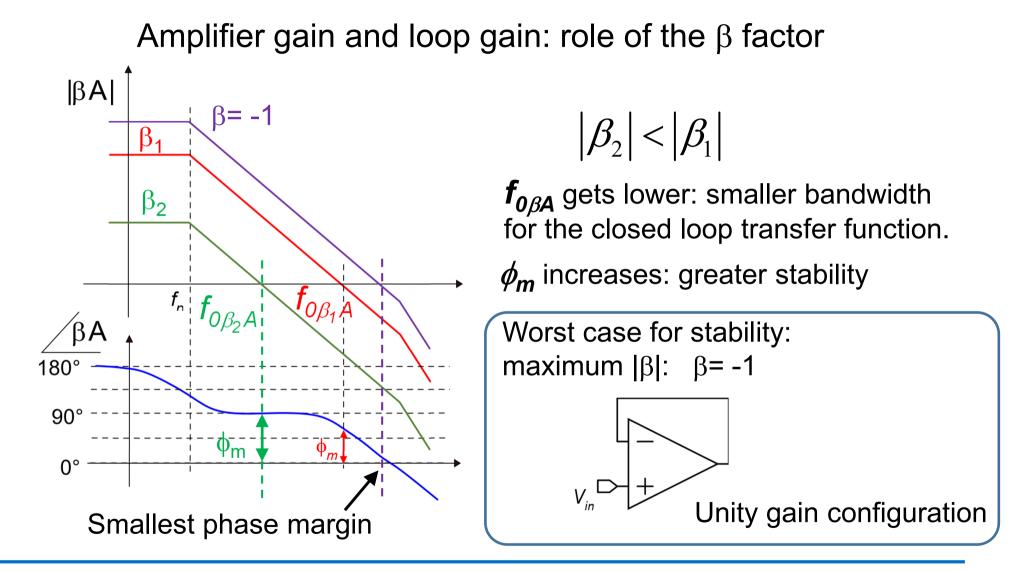

### Amplifier gain and loop gain: role of the $\beta$ factor

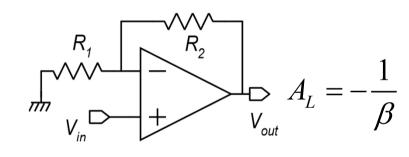

we consider the case:  $\beta = real \ constant < 0$ A(0) > 0βΑ (for d.c. stability) resistor-only or capacitor-only  $|\beta| \le 1$ feedback networks  $f_{0\beta A} = f_0 \left| \beta \right|$  $f_0$  is the unity gain frequency of the amplifier, equal to GBW (Gain-0<sub>B</sub>A BandWidth for a dominant pole 180° response In this case,  $f_{0bA}$  represents the -90° 3dB upper band limit of the closed 0° loop transfer function.

#### Example of non-unity-gain stable op-amp

Stability for gains  $\geq 6 \Longrightarrow \beta \leq \frac{1}{6}$  for non-inverting amplifiers config.

The advantage is a large GBW

Texas Instruments

OPA607, OPA2607 SBOS981G - OCTOBER 2019 - REVISED OCTOBER 2020

OPAx607 50-MHz, Low-Power, Gain of 6-V/V Stable, Rail-to-Rail Output CMOS for Cost Sensitive Systems

#### 1 Features

- Gain Bandwidth Product (GBW): 50 MHz

- Quiescent Current: 900 µA (Typical)

- Broadband Noise: 3.8 nV/\/Hz

- Input Offset Drift: 1.5 µV/°C (Maximum)

- Offset Voltage: 120 µV (Typical)

- Input Bias Current: 10 pA (Maximum)

- Rail-to-Rail Output (RRO)

- Decompensated, Gain ≥ 6 V/V (Stable)

- Power Down Current: 1 µA (Maximum)

- Supply Range : 2.2 V to 5.5 V

- 2 Applications

#### **3 Description**

The OPA607 and OPA2607 devices are decompensated, minimum gain of 6 V/V stable, general-purpose CMOS operational amplifier with low noise of 3.8 nV/√ Hz and a GBW of 50 MHz. The low noise and wide bandwidth of the OPAx607 devices make them attractive for general-purpose applications which require a good balance between cost and performance. The high-impedance CMOS inputs make the OPAx607 devices an ideal amplifier to interface with sensors with high output impedance (for example, piezoelectric transducers).

The OPAx607 devices feature a Power Down mode with a maximum quiescent current of less than 1 uA

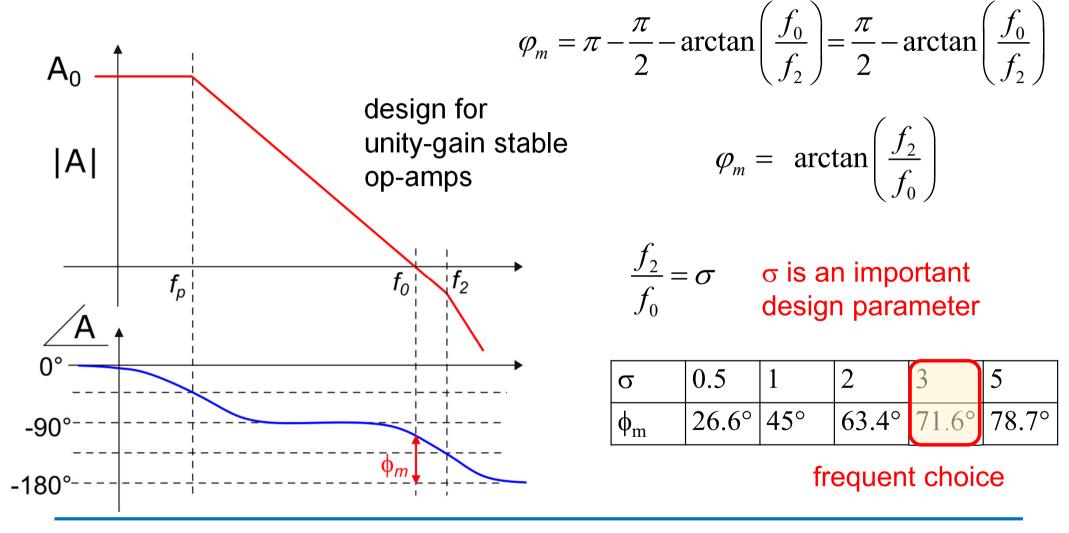

Single non-dominant pole case

Design specifications for the amplifier response speed

• Gain-BandWidth product (GBW)

For a <u>single pole</u> frequency response:

- **1.**  $GBW \cong f_0$

- 2. In a closed loop configuration, the upper band limit is given by:  $f_H = GBW \cdot |\beta|$

- 3. For the non-inverting amplifier:  $f_H = \frac{GBW}{4}$

The same relationships are approximately valid for <u>dominant-pole</u> frequency responses

• Slew rate ( $s_R$ ): this is the maximum slope that can be obtained from the output voltage. The slew rate affects the behavior for large and fast input transients

# A possible set of specification for design of a CMOS op-amp

- dc gain  $A_0$

- Speed: Gain-Band-Width product (*GBW*) and Slew rate  $(s_R)$

- Closed loop stability: e.g. phase margin in unity gain configuration and with a maximum capacitive load (C<sub>L</sub>)

- Input referred voltage noise: Thermal :  $S_{vT}$ , Flicker:  $k_F = fS_{vF}(f)$

- Offset (Input offset voltage: V<sub>io</sub>)

- Static power consumption ( $I_{supply}$ , minimum  $V_{dd}$ )

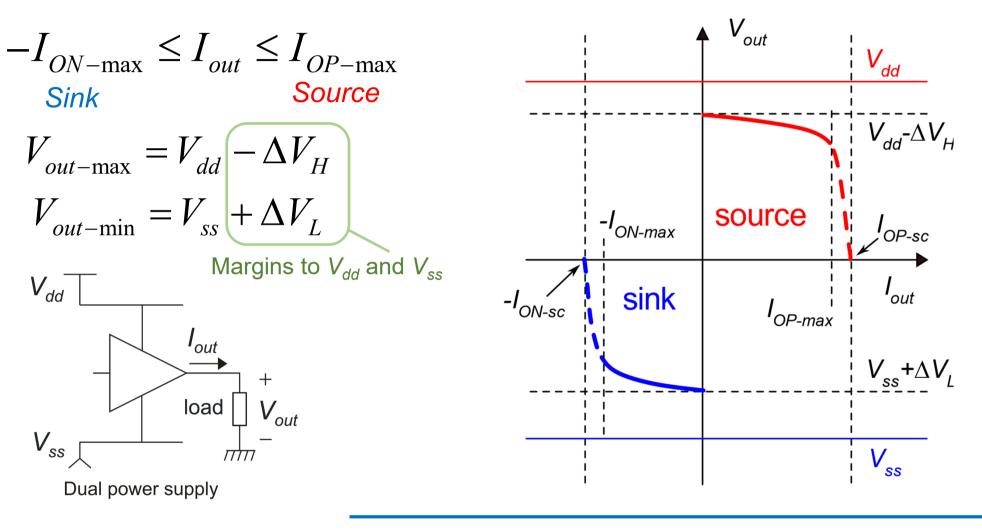

- Maximum output current *I*<sub>OP-max</sub>, *I*<sub>ON-max</sub>

- Ranges: Input common mode range (CMR), output swing.

- CMRR, PSRR

- Area

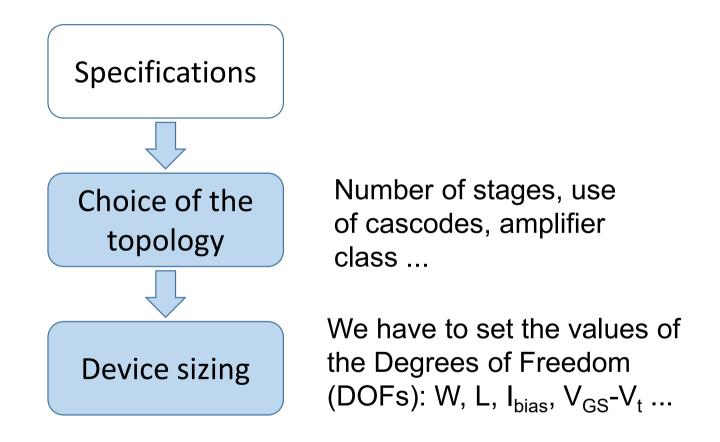

# Design of an anolog cell: phases

Operational amplifiers: number of stages

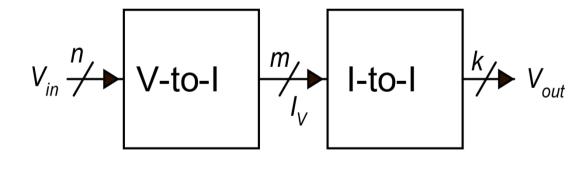

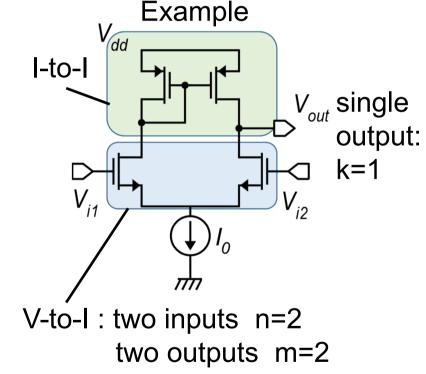

In the op-amp design terminology, the number of stages refer only to gain stages.

A gain stage is formed by a V-to-I converter and a network I-to-I that brings the output current(s) of the V-to-I converter to the output port.

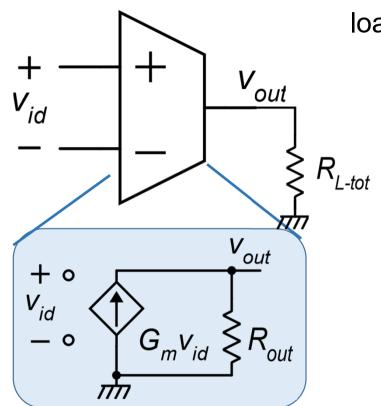

Single stage op-amps

In the case of no resistive load (only capacitive load, as in switched-cap. circuits:

$$A_{OL}(0) = G_m R_{out}$$

With very large  $R_{out}$  values, gains up to 100 dB can be obtained (cascode and regulated cascode architectures)

In the case of resistive loads, the gain falls down to

$$A_{OL}(0) = G_m \left( R_{out} / R_{L-tot} \right)$$

Includes the load brought by the feedback network

Single stage op-amps with resistive load

$$A_{OL}(0) = G_m \left( R_{out} / R_{L-tot} \right)$$

for  $R_{L-tot} << R_{out}$  $A_{OL}(0) \cong G_m R_{L-tot}$

Can be as low as several tens of  $k\Omega$

In single gain stages,  $G_m$  coincides with the transconductance  $(g_m)$  of a single device or is a linear combination of device transconductances

In most practical cases, loading a single stage op-amp with an even **moderate resistive loads** means reducing the gain **to very small values**, not suitable for op-amp closed loop applications.

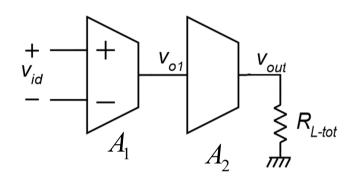

#### Two-stage op-amps

$$A_{1} = G_{m1}R_{o1} \quad (40 \text{ dB} - 100 \text{ dB})$$

$$A_{2} = G_{m2} \left( R_{out} / / R_{L-tot} \right)$$

$$A_{OL} \left( 0 \right) = A_{1} \cdot A_{2}$$

- The resistive loads affects only the gain of the second stage.

- Even in the case that the gain of the second stage falls down to a few units, the total dc gain remains as large as to be suitable for most closed-loop configurations.

- The second stage is the output stage and must be designed to provide the required current and voltage ranges to the load.

# Considerations on the op-amp number of stages

- **Single stage op-amps:** they can be designed to provide enough gain for a large variety of applications only in the case that the load and the feedback networks are capacitive (switched capacitor circuits). Their advantage is their simple frequency compensation and their power efficiency. Their stability increases with large capacitive loads.

- **Two-stage amplifiers:** they are the most popular options for general purpose op-amps since they are suitable for both capacitive and resistive loads and can be designed to provide very large dc gains. Their stability decreases with large capacitive loads.

- **Three-stage amplifiers:** this option is necessary when two-stage amplifiers cannot provide enough gain. This is the case, for example of very low supply voltages that prevent the use of cascodes. The gain of two-stage amplifiers can be too low also in the case of very fast op-amps, where the gain of each single stage is limited by the necessity to use short-length MOSFETs.

Three stage amplifiers requires complicated frequency compensation strategies, such as the nested-Miller compensation combined with feed-forward paths (multi-path architectures)