## PROVA SCRITTA di DISPOSITIVI ELETTRONICI del 3 Febbraio 2018

#### ESERCIZIO 1

In figura è rappresentato un pezzo di silicio, drogato da una parte  $n^+$   $(N_D = 10^{19} \text{ cm}^{-3}, \mu_{n+} = 0.015 \text{ m}^{-3})$  e dall'altra n  $(N_D = 10^{15} \text{ cm}^{-3}, \mu_n = 0.12 \text{ m}^{-3})$ . Le due lunghezze sono  $L_{n+} = 5 \text{ mm}$  e  $L_n = 100 \mu \text{m}$ , mentre la sezione è 1 mm<sup>2</sup>.

- 1) Determinare l'altezza di barriera che si viene a generare tra le due regioni, e la corrente per V=1 V. SUGGERIMENTO: tenere a mente l'andamento delle bande. [4]

- 2) Per una temperatura T = 900 °C, determinare l'altezza di barriera. SUGGERIMENTO: calcolare  $n_i$ . (Trascurare la diffusione delle specie droganti). [3]

- 3) Assumere che la mobilità degli elettroni sia costante con la temperatura nella regione  $n^+$ . Nella regione n avremo che, a 900 °C,  $\mu_n = 0.08$  e  $\mu_p = 0.03$ . Determinare la corrente per V = 1 V. [3]

### ESERCIZIO 2

Si consideri un transistore n-MOS polysilicon gate con  $t_{ox}=30$  nm,  $N_A=5\times 10^{15}$  cm<sup>-3</sup>, L=5  $\mu$ m, W=10  $\mu$ m. Il source è polarizzato rispetto al bulk con una tensione  $V_{SB}=5$  V, e  $V_{DS}=0$ .

- 1) Calcolare la tensione di soglia del condensatore n-MOS e del transistore n-MOS. [3]

- 2) Determinare la tensione di Gate  $V_{GB}$  per avere una caduta  $V_{Si} = 5$  V ( $\psi_S = 5$  V) nel silicio (a metà del canale) e calcolare la concentrazione di elettroni all'interfaccia ossido-silicio. [4]

- 3) Per  $V_{GB} = 10$  V calcolare la carica mobile totale nel canale per  $V_{DS} = 0$  e per  $V_{DS} = 5$  V (trascurare la modulazione del canale).[3]

#### ESERCIZIO 3

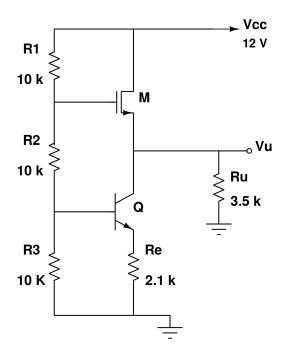

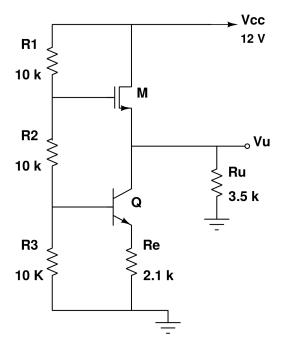

Nel circuito in figura, il transistore M è un n-MOS con  $V_{TH}=1$  V,  $\mu_n=0.08$  cm²/Vs,  $t_{ox}=30$  nm, W/L=22. Q è un transistore bipolare  $n^+pn$ , ed è stato caratterizzato imponendo una  $I_B$  pari a 10  $\mu$  A e  $V_{CE}=5$  V. È stata misurata  $I_C=5$  mA e  $V_{CB}=4.5$  V.

- 1) Sapendo che  $N_{Abase}=10^{16}~{\rm cm^{-3}}$  e  $N_{Dcollettore}=10^{15}~{\rm cm^{-3}},~\mu_n=0.12~{\rm m^2/Vs},~\tau_n=1~\mu{\rm s},$  calcolare la lunghezza effettiva della base e il  $\beta_F$  minimo garantito. [3]

- 2) Determinare il punto di riposo dei transistori e la tensione di uscita.[4]

- 3) Determinare la tensione di collettore di Q per  $R_u \to \infty$ . Se  $R_u = 0$ , i transistori sono polarizzati? [3]

#### ESERCIZIO 1

In figura è rappresentato un pezzo di silicio, drogato da una parte  $n^+$  ( $N_D = 10^{19} \text{ cm}^{-3}$ ,  $\mu_{n+} = 0.015 \text{ m}^{-3}$ ) e dall'altra n ( $N_D = 10^{15} \text{ cm}^{-3}$ ,  $\mu_n = 0.12 \text{ m}^{-3}$ ). Le due lunghezze sono  $L_{n+} = 5 \text{ mm}$  e  $L_n = 100 \mu \text{m}$ , mentre la sezione è 1 mm<sup>2</sup>.

- 1) Determinare l'altezza di barriera che si viene a generare tra le due regioni, e la corrente per V=1 V. SUGGERIMENTO: tenere a mente l'andamento delle bande. [4]

- 2) Per una temperatura T = 900 °C, determinare l'altezza di barriera. SUGGERIMENTO: calcolare  $n_i$ . (Trascurare la diffusione delle specie droganti). [3]

- 3) Assumere che la mobilità degli elettroni sia costante con la temperatura nella regione  $n^+$ . Nella regione n avremo che, a 900 °C,  $\mu_n = 0.08$  e  $\mu_p = 0.03$ . Determinare la corrente per V = 1 V. [3]

SOLUZIONE 1

1) Tra le due regioni si viene a generare una (piccola) barriera, dovuta alla diversa concentrazione di elettroni (che corrisponde alla concentrazione dei droganti. Avremo ( $x_1$  a sinistra lontano dall'interfaccia,  $x_2$  a destra):

$$V(x_2) - V(x_1) = V_T \ln \frac{n(x_1)}{n(x_2)}$$

$$V_0 = V(x_2) - V(x_1) = V_T \ln \frac{N_{Dn}}{N_{Dn^+}} = -0.238 \text{ V}$$

Questa non è una vera barriera, se  $V=1~\rm V$  si alza ma gli elettroni passano andando da destra a sinistra, e vedono quindi una discesa. Quindi i due pezzi di silicio si comportano come due resistenze in serie:

$$R_{n^{+}} = \frac{1}{q\mu_{n^{+}}N_{Dn^{+}}} \frac{L_{n^{+}}}{S} = 0.21 \ \Omega$$

$R_{n} = \frac{1}{q\mu_{n}N_{D}} \frac{L_{n}}{S} = 5.1 \ \Omega$

Quindi la corrente risulta  $I = V/(R_{n^+} + R_n) = 185 \text{ mA}.$

2) Seguendo il suggerimento, vediamo che a 1173 K la parte n è intrinseca, mentre la parte  $n^+$  rimane pesantemente drogata:

$$N_C(1173 \text{ K}) = N_C(300 \text{ K}) \left(\frac{1173}{300}\right)^{\frac{3}{2}} = 2.16 \times 10^{20} \text{ cm}^{-3}$$

$N_V(1173 \text{ K}) = N_V(300 \text{ K}) \left(\frac{1173}{300}\right)^{\frac{3}{2}} = 7.73 \times 10^{19} \text{ cm}^{-3}$

$n_i(1073 \text{ K}) = \sqrt{N_C N_V(1173 \text{ K})} e^{-\frac{E_g}{2kT}} = 6.2 \times 10^{17} \text{ cm}^{-3}$

Quindi l'altezza di barriera è la metà del gap  $(E_g/2q = 0.54 \text{ V})$ , ed è negativa.

3) La resistenza della parte  $n^+$  è la stessa (stessa concentrazione, molto maggiore di quella intrinseca, e stessa mobilità). La parte n si comporta ora come intrinseca, quindi la resistività sarà data sia dalle lacune sia dagli elettroni:

$$\sigma_n = q\mu_n n_i + q\mu_p n_i = 10926 \quad \Omega^{-1} \text{m}^{-1}$$

$$R_n = \frac{1}{sigma_n} \frac{L}{S} = 0.21 \quad \Omega$$

## **ESERCIZIO 2**

Si consideri un transistore n-MOS polysilicon gate con  $t_{ox}=30$  nm,  $N_A=5\times 10^{15}$  cm<sup>-3</sup>, L=5  $\mu$ m, W=10  $\mu$ m. Il source è polarizzato rispetto al bulk con una tensione  $V_{SB}=5$  V, e  $V_{DS}=0$ .

- 1) Calcolare la tensione di soglia del condensatore n-MOS e del transistore n-MOS. [3]

- 2) Determinare la tensione di Gate  $V_{GB}$  per avere una caduta  $V_{Si} = 5$  V ( $\psi_S = 5$  V) nel silicio (a metà del canale) e calcolare la concentrazione di elettroni all'interfaccia ossido-silicio. [4]

- 3) Per  $V_{GB} = 10$  V calcolare la carica mobile totale nel canale per  $V_{DS} = 0$  e per  $V_{DS} = 5$  V (trascurare la modulazione del canale).[3]

1) Poichè il Source è polarizzato rispetto al substrato (bulk), la caduta di tensione nel silicio all'inversione deve essere pari a  $V_{SB} + 2\psi_B$ . La  $V_{TH}$  per il condensatore MOS è riferita al bulk:

$$V_{TH\ cond} = \frac{\sqrt{2\epsilon_s q N_A (V_{SB} + 2\psi_B)}}{C_{ox}} + V_{SB} + 2\psi_B + \Phi_{MS}$$

$$C_{ox} = \frac{\epsilon_{ox}}{t_{ox}} = 1.151 \times 10^{-3} \text{ F/m}^2$$

$$\psi_B = V_T \ln\left(\frac{N_A}{n_i}\right) = 0.329$$

$$\Phi_{MS} = -\frac{E_g}{2q} - \psi_B = -0.869$$

$$V_{TH\ cond} = 5.63 \text{ V}$$

Per il transistore MOS, invece, la tensione di soglia è riferita al Source:

$$V_{TH} = V_{TH \ cond} - V_{SB} = 0.63 \text{ V}$$

(1)

2) Se la caduta di tensione nel silicio è pari a 5 V possiamo scrivere:

$$V_{GB} = \frac{\sqrt{2\epsilon_s q N_A V_{Si}}}{C_{ox}} + V_{Si} + \Phi_{MS} = 4.93 \text{ V}$$

(2)

Da notare che, a causa della  $\Phi_{MS}$ , la tensione applicata al bulk è minore della caduta nel silicio.

La concentrazione di elettroni all'interfaccia è determinata dalla posizione del livello di Fermi del Source. Nel caso in cui  $V_{Si} = V_{SB}$  La caduta di tensione tra Source e canale è nulla, quindi la banda di conduzione si trova, rispetto al livello di Fermi del Source, nella stessa condizione rispetto al bulk. La caduta di tensione nel silicio, cioè, equilibra la polarizzazione del Source rispetto al bulk. Quindi la concentrazione di elettroni nel canale è la stessa che nel silicio bulk.

$$n_S = n_{bulk} = \frac{n_i^2}{N_A} = 4.5 \times 10^4 \text{ cm}^{-3}$$

(3)

3) Se  $V_{GB}=10$  V avremo che  $V_{GS}=5$  V, e quindi  $V_{GS}>V_{TH}=0.63$  V. Quindi avremo che, per  $V_{DS}=0$ :

$$Q_n = C_{ox} (V_{GS} - V_{TH}) = 5.03 \times 10^{-3} \text{ C/m}^2$$

$Q_{tot} = LWQ_n = 2.51 \times 10^{-13} \text{ C}$

Per  $V_{DS}=5$  V il transistore è in saturazione poichè  $V_{DS}=V_{GS}>V_{GS}-V_{TH}$ . Avremo dunque:

$$Q_{tot} = \frac{2}{3} W L C_{ox} \left( V_{GS} - V_{TH} \right) = 1.67 \times 10^{-13} \text{ C}$$

(4)

## ESERCIZIO 3

Nel circuito in figura, il transistore M è n-MOS con  $V_{TH}=1$  V,  $t_{ox}=30$  nm, W/L=22,  $\mu_n=0.08$  m²/Vs. Q è un transistore bipolare  $n^+pn$ , ed è stato caratterizzato imponendo una  $I_B$  pari a 10  $\mu$  A e  $V_{CE}=5$  V. È stata misurata  $I_C=5$  mA e  $V_{CB}=4.5$  V.

- 1) Sapendo che  $N_{Abase}=10^{16}~{\rm cm^{-3}}$  e  $N_{Dcollettore}=10^{15}~{\rm cm^{-3}},~\mu_n=0.12~{\rm m^2/Vs},~\tau_n=1~\mu{\rm s},$  calcolare la lunghezza effettiva della base e il  $\beta_F$  minimo garantito. [3]

- 2) Determinare il punto di riposo dei transistori e la tensione di uscita.[4]

- 3) Determinare la tensione di collettore di Q per  $R_u \to \infty$ . Se  $R_u = 0$ , i transistori sono polarizzati? [3]

# SOLUZIONE 3

1) Dai dati della caratterizzazione ricaviamo subito  $\beta_F = I_C/I_B = 500$ . La larghezza effettiva di base, che è senz'altro inferiore alla larghezza metallurgica di base. Avremo:

$$D_n = V_T \mu_n = 3.108 \times 10^{-3} \text{ m}^2/\text{s}$$

$$\beta_F = \frac{\tau_n}{\tau_t}$$

$$\tau_t = \frac{W^2}{2D_n}$$

$$\beta_F = \frac{2\tau_n D_n}{W^2}$$

$$W = \sqrt{\frac{2\tau_n D_n}{\beta_f}} = \sqrt{\frac{2L_n^2}{\beta_f}} = 3.5 \ \mu\text{m}$$

Per calcolare il  $\beta_F$  minimo garantito, abbiamo bisogno della lunghezza metallurgica della base:

$$\begin{split} V_{0CB} &= V_T \ln \frac{N_{Abase} N_{Dcollettore}}{n_i^2} = 0.635 \\ W_{CB}(4.5 \text{ V}) &= 2.7 \ \mu\text{m} \\ X_{CB} &= W_{CB} \frac{N_D}{N_A + N_D} = 0.25 \ \mu\text{m} \\ W_{met} &= 3.5 + .25 = 3.75 \ \mu\text{m} \\ \beta_{F \ min} &= \frac{2\tau_n D_n}{W_{max}^2} = 442 \end{split}$$

2) Per il transistore bipolare abbiamo  $V_B=12\frac{R_3}{R_1+R_2+R_3}=4$  V,  $V_E=3.3$  V e quindi  $I_C\simeq I_E=V_E/R_E=1.57$  mA. Quindi avremo  $I_{Bmax}=I_C/\beta_{Fmin}=3.55~\mu$ A  $\frac{<< V_{CC}}{R_1+R_2+R_3=0.4}$  mA: il partitore pesante è verificato. Per il MOS dobbiamo impostare l'equazione  $(V_S=V_u=V_C)$ :

$$I_C + \frac{V_S}{R_u} = \frac{\mu_n C_{ox}}{2} \frac{W}{L} \left( V_G - V_{TH} - V_S \right)^2$$

(5)

che, risolta in  $V_S$ , da  $V_S=5.26$  V come valore accettabile ( $C_{ox}=1.15\times 10^{-3}$  F/m²). Quindi avremo  $V_U=V_S=5.26$  V,  $I_S=I_C+\frac{V_S}{R_u}=3.07$  mA. Avremo dunque  $V_{CE}=5.26-3.3=1.96$  V e  $V_{DS}=V_{CC}-V_S=6.74$  V  $>V_{GS}-V_{TH}=1.74$ . Quindi il bipolare è in zona attiva diretta, ed il MOS è in saturazione.

3) Se  $R_U \to \infty$   $I_S = I_C$ ,  $V_S = V_C$ , e quindi avremo:

$$1.57 \text{mA} = \frac{\mu_n C_{ox}}{2} \frac{W}{L} \left( V_G - V_{TH} - V_S \right)^2$$

(6)

da cui si ricava  $V_C = V_S = 5.75 \text{ V}.$

Se  $R_U = 0$ ,  $V_{CE} = 0$ , e quindi il transistore bipolare è in saturazione, ed il MOS rimane polarizzato in saturazione.