| LABORATORIO ELETTRONICA DIGITALE: | 01_09_B | Data:  | 26/05/2009 |

|-----------------------------------|---------|--------|------------|

| Nome_                             |         | Esito: |            |

| Tempo a disposizione: 1 ora       |         |        |            |

## **TEMA**

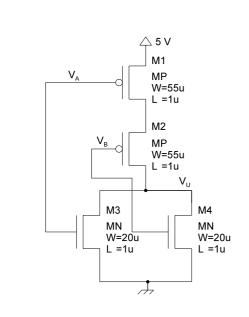

Si consideri la porta NOR CMOS realizzata in tecnologia "ED", il cui schema elettrico è riportato in figura. Si richiede di completare la scheda con i risultati ottenuti dalle opportune simulazioni effettuate. Si ritengano trascurabili, almeno in prima approssimazione, le capacità associate alle diffusioni di source e drain.

a. Analisi statica a vuoto: si consideri l'ingresso A, mantenendo l'ingresso B nello stato neutro per la porta.

| $V_{I\!L}$ |  |

|------------|--|

| $V_{IH}$   |  |

| $V_{OL}$   |  |

| $V_{OH}$   |  |

b. Analisi statica a carico: si considerino in ingresso i livelli elettrici pieni (0 e 5 V).

| $V_{OLmax}$ @ $IOL = 1 \text{ mA}$   |  |

|--------------------------------------|--|

| $V_{OHmin}$ @ $ IOH  = 1 \text{ mA}$ |  |

c. Analisi dinamica: si colleghi una capacità  $C_L = 0.6$  pF in uscita. Si faccia variare il segnale d'ingresso A tra 0 e 5 V con tempi di salita e discesa uguali e pari a 600 ps, mantenendo l'altro ingresso nello stato neutro per la porta. Valutare i tempi di propagazione  $t_{pHL}$ ,  $t_{pLH}$  e l'energia E fornita dall'alimentatore a seguito di una commutazione in discesa del segnale d'ingresso.

| $t_{pHL} (C_L = 0.6 \text{ pF})$ |  |

|----------------------------------|--|

| $t_{pLH} (C_L = 0.6 \text{ pF})$ |  |

| $E (C_L = 0.6 \text{ pF})$       |  |

d. Determinare la larghezza  $W_N$  dei transistori NMOS in modo tale che la tensione di uscita

$V_{OLmax}$  @ IOL = 1 mA sia pari a 0.4 V.

| $W_N$ |  |

|-------|--|

|       |  |